Welcome to E-XFL.COM

Microchip Technology - PIC32MX220F032CT-50I/TL Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | MIPS32® M4K <sup>™</sup>                                                          |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 23                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 12x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

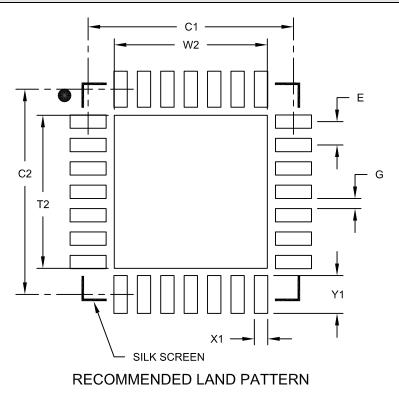

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 36-VTLA (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032ct-50i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

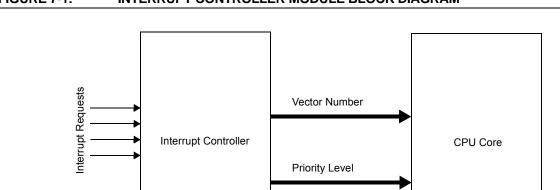

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

#### FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|-------------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                       | U-0                     | U-0              |  |  |  |  |  |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                           | _                       | —                |  |  |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                       | U-0                     | U-0              |  |  |  |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                         | —                       | —                |  |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                     | R/W-0                   | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | —                 | _                 |                   | _                 | _                 | SRIPL<2:0> <sup>(1)</sup> |                         |                  |  |  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0                   | R/W-0            |  |  |  |  |  |  |  |

| 7:0          | _                 | _                 |                   |                   | VEC               | <5:0> <sup>(1)</sup>      | VEC<5:0> <sup>(1)</sup> |                  |  |  |  |  |  |  |  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D''               | Dir              | Dit              |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 10.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7.0          |                   | IPTMR<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

# TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |        |       |       |       |        |       |      | Bi                   | ts      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|----------------------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8                 | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16         | —      | _     | —     | _     |        | _     | _    | _                    | _       |        | -      | _      | -      | —      | _      | _      | 0000       |

| 5170                        | DOITIOOIZ                       | 15:0          |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3180                        | DCH1DSIZ                        | 31:16         | _      | _     |       | —     | —      | —     | _    | -                    | —       | —      | _      |        | _      | —      | _      | —      | 0000       |

| 5100                        | DOITIDOIZ                       | 15:0          |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        |               |        |       |       |       |        |       |      | 0000                 |         |        |        |        |        |        |        |        |            |

| 0100                        |                                 | 1SPTR 15:0> 0 |        |       |       |       |        |       |      | 0000                 |         |        |        |        |        |        |        |        |            |

| 31A0                        | DCH1DPTR                        | 31:16         | —      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

| 017.00                      |                                 | 15:0          |        |       |       |       |        |       |      | CHDPT                | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16         | _      | _     | —     | —     | —      | —     | _    | _                    | —       | —      | _      | —      | —      | —      | —      | -      | 0000       |

| 0.20                        |                                 | 15:0          |        |       |       |       |        |       |      | CHCSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _      | _     | _     | —     | —      | —     | _    | _                    | —       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.00                        |                                 | 15:0          |        |       |       |       |        |       |      | CHCPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16         | —      | _     | —     | —     | —      | —     | —    | _                    | _       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.20                        |                                 | 15:0          | —      | _     | —     | —     | —      | —     | —    | _                    |         |        |        | CHPDA  |        |        |        |        | 0000       |

| 31F0                        | DCH2CON                         | 31:16         | —      | _     | —     | —     | —      | —     | —    | _                    |         | _      | —      | _      | _      | —      | —      |        | 0000       |

| 0.20                        |                                 |               | CHBUSY | _     | _     | —     | _      | _     |      | CHCHNS               | CHEN    | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | <1:0>  | 0000       |

| 31F0                        | DCH2ECON                        | 31:16         | _      | _     | —     | —     | —      | —     | _    | _                    |         |        |        | CHAIR  |        |        |        |        | 00FF       |

|                             |                                 | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |                      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      | —      | —      | FF00       |

| 3200                        | DCH2INT                         | 31:16         | —      | —     | —     | —     | —      | —     | _    | —                    | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0          | _      | _     |       | —     | —      | —     |      |                      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16         |        |       |       |       |        |       |      | CHSSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      |                      |         |        |        |        |        |        |        |        | 0000       |

| 3220                        |                                 | 31:16         |        |       |       |       |        |       |      | CHDSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | 1                    |         |        |        |        |        |        |        |        | 0000       |

| 3230                        | DCH2SSIZ                        | 31:16         |        | —     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3240                        | DCH2DSIZ                        | 31:16         |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      | —      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3250                        | DCH2SPTR                        | 31:16         |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHSPTI               | ≺<15:0> |        |        |        |        |        |        |        | 0000       |

| 3260                        | DCH2DPTR                        | 31:16         |        |       | —     | _     | —      | _     | _    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHDPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3270                        | DCH2CSIZ                        | 31:16         |        | _     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHCSI2<br>exadecimal |         |        |        |        |        |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 |                   | _                 | RDWR              | Γ                 | DMACH<2:0>       | >                |

#### REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

### REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                                                   |                    |  |  |

|-------------------|------------------|---------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                              | x = Bit is unknown |  |  |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| REGIOTE      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |  |  |

# REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

### **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

# TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |  |  |  |  |

|--------------|----------|-------------|---------------------------------------------|--|--|--|--|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |  |  |  |  |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |  |  |  |  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |  |  |  |  |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |  |  |  |  |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |  |  |  |  |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |  |  |  |  |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |  |  |  |  |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |  |  |  |  |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |  |  |  |  |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |  |  |  |  |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |  |  |  |  |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |  |  |  |  |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |  |  |  |  |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |  |  |  |  |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |  |  |  |  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |  |  |  |  |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |  |  |  |  |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |  |  |  |  |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |  |  |  |  |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |  |  |  |  |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |  |  |  |  |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |  |  |  |  |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |  |  |  |  |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |  |  |  |  |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |  |  |  |  |

#### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                       |           |       |       |       |       |       |       |      | Bi   | its  |      |      |      |              |      |       |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|--------------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3         | 18/2 | 17/1  | 16/0 | All Resets |

| FB00                        | RPA0R                 | 31:16     |       | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    | —            | —    | —     | —    | 0000       |

|                             |                       | 15:0      | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    |              | RPA0 | <3:0> |      | 0000       |

| FB04                        | RPA1R                 | 31:16     | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    | —            | —    | —     | —    | 0000       |

| 1 001                       |                       | 15:0      | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    |              | RPA1 | <3:0> |      | 0000       |

| FB08                        | RPA2R                 | 31:16     | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    | —            | —    | —     | —    | 0000       |

| 1 000                       | i (i / t <u>2</u> i ( | 15:0      | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    |              | RPA2 | <3:0> |      | 0000       |

| FB0C                        | RPA3R                 | 31:16     | _     | _     | —     | —     | _     | _     | _    | _    | _    | —    | _    | —    | _            | —    |       | —    | 0000       |

| T BOC                       |                       | 15:0      | _     |       | —     | _     | _     | _     | —    | _    | _    |      | —    | _    |              | RPA3 | <3:0> |      | 0000       |

| FB10                        | RPA4R                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _    | _            |      |       | —    | 0000       |

| T D IO                      |                       | 15:0      | —     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    |              | RPA4 | <3:0> |      | 0000       |

| FB20                        | RPA8R <sup>(1)</sup>  | 31:16     | —     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    | _            | —    | —     | —    | 0000       |

| 1 020                       |                       | 15:0      | _     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    |              | RPA8 | <3:0> |      | 0000       |

| FB24                        | RPA9R <sup>(1)</sup>  | 31:16     | —     | —     | —     | —     | -     |       | _    | -    |      | _    | _    | —    | -            | —    | _     | —    | 0000       |

| 1 D24                       | KFA9K /               | 15:0      | —     | —     | —     | —     | -     |       | _    | -    |      | _    | _    | —    |              | RPA9 | <3:0> |      | 0000       |

| FB2C                        | RPB0R                 | 31:16     | _     | _     | —     | —     | _     | -     | _    | _    | -    | —    | _    | —    | _            | _    | _     | —    | 0000       |

| 1 020                       | KF DUK                | 15:0      | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    |              | RPB0 | <3:0> |      | 0000       |

| FB30                        | RPB1R                 | 31:16     | —     | _     | —     | —     |       |       | —    |      |      | —    | —    | —    |              | _    | —     | —    | 0000       |

| FB30                        | REDIR                 | 15:0      | —     | _     | —     | —     |       |       | —    |      |      | —    | —    | —    |              | RPB1 | <3:0> |      | 0000       |

| FB34                        | RPB2R                 | 31:16     | _     | _     | _     | _     |       |       | _    |      |      | _    | _    | _    |              | _    | _     | —    | 0000       |

| FB34                        | RPBZR                 | 15:0      | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |              | RPB2 | <3:0> |      | 0000       |

| FB38                        | RPB3R                 | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —    | _            | _    | _     | _    | 0000       |

| FB30                        | RPBJR                 | 15:0      | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |              | RPB3 | <3:0> |      | 0000       |

| <b>FD2C</b>                 |                       | 31:16     | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    | —            | —    | —     | —    | 0000       |

| FB3C                        | RPB4R                 | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |              | RPB4 | <3:0> |      | 0000       |

| ED 40                       |                       | 31:16     |       |       | —     | —     | —     | -     | —    | —    | —    | —    | —    | —    | _            |      |       | —    | 0000       |

| FB40                        | RPB5R                 | 15:0      | _     |       | —     |       |       |       |      |      |      |      |      |      | RPB5<3:0> 00 |      |       |      |            |

| 5044                        |                       | 31:16     | _     | —     | _     | —     | —     | _     | _    | _    | _    | —    | _    | —    | _            | _    | _     | —    | 0000       |

| FB44                        | RPB6R <sup>(2)</sup>  | 15:0      | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    |              |      |       |      | 0000       |

| 50.40                       |                       | 31:16     | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    | _            | _    | _     | —    | 0000       |

| FB48                        | RPB7R                 | 15:0      | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    |              | RPB7 | <3:0> |      | 0000       |

DS60001168J-page 138

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: This register is only available on PIC32MX1XX devices.

3: This register is only available on 36-pin and 44-pin devices. PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# 24.1 Comparator Voltage Reference Control Register

| <b>TABLE 24-1</b> : | COMPARATOR VOLTAGE REFERENCE REGISTER MAP |

|---------------------|-------------------------------------------|

|---------------------|-------------------------------------------|

| ress<br>t)               |                                 | e         |       | Bits  |       |       |       |       |      |      |      |       |      |       |      | ŝ    |      |      |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                     | CVRCON                          | 31:16     | _     | _     | —     | —     | _     | —     | _    | _    | —    | —     | —    | _     | —    | _    | _    | —    | 0000       |

| 9800                     | CVRCON                          | 15:0      | ON    | _     | _     | _     | _     | _     | _    | _    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 25.1 CTMU Control Registers

### TABLE 25-1: CTMU REGISTER MAP

| ess                        |                                 | 6         |         |         |          |       |          |          |                                            | Bits     |         |         |      |       |          |      |      |      | ú          |

|----------------------------|---------------------------------|-----------|---------|---------|----------|-------|----------|----------|--------------------------------------------|----------|---------|---------|------|-------|----------|------|------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11    | 26/10    | 25/9                                       | 24/8     | 23/7    | 22/6    | 21/5 | 20/4  | 19/3     | 18/2 | 17/1 | 16/0 | All Reset: |

| A 200                      | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | SEL<3:0> |          | EDG2STAT                                   | EDG1STAT | EDG2MOD | EDG2POL |      | EDG2S | SEL<3:0> |      | —    | _    | 0000       |

| A200                       | CINUCON                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN    | EDGSEQEN | DGSEQEN IDISSEN CTTRIG ITRIM<5:0> IRNG<1:0 |          |         |         |      |       | <1:0>    | 0000 |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

NOTES:

# 26.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to <b>Section 10. "Power-</b><br><b>Saving Features"</b> (DS60001130), which<br>is available from the <i>Documentation</i> ><br><i>Reference Manual</i> section of the<br>Microchip PIC32 web site |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | (www.microchip.com/pic32).                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | (                                                                                                                                                                                                                                                                                                                                                                                                                                  |

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

# 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

# REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 **PWP<8:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

| DIT 18-10 | PWP<8:0>: Program Flash Write-Protect bits <sup>30</sup>                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------|

|           | Prevents selected program Flash memory pages from being modified during code execution.<br>11111111 = Disabled |

|           | 111111110 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111101 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111100 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111001 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111010 = Memory below 0x1000 (44) address is write-protected                                                |

|           | 111111001 = Memory below 0x1400 address is write-protected                                                     |

|           | 111111000 = Memory below 0x1000 address is write-protected                                                     |

|           | 111110111 = Memory below 0x2000 (8K) address is write-protected                                                |

|           | 111110110 = Memory below 0x2400 address is write-protected                                                     |

|           | 111110101 = Memory below 0x2800 address is write-protected                                                     |

|           | 111110100 = Memory below 0x2C00 address is write-protected                                                     |

|           | 111110011 = Memory below 0x3000 address is write-protected                                                     |

|           | 111110010 = Memory below 0x3400 address is write-protected                                                     |

|           | 111110001 = Memory below 0x3800 address is write-protected                                                     |

|           | 111110000 = Memory below 0x3C00 address is write-protected                                                     |

|           | 111101111 = Memory below 0x4000 (16K) address is write-protected                                               |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •<br>110111111 = Memory below 0x10000 (64K) address is write-protected                                         |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 101111111 = Memory below 0x20000 (128K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 011111111 = Memory below 0x40000 (256K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 00000000 = All possible memory is write-protected                                                              |

|           |                                                                                                                |

| bit 9-5   | Reserved: Write '1'                                                                                            |

| bit 4-3   | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits <sup>(2)</sup>                     |

|           | 11 = PGEC1/PGED1 pair is used                                                                                  |

|           | 10 = PGEC2/PGED2 pair is used                                                                                  |

|           | 01 = PGEC3/PGED3 pair is used                                                                                  |

|           | 00 = PGEC4/PGED4 pair is used <sup>(2)</sup>                                                                   |

| bit 2     | JTAGEN: JTAG Enable bit <sup>(1)</sup>                                                                         |

| bit 2     | 1 = JTAG is enabled                                                                                            |

|           | 0 = JTAG is disabled                                                                                           |

| bit 1-0   | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)           |

|           |                                                                                                                |

|           | 1x = Debugger is disabled                                                                                      |

|           | 0x = Debugger is enabled                                                                                       |

| Note 1:   | This bit sets the value for the JTAGEN bit in the CFGCON register.                                             |

|           | -                                                                                                              |

| 2:        | The PGEC4/PGED4 pin pair is not available on all devices. Refer to the " <b>Pin Diagrams</b> " section for     |

|           | availability.                                                                                                  |

| -         |                                                                                                                |

3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

| DC CHA        |        | STICS                                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                         |  |  |  |  |

|---------------|--------|-----------------------------------------------------------|------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol | Characteristics                                           | Min.                                                 | Typical | Max. | Units | Comments                                                                                |  |  |  |  |

| D300          | VIOFF  | Input Offset Voltage                                      | -                                                    | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |  |  |  |

| D301          | VICM   | Input Common Mode Voltage                                 | 0                                                    | -       | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |  |  |  |

| D302          | CMRR   | Common Mode Rejection Ratio                               | 55                                                   | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |  |  |  |

| D303A         | Tresp  | Large Signal Response Time                                | _                                                    | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |  |  |  |

| D303B         | TSRESP | Small Signal Response Time                                | -                                                    | 1       | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |  |  |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid                     | _                                                    | _       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |  |  |  |

| D305          | IVREF  | Internal Voltage Reference                                | 1.14                                                 | 1.2     | 1.26 | V     | _                                                                                       |  |  |  |  |

| D312          | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | _                                                    | —       | 10   | μs    | (Note 3)                                                                                |  |  |  |  |

#### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

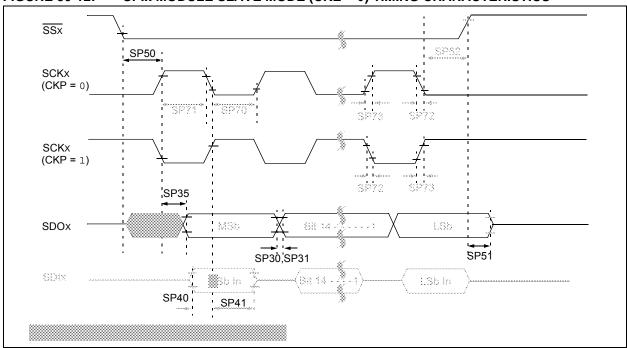

#### FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | TICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |      |       |                    |  |  |  |

|---------------|-----------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                                                                                               | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                       | TSCK/2                                                                                                                                                                                                                                                                             | —                   | _    | ns    | —                  |  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                      | TSCK/2                                                                                                                                                                                                                                                                             | —                   |      | ns    | —                  |  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                               | —                                                                                                                                                                                                                                                                                  | _                   |      | ns    | See parameter DO32 |  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                               | —                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                | —                                                                                                                                                                                                                                                                                  | —                   |      | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                | _                                                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                       | —                                                                                                                                                                                                                                                                                  | _                   | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2DoV              | SCKx Edge                                                          | —                                                                                                                                                                                                                                                                                  | —                   | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10                                                                                                                                                                                                                                                                                 |                     |      | ns    | —                  |  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                       | 10                                                                                                                                                                                                                                                                                 | _                   | _    | ns    | —                  |  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                                                                                                |                     |      | ns    | —                  |  |  |  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>             | 5                                                                                                                                                                                                                                                                                  | —                   | 25   | ns    | _                  |  |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20                                                                                                                                                                                                                                                                          | —                   |      | ns    | —                  |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

#### TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS          |                               | Standard Operatin<br>(unless otherwise<br>Operating tempera | <b>stated)</b><br>iture -40 | )°C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+105°C for V-temp |

|---------------|---------|-----------------|-------------------------------|-------------------------------------------------------------|-----------------------------|------------|--------------------------------------------------------|

| Param.<br>No. | Symbol  | Charact         | eristics                      | Min. <sup>(1)</sup>                                         | Max.                        | Units      | Conditions                                             |

| IM10          | TLO:SCL | Clock Low Time  | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μs         | —                                                      |

|               |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | —                                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | _                           | μs         | _                                                      |

| IM11          | THI:SCL | Clock High Time | 100 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μs         | —                                                      |

|               |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μs         | —                                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μs         | —                                                      |

| IM20          | TF:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 300                         | ns         | CB is specified to be                                  |

|               |         | Fall Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                         | ns         | from 10 to 400 pF                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 100                         | ns         |                                                        |

| IM21          | TR:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 1000                        | ns         | CB is specified to be                                  |

|               |         | Rise Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                         | ns         | from 10 to 400 pF                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 300                         | ns         |                                                        |

| IM25          | TSU:DAT | Data Input      | 100 kHz mode                  | 250                                                         | _                           | ns         | —                                                      |

|               |         | Setup Time      | 400 kHz mode                  | 100                                                         | —                           | ns         |                                                        |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | 100                                                         | _                           | ns         |                                                        |

| IM26          | THD:DAT | Data Input      | 100 kHz mode                  | 0                                                           | _                           | μS         | —                                                      |

|               |         | Hold Time       | 400 kHz mode                  | 0                                                           | 0.9                         | μs         |                                                        |

|               |         |                 | 1 MHz mode<br>(Note 2)        | 0                                                           | 0.3                         | μs         |                                                        |

| IM30          | TSU:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | Only relevant for                                      |

|               |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μS         | Repeated Start condition                               |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μs         | condition                                              |

| IM31          | THD:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μS         | After this period, the                                 |

|               |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μs         | first clock pulse is generated                         |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μS         | generaleu                                              |

| IM33          | Tsu:sto | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                             | μS         |                                                        |

|               |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             |                             | μs         |                                                        |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             |                             | μs         |                                                        |

| IM34          | THD:STO | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                             | ns         | —                                                      |

|               |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             |                             | ns         | ]                                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | ns         |                                                        |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

#### TABLE 30-34: ADC MODULE SPECIFICATIONS

|               |            |                                                      | (unless oth                       | erwise sta  | ted)                             |          | e 5): 2.5V to 3.6V                                                                                      |

|---------------|------------|------------------------------------------------------|-----------------------------------|-------------|----------------------------------|----------|---------------------------------------------------------------------------------------------------------|

|               |            |                                                      | Operating te                      | emperature  |                                  |          | C for Industrial<br>°C for V-temp                                                                       |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                              | Typical     | Max.                             | Units    | Conditions                                                                                              |

| Device        | Supply     |                                                      |                                   |             |                                  |          |                                                                                                         |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5 | —           | Lesser of<br>VDD + 0.3 or<br>3.6 | V        | _                                                                                                       |