Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 23                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 12x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

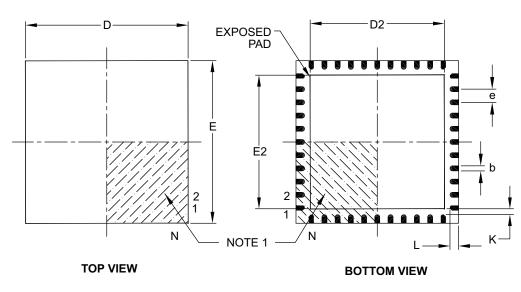

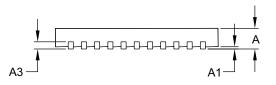

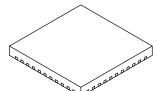

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032ct-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32  |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

# TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | IRQ | Vector |              | Interru        | pt Bit Location |              | Persistent |

|-------------------------------------|-----|--------|--------------|----------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>     | #   | #      | Flag         | Enable         | Priority        | Sub-priority | Interrupt  |

|                                     |     | Highes | st Natural C | order Priority | 1               |              | •          |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>      | IEC0<0>        | IPC0<4:2>       | IPC0<1:0>    | No         |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>      | IEC0<1>        | IPC0<12:10>     | IPC0<9:8>    | No         |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>      | IEC0<2>        | IPC0<20:18>     | IPC0<17:16>  | No         |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>      | IEC0<3>        | IPC0<28:26>     | IPC0<25:24>  | No         |

| T1 – Timer1                         | 4   | 4      | IFS0<4>      | IEC0<4>        | IPC1<4:2>       | IPC1<1:0>    | No         |

| IC1E – Input Capture 1 Error        | 5   | 5      | IFS0<5>      | IEC0<5>        | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>      | IEC0<6>        | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>      | IEC0<7>        | IPC1<20:18>     | IPC1<17:16>  | No         |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>      | IEC0<8>        | IPC1<28:26>     | IPC1<25:24>  | No         |

| T2 – Timer2                         | 9   | 8      | IFS0<9>      | IEC0<9>        | IPC2<4:2>       | IPC2<1:0>    | No         |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10>     | IEC0<10>       | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11>     | IEC0<11>       | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12>     | IEC0<12>       | IPC2<20:18>     | IPC2<17:16>  | No         |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13>     | IEC0<13>       | IPC2<28:26>     | IPC2<25:24>  | No         |

| T3 – Timer3                         | 14  | 12     | IFS0<14>     | IEC0<14>       | IPC3<4:2>       | IPC3<1:0>    | No         |

| IC3E – Input Capture 3              | 15  | 13     | IFS0<15>     | IEC0<15>       | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16>     | IEC0<16>       | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17>     | IEC0<17>       | IPC3<20:18>     | IPC3<17:16>  | No         |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18>     | IEC0<18>       | IPC3<28:26>     | IPC3<25:24>  | No         |

| T4 – Timer4                         | 19  | 16     | IFS0<19>     | IEC0<19>       | IPC4<4:2>       | IPC4<1:0>    | No         |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20>     | IEC0<20>       | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21>     | IEC0<21>       | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22>     | IEC0<22>       | IPC4<20:18>     | IPC4<17:16>  | No         |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23>     | IEC0<23>       | IPC4<28:26>     | IPC4<25:24>  | No         |

| T5 – Timer5                         | 24  | 20     | IFS0<24>     | IEC0<24>       | IPC5<4:2>       | IPC5<1:0>    | No         |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25>     | IEC0<25>       | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26>     | IEC0<26>       | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27>     | IEC0<27>       | IPC5<20:18>     | IPC5<17:16>  | No         |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28>     | IEC0<28>       | IPC5<28:26>     | IPC5<25:24>  | Yes        |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29>     | IEC0<29>       | IPC6<4:2>       | IPC6<1:0>    | No         |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30>     | IEC0<30>       | IPC6<12:10>     | IPC6<9:8>    | No         |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31>     | IEC0<31>       | IPC6<20:18>     | IPC6<17:16>  | No         |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>      | IEC1<0>        | IPC6<28:26>     | IPC6<25:24>  | No         |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>      | IEC1<1>        | IPC7<4:2>       | IPC7<1:0>    | No         |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>      | IEC1<2>        | IPC7<12:10>     | IPC7<9:8>    | No         |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>      | IEC1<3>        | IPC7<20:18>     | IPC7<17:16>  | Yes        |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>      | IEC1<4>        | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>      | IEC1<5>        | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>      | IEC1<6>        | IPC7<28:26>     | IPC7<25:24>  | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

# 7.1 Interrupt Control Registers

#### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                                 | â             |        |        |        |         |             |         |            | Bits    |        |          |          |          |                      |         |        |        |               |

|-----------------------------|---------------------------------|---------------|--------|--------|--------|---------|-------------|---------|------------|---------|--------|----------|----------|----------|----------------------|---------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14  | 29/13  | 28/12   | 27/11       | 26/10   | 25/9       | 24/8    | 23/7   | 22/6     | 21/5     | 20/4     | 19/3                 | 18/2    | 17/1   | 16/0   | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _      | _      | —      | _       |             |         | _          | -       |        |          | _        | _        |                      | —       |        |        | 0000          |

| 1000                        | INTCOM                          | 15:0          | —      | _      | —      | MVEC    | -           |         | TPC<2:0>   |         | -      | —        | _        | INT4EP   | INT3EP               | INT2EP  | INT1EP | INT0EP | 0000          |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —      |        | —      | _       | _           | _       | —          | —       |        | _        | _        | _        |                      |         | —      | —      | 0000          |

| 1010                        | INTOTAL                         | 15:0          | —      | _      | —      | —       | _           |         | SRIPL<2:0> |         | _      | _        |          |          | VEC<5:0              | )>      |        |        | 0000          |

| 1020                        | IPTMR                           | 31:16<br>15:0 |        |        |        |         |             |         |            | IPTMR<3 | 1:0>   |          |          |          |                      |         |        |        | 0000          |

| 4000                        | 1500                            | 31:16         | FCEIF  | RTCCIF | FSCMIF | AD1IF   | OC5IF       | IC5IF   | IC5EIF     | T5IF    | INT4IF | OC4IF    | IC4IF    | IC4EIF   | T4IF                 | INT3IF  | OC3IF  | IC3IF  | 0000          |

| 1030                        | IFS0                            | 15:0          | IC3EIF | T3IF   | INT2IF | OC2IF   | IC2IF       | IC2EIF  | T2IF       | INT1IF  | OC1IF  | IC1IF    | IC1EIF   | T1IF     | INT0IF               | CS1IF   | CS0IF  | CTIF   | 0000          |

| 1010                        | 1504                            | 31:16         | DMA3IF | DMA2IF | DMA1IF | DMA0IF  | CTMUIF      | I2C2MIF | I2C2SIF    | I2C2BIF | U2TXIF | U2RXIF   | U2EIF    | SPI2TXIF | SPI2RXIF             | SPI2EIF | PMPEIF | PMPIF  | 0000          |

| 1040                        | IFS1                            | 15:0          | CNCIF  | CNBIF  | CNAIF  | I2C1MIF | I2C1SIF     | I2C1BIF | U1TXIF     | U1RXIF  | U1EIF  | SPI1TXIF | SPI1RXIF | SPI1EIF  | USBIF <sup>(2)</sup> | CMP3IF  | CMP2IF | CMP1IF | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE  | RTCCIE | FSCMIE | AD1IE   | OC5IE       | IC5IE   | IC5EIE     | T5IE    | INT4IE | OC4IE    | IC4IE    | IC4EIE   | T4IE                 | INT3IE  | OC3IE  | IC3IE  | 0000          |

| 1060                        | IECU                            | 15:0          | IC3EIE | T3IE   | INT2IE | OC2IE   | IC2IE       | IC2EIE  | T2IE       | INT1IE  | OC1IE  | IC1IE    | IC1EIE   | T1IE     | INT0IE               | CS1IE   | CS0IE  | CTIE   | 0000          |

| 1070                        | IEC1                            | 31:16         | DMA3IE | DMA2IE | DMA1IE | DMA0IE  | CTMUIE      | I2C2MIE | I2C2SIE    | I2C2BIE | U2TXIE | U2RXIE   | U2EIE    | SPI2TXIE | SPI2RXIE             | SPI2EIE | PMPEIE | PMPIE  | 0000          |

| 1070                        | ILC I                           | 15:0          | CNCIE  | CNBIE  | CNAIE  | I2C1MIE | I2C1SIE     | I2C1BIE | U1TXIE     | U1RXIE  | U1EIE  | SPI1TXIE | SPI1RXIE | SPI1EIE  | USBIE <sup>(2)</sup> | CMP3IE  | CMP2IE | CMP1IE | 0000          |

| 1090                        | IPC0                            | 31:16         | —      | _      | —      |         | INT0IP<2:0> |         | INTOIS     | <1:0>   | -      | —        | _        | С        | S1IP<2:0>            |         | CS1IS  | S<1:0> | 0000          |

| 1030                        | 11 00                           | 15:0          | —      | —      | —      |         | CS0IP<2:0>  |         | CS0IS      | <1:0>   | _      | —        | —        | (        | CTIP<2:0>            |         | CTIS   | <1:0>  | 0000          |

| 10A0                        | IPC1                            | 31:16         | —      |        | —      |         | INT1IP<2:0> |         | INT1IS     | <1:0>   | _      | —        | _        | 0        | C1IP<2:0>            |         | OC1IS  | S<1:0> | 0000          |

| 10,10                       |                                 | 15:0          | —      | —      | —      |         | IC1IP<2:0>  |         | IC1IS•     | <1:0>   | —      | —        | —        | ٦        | Γ1IP<2:0>            |         | T1IS   | <1:0>  | 0000          |

| 10B0                        | IPC2                            | 31:16         | _      | —      | —      |         | INT2IP<2:0> |         | INT2IS     | <1:0>   | _      | —        | _        | 0        | C2IP<2:0>            |         | OC2IS  | 6<1:0> | 0000          |

| 1000                        | 11 02                           | 15:0          | —      |        | —      |         | IC2IP<2:0>  |         | IC2IS<     | <1:0>   | _      | —        | _        | 1        | [21P<2:0>            |         | T2IS   | <1:0>  | 0000          |

| 10C0                        | IPC3                            | 31:16         | —      | —      | —      |         | INT3IP<2:0> |         | INT3IS     | <1:0>   | —      |          | —        | 0        | C3IP<2:0>            |         | OC3IS  | 6<1:0> | 0000          |

| 1000                        | 1 00                            | 15:0          | —      | —      | —      |         | IC3IP<2:0>  |         | IC3IS<     | <1:0>   | —      |          | —        |          | [3IP<2:0>            |         | T3IS-  |        | 0000          |

| 10D0                        | IPC4                            | 31:16         | —      |        | —      |         | INT4IP<2:0> |         | INT4IS     | <1:0>   | _      | —        | _        | 0        | C4IP<2:0>            |         | OC4IS  | S<1:0> | 0000          |

| 1020                        |                                 | 15:0          | —      | —      | —      |         | IC4IP<2:0>  |         | IC4IS<     | <1:0>   |        | —        | _        | 1        | [4IP<2:0>            |         | T4IS   | <1:0>  | 0000          |

| 10E0                        | IPC5                            | 31:16         | —      | —      | —      |         | AD1IP<2:0>  |         | AD1IS      | -       | _      | —        | _        | 0        | C5IP<2:0>            |         | OC5IS  | 6<1:0> | 0000          |

| 1020                        |                                 | 15:0          | —      | _      | —      |         | IC5IP<2:0>  |         | IC5IS<     |         | -      | —        | —        |          | [5]P<2:0>            |         | T5IS   |        | 0000          |

| 10F0                        | IPC6                            | 31:16         | —      | —      | —      |         | CMP1IP<2:0> |         | CMP1IS     |         |        | _        | —        | F        | CEIP<2:0>            |         | FCEIS  | 6<1:0> | 0000          |

| 101 0                       | " 00                            | 15:0          | —      | —      | —      | F       | RTCCIP<2:0> |         | RTCCIS     | 6<1:0>  | —      | —        | _        | FS       | CMIP<2:0>            | >       | FSCMI  | S<1:0> | 0000          |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

# REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| INE OIOT     | LK 10-J.          |                   |                   |                   |                        |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   | —                 | _                      | _                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

# REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

# Legend:

| zogonai           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

# **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

|              |                   |                   |                   |                   |                   |                   |                  | ., _, _,         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | _                | _                |

# **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | —                  |                   | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | —                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

#### REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

- 111 = Reserved; do not use

- 110 = Reserved; do not use

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

- 1 = REFCLK is used by the Baud Rate Generator

- 0 = PBCLK is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

# 21.1 RTCC Control Registers

### TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | ē         |        |       |          |          |       |       |                   |      | Bits     |          |           |         |         |         |            |       | ŝ          |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|----------|-------|-------|-------------------|------|----------|----------|-----------|---------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12    | 27/11 | 26/10 | 25/9              | 24/8 | 23/7     | 22/6     | 21/5      | 20/4    | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | —      | _     | —        | —        | —     | —     |                   |      |          |          | CAL<      | <9:0>   |         |         |            |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL     | —        | —     | —     |                   | —    | RTSECSEL | RTCCLKON | —         |         | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | —      |       |          | —        | —     | _     |                   | —    | —        | _        | —         |         | _       | —       | _          | —     | 0000       |

| 0210                        | RICALIN                         | 15:0      | ALRMEN | CHIME | PIV      | ALRMSYNC |       | AMASI | <b>&lt;</b> <3:0> |      |          |          |           | ARPT    | <7:0>   |         |            |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     | —      | _     | HR1      | 0<1:0>   |       | HR01  | <3:0>             |      | —        | М        | IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0220                        |                                 | 15:0      | —      |       | SEC10<2: | 0>       |       | SEC07 | 1<3:0>            |      | —        | —        | —         | -       | _       | _       | —          | —     | xx00       |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0>  |          |       | YEAR0 | 1<3:0>            |      | —        | —        | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | xxxx       |

| 0230                        | RICDAIL                         | 15:0      | _      | _     | DAY      | 10<1:0>  |       | DAY01 | 1<3:0>            |      | —        | —        | —         |         | _       | W       | /DAY01<2:0 | >     | xx00       |

| 0240                        | ALRMTIME                        | 31:16     | _      |       | HR1      | 0<1:0>   |       | HR01  | <3:0>             |      | _        | М        | IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                 | 15:0      | —      |       | SEC10<2: | 0>       |       | SEC02 | 1<3:0>            |      | —        | _        | —         |         | _       | —       | _          | —     | xx00       |

| 0250                        | ALRMDATE                        | 31:16     | _      | _     | _        | _        | _     | _     |                   | _    | —        | _        | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | 00xx       |

| 0250                        | ALNIUATE                        | 15:0      |        | DAY1  | 0<3:0>   |          |       | DAY01 | <3:0>             |      | _        | _        | _         | -       | _       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read

If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit<br>24/16/8/0 | Bit<br>25/17/9/1 | Bit<br>26/18/10/2 | Bit<br>27/19/11/3 | Bit<br>28/20/12/4 | Bit<br>29/21/13/5 | Bit<br>30/22/14/6 | Bit<br>31/23/15/7 | Bit<br>Range |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------|

| Image: How provided with the system         HR10<1:0>         HR01<3:0>           23:16         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           23:16         —         MIN10<2:0>         MIN01<3:0>         MIN01<3:0>           15:8         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           15:8         —         SEC10<2:0>         SEC01<3:0>         SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | 04.04        |

| 23:16         —         MIN10<2:0>         MIN01<3:0>           15:8         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           15:8         —         SEC10<2:0>         SEC01<3:0>         SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  | <3:0>            | HR01              |                   | <1:0>             | HR10              | —                 | _                 | 31:24        |

| U-0         R/W-x         R | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | 00.40        |

| 15:8 — SEC10<2:0> SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | <3:0>            | MIN01             |                   |                   | MIN10<2:0>        |                   | _                 | 23:16        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | 45.0         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  | <3:0>            | SEC01             |                   |                   | SEC10<2:0>        |                   | _                 | 15:8         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0              | U-0              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | 7.0          |

| 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                |                  | _                 | _                 | _                 | _                 | _                 | _                 | 7:0          |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | —                 | —                 | _                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | —                 | _                 | MONTH10           |                   | MONTH             | 01<3:0>          |                  |  |  |

| 45.0         | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | _                 | DAY1              | 0<1:0>            |                   | DAY01             | <3:0>            |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | —                 | _                 | _                 | _                 | —                 | V                 | VDAY01<2:0       | >                |  |  |

# REGISTER 21-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Legena:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 Unimplemented: Read as '0'

bit 20 MONTH10: Binary Coded Decimal value of months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary Coded Decimal value of days bits, 10s place digit; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 Unimplemented: Read as '0'

bit 2-0 WDAY01<2:0>: Binary Coded Decimal value of weekdays bits; contains a value from 0 to 6

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | _                 |                   | —                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |  |  |

### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

# Legend:

| Logena.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan

0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | _                 | —                 |                   | —                 | _                 |                   | -                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | —                 |                   | —                 | _                 | _                 | _                | —                |  |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | -                 | —                 | SIDL              | —                 | _                 | _                 |                  | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   |                   | _                 | C3OUT             | C2OUT            | C10UT            |  |  |

### REGISTER 23-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-14 Unimplemented: Read as '0'

#### bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

#### bit 12-3 Unimplemented: Read as '0'

#### bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

#### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

# REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 **PWP<8:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

| DIT 18-10 | PWP<8:0>: Program Flash Write-Protect bits <sup>30</sup>                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------|

|           | Prevents selected program Flash memory pages from being modified during code execution.<br>11111111 = Disabled |

|           | 111111110 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111101 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111100 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111001 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111010 = Memory below 0x1000 (44) address is write-protected                                                |

|           | 111111001 = Memory below 0x1400 address is write-protected                                                     |

|           | 111111000 = Memory below 0x1000 address is write-protected                                                     |

|           | 111110111 = Memory below 0x2000 (8K) address is write-protected                                                |

|           | 111110110 = Memory below 0x2400 address is write-protected                                                     |

|           | 111110101 = Memory below 0x2800 address is write-protected                                                     |

|           | 111110100 = Memory below 0x2C00 address is write-protected                                                     |

|           | 111110011 = Memory below 0x3000 address is write-protected                                                     |

|           | 111110010 = Memory below 0x3400 address is write-protected                                                     |

|           | 111110001 = Memory below 0x3800 address is write-protected                                                     |

|           | 111110000 = Memory below 0x3C00 address is write-protected                                                     |

|           | 111101111 = Memory below 0x4000 (16K) address is write-protected                                               |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •<br>110111111 = Memory below 0x10000 (64K) address is write-protected                                         |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 101111111 = Memory below 0x20000 (128K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 011111111 = Memory below 0x40000 (256K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 00000000 = All possible memory is write-protected                                                              |

|           |                                                                                                                |

| bit 9-5   | Reserved: Write '1'                                                                                            |

| bit 4-3   | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits <sup>(2)</sup>                     |

|           | 11 = PGEC1/PGED1 pair is used                                                                                  |

|           | 10 = PGEC2/PGED2 pair is used                                                                                  |

|           | 01 = PGEC3/PGED3 pair is used                                                                                  |

|           | 00 = PGEC4/PGED4 pair is used <sup>(2)</sup>                                                                   |

| bit 2     | JTAGEN: JTAG Enable bit <sup>(1)</sup>                                                                         |

| bit 2     | 1 = JTAG is enabled                                                                                            |

|           | 0 = JTAG is disabled                                                                                           |

| bit 1-0   | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)           |

|           |                                                                                                                |

|           | 1x = Debugger is disabled                                                                                      |

|           | 0x = Debugger is enabled                                                                                       |

| Note 1:   | This bit sets the value for the JTAGEN bit in the CFGCON register.                                             |

|           | -                                                                                                              |

| 2:        | The PGEC4/PGED4 pin pair is not available on all devices. Refer to the " <b>Pin Diagrams</b> " section for     |

|           | availability.                                                                                                  |

| -         |                                                                                                                |

3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |  |

| 31:24        | —                 | _                 | _                 | _                 | —                 | —                 | FWDTWI           | NSZ<1:0>         |  |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | _                 | WDTPS<4:0>        |                   |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | V<1:0>            | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO              | _                 | FSOSCEN           | _                 | —                 | F                 | NOSC<2:0>        |                  |  |

#### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit P = Programmable bit |                                         |  |  |

|-------------------|---------------------------------------|-----------------------------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0'      |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared x = Bit is unknown |  |  |

#### bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

#### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

#### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

#### bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 <b>= 1:1048576</b>                                     |

|--------------------------------------------------------------|

| 10011 <b>= 1:524288</b>                                      |

| 10010 <b>= 1:262144</b>                                      |

| 10001 <b>= 1:131072</b>                                      |

| 10000 <b>= 1:65536</b>                                       |

| 01111 <b>= 1:32768</b>                                       |

| 01110 <b>= 1:16384</b>                                       |

| 01101 = 1:8192                                               |

| 01100 = 1:4096                                               |

| 01011 = <b>1:2048</b>                                        |

| 01010 = 1:1024                                               |

| 01001 = 1:512                                                |

| 01000 <b>= 1:256</b>                                         |

| 00111 <b>= 1:128</b>                                         |

| 00110 <b>= 1:64</b>                                          |

| 00101 <b>= 1:32</b>                                          |

| 00100 <b>= 1:16</b>                                          |

| 00011 <b>= 1:8</b>                                           |

| 00010 <b>= 1</b> :4                                          |

| 00001 = 1:2                                                  |

| 00000 = 1:1                                                  |

| All other combinations not shown result in operation = 10100 |

| ······································                       |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

# REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

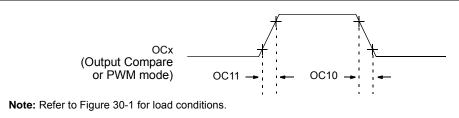

# FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

# TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | (unless | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |                    |  |  |

|--------------------|--------|--------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.    | Typical <sup>(2)</sup>                                                                                                                                                                             | Max. | Units | Conditions         |  |  |

| OC10               | TccF   | OCx Output Fall Time           | —       | —                                                                                                                                                                                                  | _    | ns    | See parameter DO32 |  |  |

| OC11               | TccR   | OCx Output Rise Time           | —       | —                                                                                                                                                                                                  |      | ns    | See parameter DO31 |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

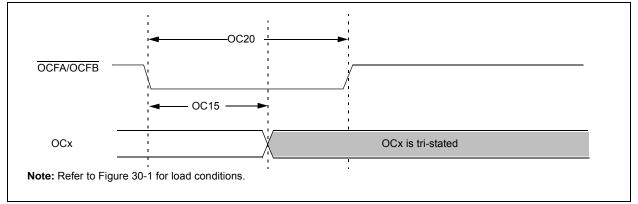

### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

# TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

|              |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |     |                        |     |       |            |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|-----|-------|------------|

| Param<br>No. | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                        | Min | Typical <sup>(2)</sup> | Max | Units | Conditions |