Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032d-50i-tl |

#### TABLE 11: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

44-PIN TQFP (TOP VIEW)(1,2,3,5)

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

1

| Pin # | Full Pin Name                                  |

|-------|------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       |

| 2     | RPC6/PMA1/RC6                                  |

| 3     | RPC7/PMA0/RC7                                  |

| 4     | RPC8/PMA5/RC8                                  |

| 5     | RPC9/CTED7/PMA6/RC9                            |

| 6     | Vss                                            |

| 7     | VCAP                                           |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          |

| 10    | AN12/PMD0/RB12                                 |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 16    | AVss                                           |

| 17    | AVDD                                           |

| 18    | MCLR                                           |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

| Pin # | Full Pin Name                        |

|-------|--------------------------------------|

| 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 25    | AN6/RPC0/RC0                         |

| 26    | AN7/RPC1/RC1                         |

| 27    | AN8/RPC2/PMA2/RC2                    |

| 28    | VDD                                  |

| 29    | Vss                                  |

| 30    | OSC1/CLKI/RPA2/RA2                   |

| 31    | OSC2/CLKO/RPA3/RA3                   |

| 32    | TDO/RPA8/PMA8/RA8                    |

| 33    | SOSCI/RPB4/RB4                       |

| 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 35    | TDI/RPA9/PMA9/RA9                    |

| 36    | RPC3/RC3                             |

| 37    | RPC4/PMA4/RC4                        |

| 38    | RPC5/PMA3/RC5                        |

| 39    | Vss                                  |

| 40    | VDD                                  |

| 41    | PGED3/RPB5/PMD7/RB5                  |

| 42    | PGEC3/RPB6/PMD6/RB6                  |

| 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- 5: Shaded pins are 5V tolerant.

### **Table of Contents**

| 1.0   | Device Overview                                    | 19  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs.   |     |

| 3.0   | CPU.                                               |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Flash Program Memory                               |     |

| 6.0   | Resets                                             |     |

| 7.0   | Interrupt Controller                               |     |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 83  |

| 10.0  | USB On-The-Go (OTG)                                | 103 |

| 11.0  | I/O Ports                                          | 127 |

| 12.0  | Timer1                                             | 143 |

| 13.0  | Timer2/3, Timer4/5                                 | 147 |

| 14.0  | Watchdog Timer (WDT)                               | 153 |

| 15.0  | Input Capture                                      | 157 |

|       | Output Compare                                     |     |

| 17.0  | Serial Peripheral Interface (SPI)                  | 165 |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 181 |

|       | Parallel Master Port (PMP)                         |     |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 209 |

| 23.0  | Comparator                                         |     |

| 24.0  | Comparator Voltage Reference (CVREF)               | 223 |

| 25.0  | Charge Time Measurement Unit (CTMU)                | 227 |

| 26.0  | Power-Saving Features                              | 233 |

| 27.0  | Special Features                                   | 239 |

| 28.0  | Instruction Set                                    |     |

| 29.0  | Development Support                                | 253 |

|       | Electrical Characteristics                         |     |

|       | 50 MHz Electrical Characteristics                  |     |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

|       | Aicrochip Web Site                                 |     |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Produ | uct Identification System                          | 342 |

#### Referenced Sources

This device data sheet is based on the following individual chapters of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the following documents, refer to the *Documentation > Reference Manuals* section of the Microchip PIC32 website: http://www.microchip.com/pic32

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

#### REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | -                 | _                 | -                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | ı                 | ı                 | _                 | ı                 | -                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 |                   |                   | RDWR              |                   | OMACH<2:0>       | •                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-4 **Unimplemented:** Read as '0' bit 3 **RDWR:** Read/Write Status bit

1 = Last DMA bus access was a read0 = Last DMA bus access was a write

bit 2-0 DMACH<2:0>: DMA Channel bits

These bits contain the value of the most recent active DMA channel.

### REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

#### REGISTER 10-16: U1SOF: USB SOF THRESHOLD REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | -                 | -                 | 1                 | -                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | -                 | -                 | -                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

Typical values of the threshold are:

01001010 **= 64-byte packet**

00101010 = 32-byte packet

00011010 = **16-byte packet**

00010010 = 8-byte packet

### REGISTER 10-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | -                 | -                 | -                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          |                   |                   | В                 | DTPTRL<15:        | )>                |                   |                  | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: Buffer Descriptor Table Base Address bits

This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

TABLE 11-4: PORTB REGISTER MAP

| ess                         |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

| 6100                        | ANSELB           | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | ANOLLD           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | _             | _             | _            | _            | -            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0110                        | TITIOD           | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            |              |              |              |              |              | 0000       |

| 0120                        | TOKID            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | LAND             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| 6140                        | ODCB             | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        | CNPUB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0130                        | CINFUB           | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                        |                  | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | CINFUB           | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                        | CNCONB           | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0170                        | CINCOIND         | 15:0      | ON            | _             | SIDL          | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 6180                        | CNENB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | CINEIND          | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6 <sup>(2)</sup>       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | _             | _             | -             | _                            | _             | -             | -            | _            | ı            | _                           | _            | -            | -            | -            | _            | _            | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

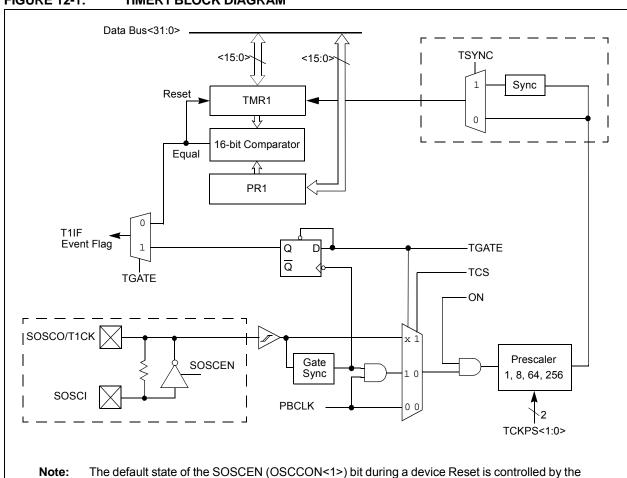

### 12.0 TIMER1

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "**Timers**" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

The following modes are supported:

- · Synchronous Internal Timer

- · Synchronous Internal Gated Timer

- Synchronous External Timer

- · Asynchronous External Timer

### 12.1 Additional Supported Features

- · Selectable clock prescaler

- · Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

**Note:** The default state of the SOSCEN (OSCCON<1>) bit during a device Reset is controlled by the FSOSCEN bit in Configuration Word, DEVCFG1.

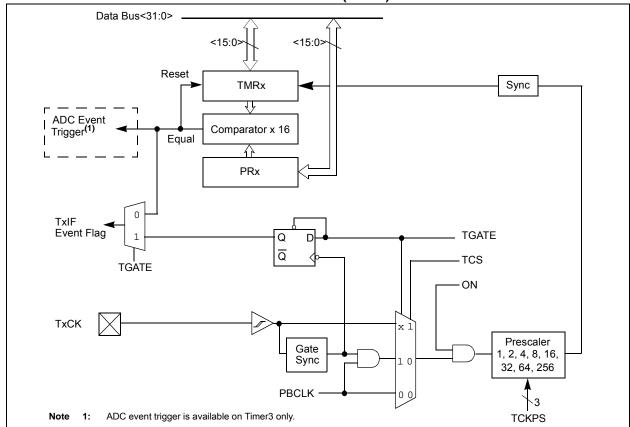

### 13.0 TIMER2/3, TIMER4/5

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "Timers" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- · Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

Note:

In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through Timer5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or Timer4 and 'y' represents Timer3 or Timer5.

### 13.1 Additional Supported Features

- · Selectable clock prescaler

- · Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

#### FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send a NACK during an Acknowledge sequence

- 0 = Send an ACK during an Acknowledge sequence

- bit 4 **ACKEN:** Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        | _                 | — HR10<1:0> HR01<3:0> |                   |                   |                   |                   |                  |                  |  |

| 22.40        | U-0               | R/W-x                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        | _                 |                       | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | _                 |                       | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                     | _                 | _                 | _                 |                   |                  | _                |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                   | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                   | _                 | _                 | -                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | _                 | _                 | _                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 | _                 | CCH              | <1:0>            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

1 = Module is enabled. Setting this bit does not affect the other bits in this register

0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

bit 14 **COE:** Comparator Output Enable bit

1 = Comparator output is driven on the output CxOUT pin

0 = Comparator output is not driven on the output CxOUT pin

bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

1 = Output is inverted

0 = Output is not inverted

bit 12-9 Unimplemented: Read as '0'

bit 8 **COUT:** Comparator Output bit

1 = Output of the Comparator is a '1'

0 = Output of the Comparator is a '0'

bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

00 = Comparator interrupt generation is disabled

bit 5 Unimplemented: Read as '0'

bit 4 CREF: Comparator Positive Input Configure bit

1 = Comparator non-inverting input is connected to the internal CVREF

0 = Comparator non-inverting input is connected to the CxINA pin

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

11 = Comparator inverting input is connected to the IVREF

10 = Comparator inverting input is connected to the CxIND pin

01 = Comparator inverting input is connected to the CxINC pin

00 = Comparator inverting input is connected to the CxINB pin

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

| 1XX/2X | X 28/36/ | 44-PIN         | FAMIL'               | <u> </u>                    |                             |

|--------|----------|----------------|----------------------|-----------------------------|-----------------------------|

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          |                |                      |                             |                             |

|        |          | 1XX/2XX 28/36/ | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMILY | 1XX/2XX 28/36/44-PIN FAMILY |

### 27.0 SPECIAL FEATURES

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and "Programming and Diagnostics" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- · Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming™ (ICSP™)

### 27.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 27-6) provides device and revision information.

#### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2  | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|------------------|------------------|--|

| 24.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1                | R/P              | R/P              |  |

| 31:24        |                   | _                 | _                 |                   |                   | _                  | FWDTWINSZ<1:0>   |                  |  |

| 22.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P                | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | _                 | WDTPS<4:0>        |                   |                    |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P                | R/P              | R/P              |  |

| 15:8         | FCKSM<1:0>        |                   | FPBDIV<1:0>       |                   | _                 | OSCIOFNC POSCMOD<1 |                  | OD<1:0>          |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P                | R/P              | R/P              |  |

| 7:0          | IESO              | _                 | FSOSCEN           |                   | _                 | F                  | NOSC<2:0>        |                  |  |

Legend: r = Reserved bit P = Programmable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

11 = Window size is 25%

10 = Window size is 37.5%

01 = Window size is 50%

00 = Window size is 75%

bit 23 **FWDTEN:** Watchdog Timer Enable bit

1 = Watchdog Timer is enabled and cannot be disabled by software

0 = Watchdog Timer is not enabled; it can be enabled in software

WINDIS: Watchdog Timer Window Enable bit bit 22

1 = Watchdog Timer is in non-Window mode

0 = Watchdog Timer is in Window mode

bit 21 Reserved: Write '1'

bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

10100 = 1:1048576

10011 = 1:524288

10010 = 1:262144

10001 = 1:131072

10000 = 1:65536

01111 = 1:32768

01110 = 1:16384

01101 = 1:8192

01100 = 1:4096

01011 = 1:2048

01010 = 1:1024

01001 = 1:512

01000 = 1:256

00111 = 1:128 00110 = 1:64

00101 = 1:32

00100 = 1:16

00011 = 1:8

00010 = 1:4

00001 = 1:2 00000 = 1:1

All other combinations not shown result in operation = 10100

Note 1: Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

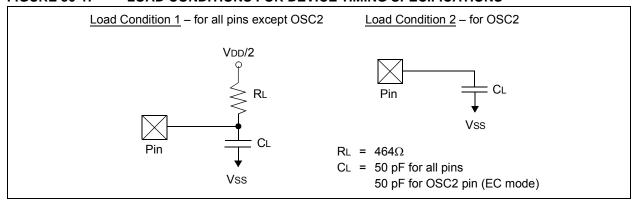

## 30.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX1XX/2XX 28/36/44-pin Family AC characteristics and timing parameters.

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| .,                 |        |                       |                                                                                                                                                                                                                                                |                        |      |       |                          |  |  |  |

|--------------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------------|--|--|--|

| AC CHARACTERISTICS |        |                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |                          |  |  |  |

| Param.<br>No.      | Symbol | Characteristics       | Min.                                                                                                                                                                                                                                           | Typical <sup>(1)</sup> | Max. | Units | Conditions               |  |  |  |

| DO56               | Сю     | All I/O pins and OSC2 |                                                                                                                                                                                                                                                | _                      | 50   | pF    | EC mode                  |  |  |  |

| DO58               | Св     | SCLx, SDAx            | _                                                                                                                                                                                                                                              | _                      | 400  | pF    | In I <sup>2</sup> C mode |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

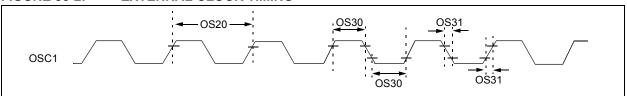

### FIGURE 30-2: EXTERNAL CLOCK TIMING

### **TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS**

AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$  for V-temp

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                      | Min.  | Typical | Max.  | Units | Conditions                           |

|---------------|--------|---------------------------------------------------------------------|-------|---------|-------|-------|--------------------------------------|

| OS50          | FPLLI  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51          | Fsys   | On-Chip VCO System Frequency                                        | 60    | _       | 120   | MHz   | _                                    |

| OS52          | TLOCK  | PLL Start-up Time (Lock Time)                                       | _     | _       | 2     | ms    | _                                    |

| OS53          | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      | -0.25 | _       | +0.25 | %     | Measured over 100 ms period          |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

### **TABLE 30-19: INTERNAL FRC ACCURACY**

| AC CHA        | RACTERISTICS                                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +105^{\circ}\text{C}$ for V-temp |         |      |          |            |  |  |  |

|---------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------|------------|--|--|--|

| Param.<br>No. | Characteristics                                 | Min.                                                                                                                                                                                                                                               | Typical | Max. | Units    | Conditions |  |  |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                    |         |      |          |            |  |  |  |

| F20b          | FRC                                             | -0.9                                                                                                                                                                                                                                               | _       | +0.9 | <u> </u> |            |  |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### **TABLE 30-20: INTERNAL LPRC ACCURACY**

| AC CHA        | RACTERISTICS                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                         |  |  |            |  |  |

|---------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|------------|--|--|

| Param.<br>No. | Characteristics                 | Min.                                                                                                                                                                                                                                           | Min. Typical Max. Units |  |  | Conditions |  |  |

| LPRC @        | LPRC @ 31.25 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                |                         |  |  |            |  |  |

| F21           | LPRC                            | -15                                                                                                                                                                                                                                            | -15 — +15 % —           |  |  |            |  |  |

Note 1: Change of LPRC frequency as VDD changes.

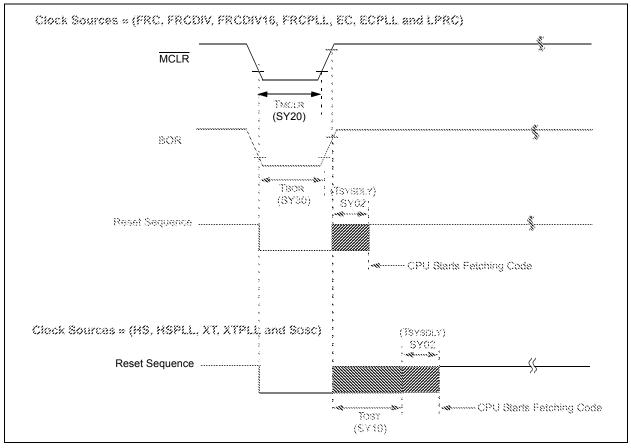

FIGURE 30-5: EXTERNAL RESET TIMING CHARACTERISTICS

**TABLE 30-22: RESETS TIMING**

| AC CHARACTERISTICS |         |                                                                                                                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                              |     |    |   |  |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|----|---|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                                                                                 | Min. Typical <sup>(2)</sup> Max. Units Conditions                                                                                                                                                                                              |                              |     |    |   |  |

| SY00               | Tpu     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                          | _                                                                                                                                                                                                                                              | 400                          | 600 | μS | _ |  |

| SY02               | Tsysdly | System Delay Period: Time Required to Reload Device Configuration Fuses plus SYSCLK Delay before First instruction is Fetched. | _                                                                                                                                                                                                                                              | 1 μs +<br>8 SYSCLK<br>cycles | _   | _  | _ |  |

| SY20               | TMCLR   | MCLR Pulse Width (low)                                                                                                         | 2                                                                                                                                                                                                                                              | _                            | _   | μS | _ |  |

| SY30               | TBOR    | BOR Pulse Width (low)                                                                                                          | _                                                                                                                                                                                                                                              | 1                            | _   | μS | _ |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

SP60 <del>✓→</del> SSx **SCKx** (CKP = 0)sėtz SP73 SCKx (CKP = 1)MSb Bit 14 -LSb SDOx SP30,SP31 SP51 SDIx MSb In Bit 14 LSb In SP40

**FIGURE 30-13:** SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 30-31: SPIx MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | AC CHARACTERISTICS    |                                            |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |            |    |                    |  |  |

|---------------|-----------------------|--------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.   | Typical <sup>(2)</sup>                                                                                                                                                                                                                         | Conditions |    |                    |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)               | Tsck/2 | _                                                                                                                                                                                                                                              | _          | ns | _                  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)              | Tsck/2 | _                                                                                                                                                                                                                                              | _          | ns | _                  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                       | _      | 5                                                                                                                                                                                                                                              | 10         | ns | _                  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                       | _      | 5                                                                                                                                                                                                                                              | 10         | ns | _                  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)        | _      |                                                                                                                                                                                                                                                | _          | ns | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)        | _      | _                                                                                                                                                                                                                                              | _          | ns | See parameter DO31 |  |  |

| SP35          | TscH2DoV,             | SDOx Data Output Valid after<br>SCKx Edge  | _      | _                                                                                                                                                                                                                                              | 20         | ns | VDD > 2.7V         |  |  |

|               | TscL2DoV              |                                            | _      | _                                                                                                                                                                                                                                              | 30         | ns | VDD < 2.7V         |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10     | _                                                                                                                                                                                                                                              | _          | ns | _                  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10     | _                                                                                                                                                                                                                                              | _          | ns | _                  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or SCKx ↑ Input            | 175    | _                                                                                                                                                                                                                                              | _          | ns | _                  |  |  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- Assumes 50 pF load on all SPIx pins.

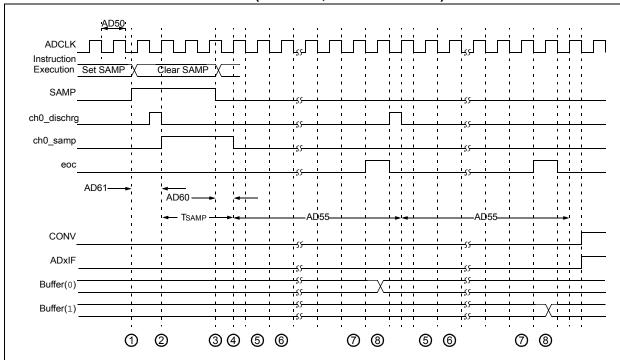

FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

- 1 Software sets ADxCON. SAMP to start sampling.

- ② Sampling starts after discharge period. TSAMP is described in Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual".

- (3) Software clears ADxCON. SAMP to start conversion.

- 4 Sampling ends, conversion sequence starts.

- 6 Convert bit 9.

- 6 Convert bit 8.

- 7 Convert bit 0.

- (8) One TAD for end of conversion.

### **INDEX**

| Numerics                                        |     | Core Exception Types                                                  |     |

|-------------------------------------------------|-----|-----------------------------------------------------------------------|-----|

| 50 MHz Electrical Characteristics               | 301 | EJTAG Debug Support                                                   |     |

| A                                               |     | Power Management                                                      |     |

| Α                                               |     | CPU Module                                                            |     |

| AC Characteristics                              |     | Customer Change Notification Service<br>Customer Notification Service |     |

| 10-Bit Conversion Rate Parameters               |     | Customer Support                                                      |     |

| ADC Specifications                              |     | Customer Support                                                      | 34  |

| Analog-to-Digital Conversion Requirements       |     | D                                                                     |     |

| EJTAG Timing Requirements                       |     | DC and AC Characteristics                                             |     |

| Internal FRC Accuracy                           |     | Graphs and Tables                                                     | 30. |

| Internal RC Accuracy                            |     | DC Characteristics                                                    |     |

| OTG Electrical Specifications                   |     | I/O Pin Input Specifications                                          |     |

| Parallel Master Port Read Requirements          |     | I/O Pin Output Specifications                                         | ,   |

| Parallel Master Port Write                      |     | Idle Current (IDLE)                                                   |     |

| Parallel Master Port Write Requirements         |     | Power-Down Current (IPD)                                              |     |

| Parallel Slave Port Requirements                |     | Program Memory                                                        |     |

| PLL Clock Timing                                |     | Temperature and Voltage Specifications                                |     |

| Analog-to-Digital Converter (ADC)               | 209 | DC Characteristics (50 MHz)                                           |     |

| Assembler                                       |     | Idle Current (IDLE)                                                   |     |

| MPASM Assembler                                 | 254 | Power-Down Current (IPD)                                              |     |

| В                                               |     | Development Support                                                   |     |

|                                                 |     | · · · · · · · · · · · · · · · · · · · ·                               |     |

| Block Diagrams                                  |     | Direct Memory Access (DMA) Controller                                 | 0   |

| ADC Module                                      |     | E                                                                     |     |

| Comparator I/O Operating Modes                  |     | Electrical Characteristics                                            | 25  |

| Comparator Voltage Reference                    |     | AC                                                                    |     |

| Connections for On-Chip Voltage Regulator       |     | Errata                                                                |     |

| Core and Peripheral Modules                     | 19  | External Clock                                                        |     |

| CPU                                             | 33  | Timer1 Timing Requirements                                            | 27/ |

| CTMU Configurations                             |     | Timer 7 Timing Requirements Timer2, 3, 4, 5 Timing Requirements       |     |

| Time Measurement                                | 227 | Timing Requirements                                                   |     |

| DMA                                             | 83  | External Clock (50 MHz)                                               | 27  |

| I2C Circuit                                     | 174 | Timing Requirements                                                   | 30/ |

| Input Capture                                   | 157 | Tilling Requirements                                                  |     |

| Interrupt Controller                            |     | F                                                                     |     |

| JTAG Programming, Debugging and Trace Ports     | 250 | Flash Program Memory                                                  | 51  |

| Output Compare Module                           |     | RTSP Operation                                                        | 5   |

| PMP Pinout and Connections to External Devices. |     | Teror operation                                                       |     |

| Reset System                                    | 59  | l                                                                     |     |

| RTCC                                            |     | I/O Ports                                                             | 127 |

| SPI Module                                      | 165 | Parallel I/O (PIO)                                                    |     |

| Timer1                                          |     | Write/Read Timing                                                     |     |

| Timer2/3/4/5 (16-Bit)                           |     | Input Change Notification                                             |     |

| Typical Multiplexed Port Structure              | 127 | Instruction Set                                                       |     |

| UART                                            | 181 | Inter-Integrated Circuit (I2C                                         |     |

| WDT and Power-up Timer                          | 153 | Internal Voltage Reference Specifications                             |     |

| Brown-out Reset (BOR)                           |     | Internet Address                                                      |     |

| and On-Chip Voltage Regulator                   | 250 | Interrupt Controller                                                  |     |

| C                                               |     | IRG, Vector and Bit Location                                          |     |

|                                                 |     |                                                                       |     |

| C Compilers                                     |     | M                                                                     |     |

| MPLAB C18                                       | 254 | Memory Maps                                                           |     |

| Charge Time Measurement Unit. See CTMU.         |     | PIC32MX110/210 Devices                                                |     |

| Clock Diagram                                   | 74  | (4 KB RAM, 16 KB Flash)                                               | 38  |

| Comparator                                      |     | PIC32MX120/220 Devices                                                |     |

| Specifications267                               |     | (8 KB RAM, 32 KB Flash)                                               | 39  |

| Comparator Module                               |     | PIC32MX130/230                                                        |     |

| Comparator Voltage Reference (CVref             |     | (16 KB RAM, 256 KB Flash)                                             | 43  |

| Configuration Bit                               |     | PIC32MX130/230 Devices                                                |     |

| Configuring Analog Port Pins                    | 128 | (16 KB RAM, 64 KB Flash)                                              | 40  |

| CPU                                             |     | PIC32MX150/250 Devices                                                |     |

| Architecture Overview                           |     | (32 KB RAM, 128 KB Flash)                                             | 4   |

| Coprocessor 0 Registers                         | 35  | PIC32MX170/270                                                        |     |

|                                                 |     | · · · · · · · · · · · · · · · · · · ·                                 |     |