Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| )etails                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| roduct Status             | Active                                                                         |

| Core Processor            | MIPS32® M4K™                                                                   |

| Core Size                 | 32-Bit Single-Core                                                             |

| peed                      | 40MHz                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| lumber of I/O             | 33                                                                             |

| rogram Memory Size        | 32KB (32K x 8)                                                                 |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 8K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 13x10b                                                                     |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 85°C (TA)                                                              |

| lounting Type             | Surface Mount                                                                  |

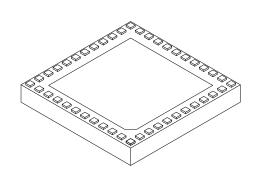

| ackage / Case             | 44-VQFN Exposed Pad                                                            |

| upplier Device Package    | 44-QFN (8x8)                                                                   |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032d-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 14: PIN NAMES FOR 44-PIN USB DEVICES

44-PIN VTLA (TOP VIEW)(1,2,3,5)

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

| Pin # | Full Pin Name                                    |

|-------|--------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         |

| 2     | RPC6/PMA1/RC6                                    |

| 3     | RPC7/PMA0/RC7                                    |

| 4     | RPC8/PMA5/RC8                                    |

| 5     | RPC9/CTED7/PMA6/RC9                              |

| 6     | Vss                                              |

| 7     | VCAP                                             |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       |

| 9     | PGEC2/RPB11/D-/RB11                              |

| 10    | Vusb3v3                                          |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 16    | AVss                                             |

| 17    | AVDD                                             |

| 18    | MCLR                                             |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 23   | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 24   | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 25   | AN6/RPC0/RC0                              |

| 26   | AN7/RPC1/RC1                              |

| 27   | AN8/RPC2/PMA2/RC2                         |

| 28   | VDD                                       |

| 29   | Vss                                       |

| 30   | OSC1/CLKI/RPA2/RA2                        |

| 31   | OSC2/CLKO/RPA3/RA3                        |

| 32   | TDO/RPA8/PMA8/RA8                         |

| 33   | SOSCI/RPB4/RB4                            |

| 34   | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 35   | TDI/RPA9/PMA9/RA9                         |

| 36   | AN12/RPC3/RC3                             |

| 37   | RPC4/PMA4/RC4                             |

| 38   | RPC5/PMA3/RC5                             |

| 39   | Vss                                       |

| 40   | VDD                                       |

| 41   | RPB5/USBID/RB5                            |

| 42   | VBUS                                      |

| 43   | RPB7/CTED3/PMD5/INT0/RB7                  |

| 44   | RPB8/SCL1/CTED10/PMD4/RB8                 |

#### Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

- 5: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup> | •                               |             |                |                                                                         |

|----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>   | 41(3)                           | ı           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                | 2                                 | 33                  | 19                              | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                | 3                                 | 34                  | 20                              | I           | ST             | 1                                                                       |

| CTED3    | 13                | 16                                | 17                  | 43                              | I           | ST             | 1                                                                       |

| CTED4    | 15                | 18                                | 19                  | 1                               | I           | ST             | 1                                                                       |

| CTED5    | 22                | 25                                | 28                  | 14                              | I           | ST             | 1                                                                       |

| CTED6    | 23                | 26                                | 29                  | 15                              | I           | ST             | 1                                                                       |

| CTED7    | _                 | _                                 | 20                  | 5                               | I           | ST             | 1                                                                       |

| CTED8    | _                 | _                                 | -                   | 13                              | I           | ST             | 1                                                                       |

| CTED9    | 9                 | 12                                | 10                  | 34                              | I           | ST             | 1                                                                       |

| CTED10   | 14                | 17                                | 18                  | 44                              | I           | ST             | 1                                                                       |

| CTED11   | 18                | 21                                | 24                  | 8                               | I           | ST             | 1                                                                       |

| CTED12   | 2                 | 5                                 | 36                  | 22                              | I           | ST             | 1                                                                       |

| CTED13   | 3                 | 6                                 | 1                   | 23                              | I           | ST             | 1                                                                       |

| CTPLS    | 21                | 24                                | 27                  | 11                              | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |

| PGEC1    | 2                 | 5                                 | 36                  | 22                              | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                | 21                                | 24                  | 8                               | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |

| PGEC2    | 19                | 22                                | 25                  | 9                               | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>   | 41 <sup>(2)</sup>               | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)               | 19 <sup>(3)</sup>               | 1/0         | 31             | Communication Channel 3                                                 |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               |             | ST             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>   | 20 <sup>(3)</sup>               | 1 '         | 31             | Debugging Communication Channel 3                                       |

| PGED4    | _                 | _                                 | 3                   | 12                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |

| PGEC4    | _                 | _                                 | 4                   | 13                              | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

**3:** Pin number for PIC32MX2XX devices only.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44-pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note:

The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within onequarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 µF to 0.001 µF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 µF in parallel with 0.001 µF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | ddress          |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| Watchdog Timer            |            | 0x0000          |

| RTCC                      |            | 0x0200          |

| Timer1-5                  |            | 0x0600          |

| Input Capture 1-5         |            | 0x2000          |

| Output Compare 1-5        |            | 0x3000          |

| IC1 and IC2               |            | 0x5000          |

| SPI1 and SPI2             |            | 0x5800          |

| UART1 and UART2           |            | 0x6000          |

| PMP                       |            | 0x7000          |

| ADC                       | 0xBF80     | 0x9000          |

| CVREF                     |            | 0x9800          |

| Comparator                |            | 0xA000          |

| CTMU                      |            | 0xA200          |

| Oscillator                |            | 0xF000          |

| Device and Revision ID    |            | 0xF220          |

| Peripheral Module Disable |            | 0xF240          |

| Flash Controller          |            | 0xF400          |

| Reset                     |            | 0xF600          |

| PPS                       |            | 0xFA04          |

| Interrupts                |            | 0x1000          |

| Bus Matrix                |            | 0x2000          |

| DMA                       | 0xBF88     | 0x3000          |

| USB                       |            | 0x5050          |

| PORTA-PORTC               |            | 0x6000          |

| Configuration             | 0xBFC0     | 0x0BF0          |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |       |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------|-------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0   | U-0   | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | _                 | _                 | _     | _     | _                 | _                 | _                | _                |  |  |  |  |  |  |

| 22.40        | U-0               | U-0               | U-0   | U-0   | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | _                 | _                 | _     | _     | _                 | _                 | _                | _                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         |                   | BMXDUDBA<15:8>    |       |       |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0   | R-0   | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |       | BMXDU | DBA<7:0>          |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits

This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| PIC32MX1XX | /2XX 28/3 | 86/44-PIN | FAMILY |  |

|------------|-----------|-----------|--------|--|

| NOTES:     |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

|            |           |           |        |  |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

Note: This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit

definitions.

### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0 R/W-0 R/W-0 R/W |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            |                  |

| 31:24        | IEC31             | IEC30                 | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22                 | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | IEC15             | IEC14                 | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06                 | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

REGISTER 9-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | _                 | _                 | _                 | _                 | -                 | _                | _                     |

| 23:16        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23.10        | _                   | _                 | _                 | _                 | _                 | -                 | _                | _                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | _                 | _                 | ı                 | _                 | ı                 |                  | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 CHBUSY: Channel Busy bit

1 = Channel is active or has been enabled

0 = Channel is inactive or has been disabled

bit 14-9 Unimplemented: Read as '0'

bit 8 **CHCHNS**: Chain Channel Selection bit<sup>(1)</sup>

1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

bit 7 CHEN: Channel Enable bit(2)

1 = Channel is enabled

0 = Channel is disabled

bit 6 CHAED: Channel Allow Events If Disabled bit

1 = Channel start/abort events will be registered, even if the channel is disabled

0 = Channel start/abort events will be ignored if the channel is disabled

bit CHCHN: Channel Chain Enable bit

1 = Allow channel to be chained

0 = Do not allow channel to be chained

bit 4 CHAEN: Channel Automatic Enable bit

1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

bit 3 Unimplemented: Read as '0'

bit 2 CHEDET: Channel Event Detected bit

1 = An event has been detected

0 = No events have been detected

bit 1-0 CHPRI<1:0>: Channel Priority bits

11 = Channel has priority 3 (highest)

10 = Channel has priority 2

01 = Channel has priority 1

00 = Channel has priority 0

Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

TABLE 11-4: PORTB REGISTER MAP

| ess                         |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

| 6100                        | ANSELB           | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | ANOLLD           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | _             | _             | _            | _            | -            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0110                        | TITIOD           | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            |              |              |              |              |              | 0000       |

| 0120                        | TOKID            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | LAND             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| 6140                        | ODCB             | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        | CNPUB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0130                        | CINFUB           | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                        |                  | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | CINFUB           | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                        | CNCONB           | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0170                        | CINCOIND         | 15:0      | ON            | _             | SIDL          | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 6180                        | CNENB            | 31:16     | _             | _             | _             | _                            | _             | _             | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | CINEIND          | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6 <sup>(2)</sup>       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | _             | _             | -             | _                            | _             | -             | -            | _            | ı            | _                           | _            | -            | -            | -            | _            | _            | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

### 17.1 SPI Control Registers

### TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

|                             | LE 17-1                         |           |               | J SPIZ P | ·      | - 1 \ 1417 \ \               |                                                                  |              |          |        |         |        |        |        |             |          |        |        |            |

|-----------------------------|---------------------------------|-----------|---------------|----------|--------|------------------------------|------------------------------------------------------------------|--------------|----------|--------|---------|--------|--------|--------|-------------|----------|--------|--------|------------|

| ess                         |                                 | 4         |               |          |        |                              |                                                                  |              |          | Bit    | ts      |        |        |        |             |          |        |        |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14    | 29/13  | 28/12                        | 27/11                                                            | 26/10        | 25/9     | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0   | All Resets |

| 5900                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC  | FRMPOL | MSSEN                        | FRMSYPW                                                          | FF           | RMCNT<2: | )>     | MCLKSEL | _      |        | 1      | _           | 1        | SPIFE  | ENHBUF | 0000       |

| 3000                        | SFITCON                         | 15:0      | ON            | _        | SIDL   | DISSDO MODE32 MODE16 SMP CKE |                                                                  |              |          |        | SSEN    | CKP    | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | L<1:0> | 0000       |

| E010                        | SPI1STAT                        | 31:16     | _             | _        | _      |                              | RXE                                                              | BUFELM<4:    | 0>       |        | _       | _      | 1      |        | TXI         | BUFELM<4 | :0>    |        | 0000       |

| 5610                        | SFIISIKI                        | 15:0      | _             | _        | _      | FRMERR                       | RMERR SPIBUSY SPITUR SRMT SPIROV SPIRBE - SPITBE - SPITBF SPIRBF |              |          |        |         |        |        |        | 8000        |          |        |        |            |

| 5820                        | SPI1BUF                         | 31:16     |               |          |        |                              |                                                                  |              |          | DATA<  | 31.0>   |        |        |        |             |          |        |        | 0000       |

| 3620                        | 51 11001                        | 15:0      |               |          |        |                              |                                                                  |              |          | DAIA   | 31.0    |        |        |        |             |          |        |        | 0000       |

| 5830                        | SPI1BRG                         | 31:16     |               | _        | _      |                              |                                                                  |              |          |        |         |        | _      | _      | 0000        |          |        |        |            |

| 3030                        | oi Tibico                       | 15:0      |               | _        | _      | BRG<12:0>                    |                                                                  |              |          |        |         |        |        |        | 0000        |          |        |        |            |

|                             |                                 | 31:16     | _             | _        | _      | _                            | _                                                                | _            | _        | _      | _       | _      | _      | _      | _           | _        | _      | _      | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | _        | _      | FRM<br>ERREN                 | SPI<br>ROVEN                                                     | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _      | _      | _      | AUD<br>MONO | _        | AUDMO  | D<1:0> | 0000       |

| E A OO                      | SDI3CON                         | 31:16     | FRMEN         | FRMSYNC  | FRMPOL | MSSEN                        | FRMSYPW                                                          | FF           | RMCNT<2: | )>     | MCLKSEL | _      | -      | _      | _           | _        | SPIFE  | ENHBUF | 0000       |

| 5A00                        | SPI2CON                         | 15:0      | ON            | _        | SIDL   | DISSDO                       | MODE32                                                           | MODE16       | SMP      | CKE    | SSEN    | CKP    | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | L<1:0> | 0000       |

| E A 40                      | SPI2STAT                        | 31:16     | _             | _        | _      |                              | RXE                                                              | BUFELM<4:    | 0>       |        | _       | _      | 1      |        | TXI         | BUFELM<4 | :0>    |        | 0000       |

| 5A10                        | SPIZSTAT                        | 15:0      | _             | _        | _      | FRMERR                       | SPIBUSY                                                          | -            | _        | SPITUR | SRMT    | SPIROV | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF | 8000       |

| E A 20                      | SPI2BUF                         | 31:16     |               |          |        |                              |                                                                  |              |          | DATA<  | 21:05   |        |        |        |             |          |        |        | 0000       |

| 5A20                        | SFIZEOI                         | 15:0      |               |          |        |                              |                                                                  |              |          | DAIA   | 31.0    |        |        |        |             |          |        |        | 0000       |

| E A 20                      | SPI2BRG                         | 31:16     | _             | _        | _      | -                            | _                                                                | -            | _        | _      | _       | _      | _      | _      | _           | _        | _      | _      | 0000       |

| 5A30                        | OI IZDINO                       | 15:0      |               | _        | _      | BRG<12:0> 00                 |                                                                  |              |          |        |         |        |        | 0000   |             |          |        |        |            |

|                             |                                 | 31:16     |               | _        | _      | _                            | _                                                                | _            | _        | _      | _       | _      | _      | _      | _           | _        | _      | _      | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | _        | -      | FRM<br>ERREN                 | SPI<br>ROVEN                                                     | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _      | _      | 1      | AUD<br>MONO | 1        | AUDMO  | D<1:0> | 0000       |

egend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

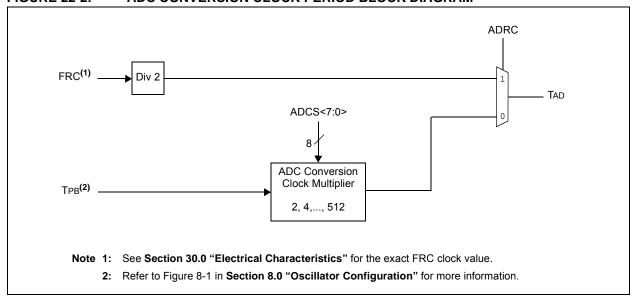

### FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

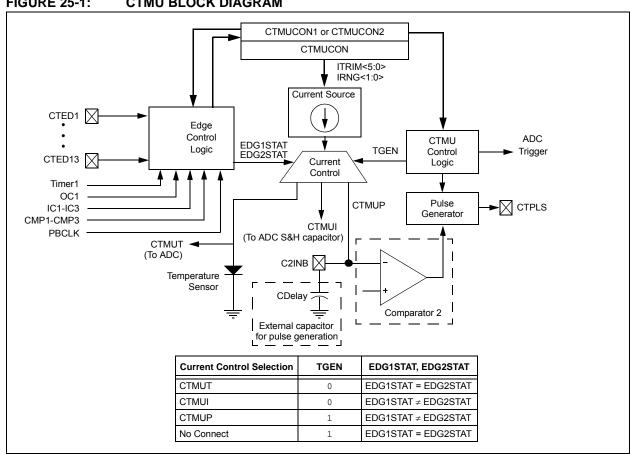

#### **CHARGE TIME** 25.0 **MEASUREMENT UNIT (CTMU)**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The CTMU module includes the following key features:

- · Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- · 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- · Control of edge sequence

- · Control of response to edges

- High precision time measurement

- · Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

TABLE 30-9: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                     |                     |       |                                                                                                                              |

|--------------------|--------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                       | Min.                                                                                                                                                                                                                                           | Typ. <sup>(1)</sup> | Max.                | Units | Conditions                                                                                                                   |

| DI60a              | licl   | Input Low Injection<br>Current                                        | 0                                                                                                                                                                                                                                              | _                   | <sub>-5</sub> (2,5) | mA    | This parameter applies to all pins, with the exception of the power pins.                                                    |

| DI60b              | lich   | Input High Injection<br>Current                                       | 0                                                                                                                                                                                                                                              | _                   | +5(3,4,5)           | mA    | This parameter applies to all pins, with the exception of all 5V tolerant pins, and the SOSCI, SOSCO, OSC1, D+, and D- pins. |

| DI60c              | ∑lict  | Total Input Injection<br>Current (sum of all I/O<br>and Control pins) | <sub>-20</sub> (6)                                                                                                                                                                                                                             |                     | +20(6)              | mA    | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \sum$ IICT )  |

- **Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: VIL source < (Vss 0.3). Characterized but not tested.

- 3: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **4:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 5: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., ViH Source > (VDD + 0.3) or ViL source < (Vss 0.3)).

- 6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If **Note 2**, IICL = (((Vss 0.3) VIL source) / Rs). If **Note 3**, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

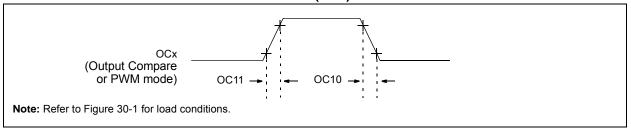

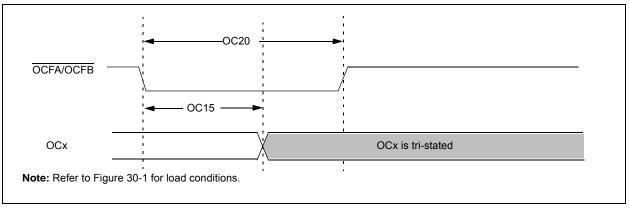

### FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |                        |      |       |                    |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                  | Min. | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time                                                                                                                                                                                                                            | _    | _                      |      | ns    | See parameter DO32 |

| OC11               | TccR   | OCx Output Rise Time                                                                                                                                                                                                                            |      | _                      | _    | ns    | See parameter DO31 |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |     |                        |     |       |            |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|-----|-------|------------|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                 | Min | Typical <sup>(2)</sup> | Max | Units | Conditions |

| OC15               | TFD    | Fault Input to PWM I/O Change                                                                                                                                                                                                                  | _   | _                      | 50  | ns    | _          |

| OC20               | TFLT   | Fault Input Pulse Width                                                                                                                                                                                                                        | 50  | _                      | _   | ns    | _          |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |         |          |       |                               |

|--------------------|--------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|-------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                                    | Min.                                                                                                                           | Typical | Max.     | Units | Conditions                    |

| MOS10              |        | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4                                                                                                                        |         | 50<br>50 |       | EC (Note 2)<br>ECPLL (Note 1) |

**Note 1:** PLL input requirements: 4 MHz ≤ FPLLIN ≤ 5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

### TABLE 31-6: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |        |         |      |       |            |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                        | Min.   | Typical | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time (Note 1,2)                                                                                                                                        | Tsck/2 |         | _    | ns    | -          |

| MSP11              | TscH   | SCKx Output High Time (Note 1,2)                                                                                                                                       | Tsck/2 | _       | _    | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

### TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

|                    | TABLE OF 7. OF IX MODULE MAGTER MODE (ORE = 1) TIMING REQUIREMENTS |                                                                                                                                                                          |        |      |      |       |            |

|--------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|------------|

| AC CHARACTERISTICS |                                                                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial |        |      |      |       |            |

| Param.<br>No.      | Symbol                                                             | Characteristics <sup>(1)</sup>                                                                                                                                           | Min.   | Тур. | Max. | Units | Conditions |

| MSP10              | TscL                                                               | SCKx Output Low Time (Note 1,2)                                                                                                                                          | Tsck/2 | _    | _    | ns    | _          |

| MSP11              | TscH                                                               | SCKx Output High Time (Note 1,2)                                                                                                                                         | Tsck/2 |      |      | ns    | _          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> This parameter is characterized, but not tested in manufacturing.

**<sup>2:</sup>** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

**<sup>2:</sup>** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

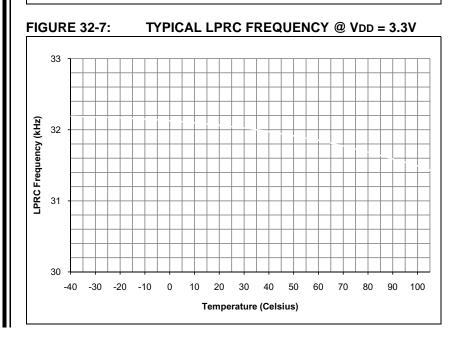

-40 -30

-20 -10 0 10

### **FIGURE 32-6:** TYPICAL FRC FREQUENCY @ VDD = 3.3V 8000 7990 7980 7970 FRC Frequency (kHz) 7960 7950 7940 7930 7920 7910

20 30 40 50

Temperature (Celsius)

60 70 80

90 100

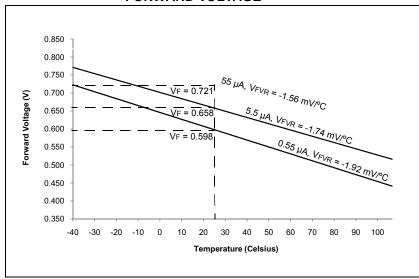

**FIGURE 32-8:** TYPICAL CTMU TEMPERATURE DIODE **FORWARD VOLTAGE**

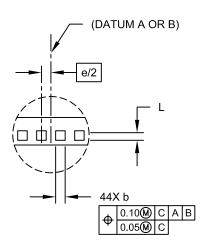

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**DETAIL A**

|                         | N      | ILLIMETER | S        |       |

|-------------------------|--------|-----------|----------|-------|

| Dimension               | Limits | MIN       | NOM      | MAX   |

| Number of Pins          | Ν      |           | 44       |       |

| Number of Pins per Side | ND     |           | 12       |       |

| Number of Pins per Side | NE     |           | 10       |       |

| Pitch                   | е      |           | 0.50 BSC |       |

| Overall Height          | Α      | 0.80      | 0.90     | 1.00  |

| Standoff                | A1     | 0.025     | -        | 0.075 |

| Overall Width           | Е      |           | 6.00 BSC |       |

| Exposed Pad Width       | E2     | 4.40      | 4.55     | 4.70  |

| Overall Length          | D      |           | 6.00 BSC |       |

| Exposed Pad Length      | D2     | 4.40      | 4.55     | 4.70  |

| Contact Width           | b      | 0.20      | 0.25     | 0.30  |

| Contact Length          | L      | 0.20      | 0.25     | 0.30  |

| Contact-to-Exposed Pad  | K      | 0.20      | -        | -     |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section                        | Update Description                                                                                                                                                                                                                   |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.0 "Memory Organization"      | Added Memory Maps for the new devices (see Figure 4-3 and Figure 4-4).                                                                                                                                                               |

|                                | Removed the BMXCHEDMA bit from the Bus Matrix Register map (see Table 4-1).                                                                                                                                                          |

|                                | Added the REFOTRIM register, added the DIVSWEN bit to the REFOCON registers, added Note 4 to the ULOCK and SOSCEN bits and added the PBDIVRDY bit in the OSCCON register in the in the System Control Register map (see Table 4-16). |

|                                | Removed the ALTI2C1 and ALTI2C2 bits from the DEVCFG3 register and added Note 1 to the UPLLEN and UPLLIDIV<2:0> bits of the DEVCFG2 register in the Device Configuration Word Summary (see Table 4-17).                              |

|                                | Updated Note 1 in the Device and Revision ID Summary (see Table 4-18).                                                                                                                                                               |

|                                | Added Note 2 to the PORTA Register map (see Table 4-19).                                                                                                                                                                             |

|                                | Added the ANSB6 and ANSB12 bits to the ANSELB register in the PORTB Register map (see Table 4-20).                                                                                                                                   |

|                                | Added Notes 2 and 3 to the PORTC Register map (see Table 4-21).                                                                                                                                                                      |

|                                | Updated all register names in the Peripheral Pin Select Register map (see Table 4-23).                                                                                                                                               |

|                                | Added values in support of new devices (16 KB RAM and 32 KB RAM) in the Data RAM Size register (see Register 4-5).                                                                                                                   |

|                                | Added values in support of new devices (64 KB Flash and 128 KB Flash) in the Data RAM Size register (see Register 4-5).                                                                                                              |

| 8.0 "Oscillator Configuration" | Added Note 5 to the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).                                                                                                                                                            |

|                                | Added the PBDIVRDY bit and Note 2 to the Oscillator Control register (see Register 8-1).                                                                                                                                             |

|                                | Added the DIVSWEN bit and Note 3 to the Reference Oscillator Control register (see Register 8-3).                                                                                                                                    |

|                                | Added the REFOTRIM register (see Register 8-4).                                                                                                                                                                                      |

| 21.0 "10-bit Analog-to-Digital | Updated the ADC1 Module Block Diagram (see Figure 21-1).                                                                                                                                                                             |

| Converter (ADC)"               | Updated the Notes in the ADC Input Select register (see Register 21-4).                                                                                                                                                              |

| 24.0 "Charge Time Measurement  | Updated the CTMU Block Diagram (see Figure 24-1).                                                                                                                                                                                    |

| Unit (CTMU)"                   | Added Note 3 to the CTMU Control register (see Register 24-1)                                                                                                                                                                        |

| 26.0 "Special Features"        | Added Note 1 and the PGEC4/PGED4 pin pair to the ICESEL<1:0> bits in DEVCFG0: Device Configuration Word 0 (see Register 26-1).                                                                                                       |

|                                | Removed the ALTI2C1 and ALTI2C2 bits from the Device Configuration Word 3 register (see Register 26-4).                                                                                                                              |

|                                | Removed 26.3.3 "Power-up Requirements".                                                                                                                                                                                              |

|                                | Added Note 3 to the Connections for the On-Chip Regulator diagram (see Figure 26-2).                                                                                                                                                 |

|                                | Updated the Block Diagram of Programming, Debugging and Trace Ports diagram (see Figure 26-3).                                                                                                                                       |

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section                           | Update Description                                                                                                                                    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29.0 "Electrical Characteristics" | Updated the Absolute Maximum Ratings (removed Voltage on VCORE with respect to Vss).                                                                  |

|                                   | Added the SPDIP specification to the Thermal Packaging Characteristics (see Table 29-2).                                                              |

|                                   | Updated the Typical values for parameters DC20-DC24 in the Operating Current (IDD) specification (see Table 29-5).                                    |

|                                   | Updated the Typical values for parameters DC30a-DC34a in the Idle Current (IIDLE) specification (see Table 29-6).                                     |

|                                   | Updated the Typical values for parameters DC40i and DC40n and removed parameter DC40m in the Power-down Current (IPD) specification (see Table 29-7). |

|                                   | Removed parameter D320 (VCORE) from the Internal Voltage Regulator Specifications and updated the Comments (see Table 29-13).                         |

|                                   | Updated the Minimum, Typical, and Maximum values for parameter F20b in the Internal FRC Accuracy specification (see Table 29-17).                     |

|                                   | Removed parameter SY01 (TPWRT) and removed all Conditions from Resets Timing (see Table 29-20).                                                       |

|                                   | Updated all parameters in the CTMU Specifications (see Table 29-39).                                                                                  |

| 31.0 "Packaging Information"      | Added the 28-lead SPDIP package diagram information (see <b>31.1</b> "Package Marking Information" and <b>31.2</b> "Package Details").                |

| "Product Identification System"   | Added the SPDIP (SP) package definition.                                                                                                              |

### **Revision C (November 2011)**

All major changes are referenced by their respective section in Table A-2.

TABLE A-2: MAJOR SECTION UPDATES

| Section                                                                                                                    | Update Description                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB Flash and 32 KB SRAM) with Audio and Graphics Interfaces, USB, and Advanced Analog" | Revised the source/sink on I/O pins (see "Input/Output" on page 1).  Added the SPDIP package to the PIC32MX220F032B device in the PIC32MX2XX USB Family Features (see Table 2). |

| 4.0 "Memory Organization"                                                                                                  | Removed ANSB6 from the ANSELB register and added the ODCB6, ODCB10, and ODCB11 bits in the PORTB Register Map (see Table 4-20).                                                 |

| 29.0 "Electrical Characteristics"                                                                                          | Updated the minimum value for parameter OS50 in the PLL Clock Timing Specifications (see Table 29-16).                                                                          |

### Revision D (February 2012)

All occurrences of VUSB were changed to: VUSB3V3. In addition, text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-3: MAJOR SECTION UPDATES

| Section                                                                                | Update Description                                                                                                                                                                |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|