#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 33                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032dt-50i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

# 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

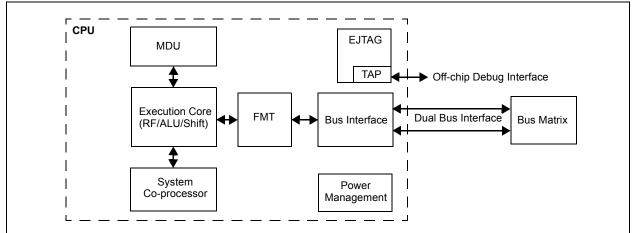

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

## 3.1 Features

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

#### FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

#### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |  |  |

|---------------------------|-----------|-----------------|--|--|

| Peripheral                | Base      | Offset<br>Start |  |  |

| Watchdog Timer            |           | 0x0000          |  |  |

| RTCC                      |           | 0x0200          |  |  |

| Timer1-5                  |           | 0x0600          |  |  |

| Input Capture 1-5         |           | 0x2000          |  |  |

| Output Compare 1-5        |           | 0x3000          |  |  |

| IC1 and IC2               |           | 0x5000          |  |  |

| SPI1 and SPI2             |           | 0x5800          |  |  |

| UART1 and UART2           |           | 0x6000          |  |  |

| PMP                       |           | 0x7000          |  |  |

| ADC                       | 0xBF80    | 0x9000          |  |  |

| CVREF                     |           | 0x9800          |  |  |

| Comparator                |           | 0xA000          |  |  |

| CTMU                      |           | 0xA200          |  |  |

| Oscillator                |           | 0xF000          |  |  |

| Device and Revision ID    |           | 0xF220          |  |  |

| Peripheral Module Disable |           | 0xF240          |  |  |

| Flash Controller          |           | 0xF400          |  |  |

| Reset                     |           | 0xF600          |  |  |

| PPS                       |           | 0xFA04          |  |  |

| Interrupts                |           | 0x1000          |  |  |

| Bus Matrix                |           | 0x2000          |  |  |

| DMA                       | 0xBF88    | 0x3000          |  |  |

| USB                       |           | 0x5050          |  |  |

| PORTA-PORTC               |           | 0x6000          |  |  |

| Configuration             | 0xBFC0    | 0x0BF0          |  |  |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

## REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| ========          |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

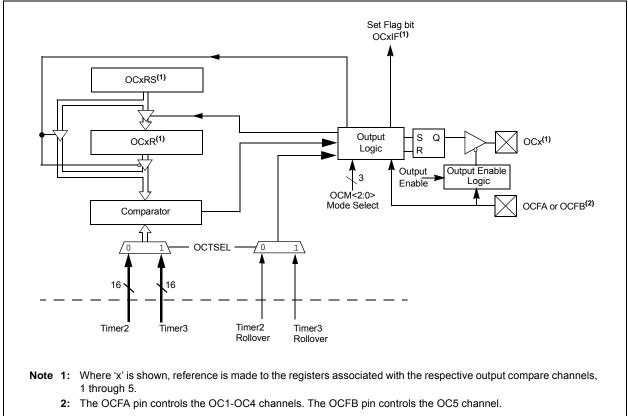

## 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

| REGISTE | R 18-1:           | I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: Ge          | eneral Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                     |

|         | (module           | interrupt when a general call address is received in the I2CxRSR<br>e is enabled for reception)                                                                       |

|         |                   | al call address is disabled                                                                                                                                           |

| bit 6   | STREN: S          | CLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                               |

|         |                   | njunction with SCLREL bit.                                                                                                                                            |

|         |                   | e software or receive clock stretching                                                                                                                                |

| L:1 F   |                   | e software or receive clock stretching                                                                                                                                |

| bit 5   |                   | cknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive) is transmitted when the software initiates an Acknowledge sequence. |

|         |                   | a NACK during an Acknowledge sequence                                                                                                                                 |

|         |                   | an ACK during an Acknowledge sequence                                                                                                                                 |

| bit 4   | ACKEN: A receive) | cknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master                                                                   |

|         | Hardwa            | Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br>are clear at end of master Acknowledge sequence.<br>wledge sequence not in progress        |

| bit 3   | RCEN: Re          | ceive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                          |

|         |                   | es Receive mode for I <sup>2</sup> C. Hardware clear at end of eighth bit of master receive data byte.<br>The sequence not in progress                                |

| bit 2   | PEN: Stop         | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence. ondition not in progress                                                         |

| bit 1   | RSEN: Re          | peated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                         |

|         |                   | Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of Repeated Start sequence.                                                                     |

|         | 0 = Repeat        | ted Start condition not in progress                                                                                                                                   |

| bit 0   |                   | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence. ondition not in progress                                                       |

|         |                   |                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| <b>NEGISTE</b> | -1\ 21-4. 1\      | ICDAIL. R         | IC DAIL W         |                   |                                         |                   |                  |                  |  |  |  |

|----------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04.04          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24          |                   | YEAR1             | 0<3:0>            |                   | YEAR01<3:0>                             |                   |                  |                  |  |  |  |

| 00.40          | U-0               | U-0               | U-0               | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16          |                   | —                 | _                 | MONTH10           | MONTH01<3:0>                            |                   |                  |                  |  |  |  |

| 15:8           | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |  |

|                |                   |                   | DAY10             | )<1:0>            | DAY01<3:0>                              |                   |                  |                  |  |  |  |

| 7.0            | U-0               | U-0               | U-0               | U-0               | U-0                                     | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0            | —                 | —                 | —                 | _                 | —                                       | — WDAY01<2:0>     |                  |                  |  |  |  |

|                |                   |                   |                   |                   |                                         |                   |                  |                  |  |  |  |

| Legend:        |                   |                   |                   |                   |                                         |                   |                  |                  |  |  |  |

| R = Read       | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0'      |                   |                  |                  |  |  |  |

| -n = Value     | e at POR          |                   | '1' = Bit is se   | t                 | '0' = Bit is cleared x = Bit is unknown |                   |                  |                  |  |  |  |

## REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 **YEAR01<3:0>:** Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9 bit 23-21 **Unimplemented:** Read as '0'

bit 20 **MONTH10:** Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | CH0NB             | _                 | _                 | _                 | CH0SB<3:0>        |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | CH0NA             |                   | _                 | _                 | CH0SA<3:0>        |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 |                   | _                | -                |  |  |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 31 |          | CH0NB: Negative Input Select bit for Sample B                                                                                        |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

|        |          | 1 = Channel 0 negative input is AN1                                                                                                  |

|        |          | 0 = Channel 0 negative input is VREFL                                                                                                |

| bit 30 | -28      | Unimplemented: Read as '0'                                                                                                           |

| bit 27 | -24      | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                  |

|        |          | 1111 = Channel 0 positive input is Open <sup>(1)</sup>                                                                               |

|        |          | 1110 = Channel 0 positive input is IVREF <sup>(2)</sup>                                                                              |

|        |          | 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(3)</sup>                                                    |

|        |          | 1100 = Channel 0 positive input is AN12 <sup>(4)</sup>                                                                               |

|        |          | •                                                                                                                                    |

|        |          | •                                                                                                                                    |

|        |          | •                                                                                                                                    |

|        |          | 0001 = Channel 0 positive input is AN1                                                                                               |

|        |          | 0000 = Channel 0 positive input is AN0                                                                                               |

| bit 23 |          | <b>CH0NA:</b> Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                              |

|        |          | 1 = Channel 0 negative input is AN1                                                                                                  |

|        | ~ ~      | 0 = Channel 0 negative input is VREFL                                                                                                |

| bit 22 | -20      | Unimplemented: Read as '0'                                                                                                           |

| bit 19 | -16      | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting                                                              |

|        |          | 1111 = Channel 0 positive input is Open <sup>(1)</sup>                                                                               |

|        |          | 1110 = Channel 0 positive input is IVREF <sup>(2)</sup>                                                                              |

|        |          | 1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup> |

|        |          |                                                                                                                                      |

|        |          |                                                                                                                                      |

|        |          |                                                                                                                                      |

|        |          | - Channel O positive input in AN1                                                                                                    |

|        |          | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                     |

| bit 15 | 0        | Unimplemented: Read as '0'                                                                                                           |

| bit 15 | -0       | Ommplemented. Nead as 0                                                                                                              |

| Note   | 1:       | This selection is only used with CTMU capacitive and time measurement.                                                               |

|        | 2:       | See Section 24.0 "Comparator Voltage Reference (CVREF)" for more information.                                                        |

|        | 3:       | See Section 25.0 "Charge Time Measurement Unit (CTMU)" for more information.                                                         |

|        | 3.<br>4: | AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices.                                               |

|        | т.       |                                                                                                                                      |

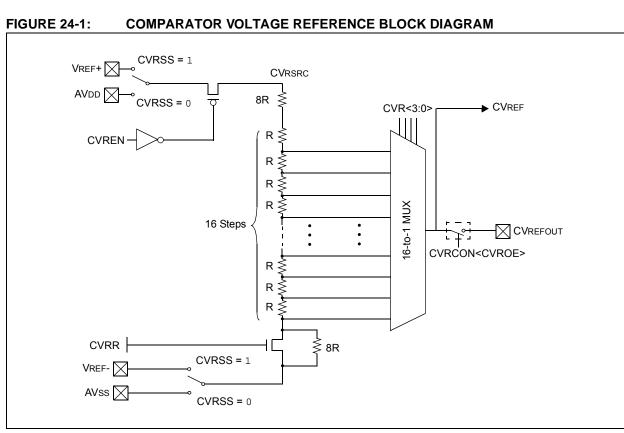

# 24.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- Output can be connected to a pin

A block diagram of the module is shown in Figure 24-1.

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

## 27.2 Configuration Registers

## TABLE 27-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess (                       |                  |           |                       |          |         |          |       |          |            | Bits                |        |                               |         |       |               |           |            |        | ú         |

|-----------------------------|------------------|-----------|-----------------------|----------|---------|----------|-------|----------|------------|---------------------|--------|-------------------------------|---------|-------|---------------|-----------|------------|--------|-----------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31/15                 | 30/14    | 29/13   | 28/12    | 27/11 | 26/10    | 25/9       | 24/8                | 23/7   | 22/6                          | 21/5    | 20/4  | 19/3          | 18/2      | 17/1       | 16/0   | All Reset |

|                             | DEVCFG3          | 31:16     | FVBUSONIO             | FUSBIDIO | IOL1WAY | PMDL1WAY | -     | —        | _          | —                   | -      | —                             | —       | —     | —             | —         | —          | _      | xxxx      |

| UDFU                        | DEVCEGS          | 15:0      | USERID<15:0> xxx      |          |         |          |       |          |            |                     |        |                               |         |       | xxxx          |           |            |        |           |

|                             | DEVCFG2          | 31:16     | _                     | —        | _       | —        | —     | —        | _          |                     |        |                               | _       | _     | FPLLODIV<2:0> |           |            | xxxx   |           |

| 0014                        |                  | 15:0      | UPLLEN <sup>(1)</sup> |          |         | —        | _     | UPL      | LIDIV<2:0> | <sub>&gt;</sub> (1) | _      | - FPLLMUL<2:0> — FPLLIDIV<2:0 |         |       | )>            | xxxx      |            |        |           |

|                             | DEVCFG1          | 31:16     |                       |          |         | —        | _     | _        | FWDTWI     | NSZ<1:0>            | FWDTEN | WINDIS                        | _       |       | ١             | WDTPS<4:0 | >          |        | xxxx      |

|                             |                  | 15:0      | FCKSM                 | <1:0>    | FPBD    | IV<1:0>  | _     | OSCIOFNC | POSCM      | OD<1:0>             | IESO   | _                             | FSOSCEN |       | _             | F         | NOSC<2:0>  | >      | xxxx      |

|                             | DEVCFG0          | 31:16     | _                     | —        | _       | CP       | —     | —        | _          | BWP                 | —      | _                             | _       | _     | _             | F         | WP<8:6>(2) | )      | xxxx      |

| UBFC                        |                  | 15:0      |                       |          | PWP<    | <5:0>    |       |          |            |                     | _      | _                             | _       | ICESE | L<1:0>        | JTAGEN    | DEBUG      | G<1:0> | xxxx      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on PIC32MX2XX devices.

2: PWP<8:7> are only available on devices with 256 KB of Flash.

## TABLE 27-2: DEVICE ID, REVISION, AND CONFIGURATION SUMMARY

| ess                         |                       | 0         |                               | Bits  |        |         |       |       |      |       |         |      |                     |                     |        |      |      |       | (1)        |

|-----------------------------|-----------------------|-----------|-------------------------------|-------|--------|---------|-------|-------|------|-------|---------|------|---------------------|---------------------|--------|------|------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15                         | 30/14 | 29/13  | 28/12   | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6 | 21/5                | 20/4                | 19/3   | 18/2 | 17/1 | 16/0  | All Resets |

| F220                        | DEVID                 | 31:16     | VER<3:0>         DEVID<27:16> |       |        |         |       |       |      |       |         |      | xxxx <sup>(1)</sup> |                     |        |      |      |       |            |

| F220                        | DEVID                 | 15:0      | DEVID<15:0>                   |       |        |         |       |       |      |       |         |      |                     | xxxx <sup>(1)</sup> |        |      |      |       |            |

| F000                        |                       | 31:16     | -                             | _     | _      | _       | _     | _     | _    | _     | _       | _    | _                   | _                   | _      | _    | _    | _     | 0000       |

|                             | CFGCON                | 15:0      |                               | —     | IOLOCK | PMDLOCK | _     | _     | _    | _     | —       | _    | _                   | _                   | JTAGEN | _    | _    | TDOEN | 000B       |

| F220                        | SYSKEY <sup>(3)</sup> | 31:16     |                               |       |        |         |       |       |      | SYSKE | /~31.05 |      |                     |                     |        |      |      |       | 0000       |

| F230                        | STORET                | 15:0      |                               |       |        |         |       |       |      | SISKE | 1~51.02 |      |                     |                     |        |      |      |       | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the device variant.

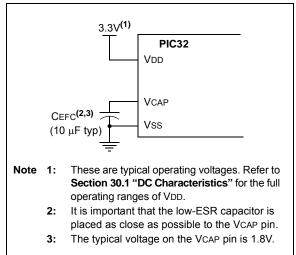

## 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

## 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

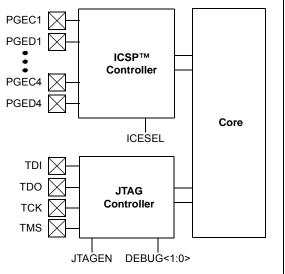

## 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

#### TABLE 30-39: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                           | (unless | -     | e stated)<br>ature -4 | •0°C ≤ TA : | <b>3V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +105°C for V-temp |

|--------------------|---------|---------------------------------------------------------------------------|---------|-------|-----------------------|-------------|--------------------------------------------------------------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.    | Тур.  | Max.                  | Units       | Conditions                                                         |

| PM11               | Twr     | PMWR Pulse Width                                                          | _       | 1 Трв | _                     | _           | _                                                                  |

| PM12               | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —       | 2 Трв |                       | _           | _                                                                  |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —       | 1 Трв |                       | _           | —                                                                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### TABLE 30-40: OTG ELECTRICAL SPECIFICATIONS

| AC CHA        | RACTERI | STICS                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industr} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-tem} \end{array}$ |      |      | $\bar{A} \le +85^{\circ}C$ for Industrial |                                                                                   |

|---------------|---------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------------------------------|-----------------------------------------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                              | Тур. | Max. | Units                                     | Conditions                                                                        |

| USB313        | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                                                               |      | 3.6  | V                                         | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |

| USB315        | VILUSB  | Input Low Voltage for USB Buffer  | —                                                                                                                                                                                                                                                                                 | —    | 0.8  | V                                         | —                                                                                 |

| USB316        | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                                                               | —    | _    | V                                         | —                                                                                 |

| USB318        | VDIFS   | Differential Input Sensitivity    | _                                                                                                                                                                                                                                                                                 | _    | 0.2  | V                                         | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |

| USB319        | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                                                               |      | 2.5  | V                                         | —                                                                                 |

| USB320        | Zout    | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                                                              | —    | 44.0 | Ω                                         | —                                                                                 |

| USB321        | Vol     | Voltage Output Low                | 0.0                                                                                                                                                                                                                                                                               | _    | 0.3  | V                                         | 1.425 kΩ load<br>connected to VUSB3V3                                             |

| USB322        | Vон     | Voltage Output High               | 2.8                                                                                                                                                                                                                                                                               | _    | 3.6  | V                                         | 1.425 kΩ load connected to ground                                                 |

# 31.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 30.0** "Electrical Characteristics", with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 30.0** "**Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      |                          |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               |                          |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

## 31.1 DC Characteristics

#### TABLE 31-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range    | Max. Frequency                    |  |  |

|----------------|---------------------------|----------------|-----------------------------------|--|--|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX 28/36/44-pin Famil |  |  |

| MDC5           | 2.3-3.6V                  | -40°C to +85°C | 50 MHz                            |  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

#### TABLE 31-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA         | CTERISTICS             | 5           | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |  |

|------------------|------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Parameter<br>No. | Typical <sup>(3)</sup> | Max.        | Units                                                                                                                                           | Conditions |  |  |  |

| Operating (      | Current (IDD)          | (Note 1, 2) |                                                                                                                                                 |            |  |  |  |

| MDC24            | 25                     | 37          | mA                                                                                                                                              | 50 MHz     |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- 3: RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                    | (unless othe | erwise state | nditions: 2.3<br>ed)<br>-40°C ≤ TA ≤ |       |                               |

|--------------------|--------|------------------------------------------------------------------------------------|--------------|--------------|--------------------------------------|-------|-------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                                    | Min.         | Typical      | Max.                                 | Units | Conditions                    |

| MOS10              |        | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4      |              | 50<br>50                             |       | EC (Note 2)<br>ECPLL (Note 1) |

Note 1: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

**2:** This parameter is characterized, but not tested in manufacturing.

## TABLE 31-6:SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | (unless | otherwise | stated) |       | 2.3V to 3.6V<br>△ ≤ +85°C for Industrial |

|--------------------|--------|------------------------------------|---------|-----------|---------|-------|------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                    | Min.    | Typical   | Max.    | Units | Conditions                               |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2) | Тѕск/2  |           | —       | ns    | _                                        |

| MSP11              | TscH   | SCKx Output High Time (Note 1,2)   | Tscк/2  |           | —       | ns    |                                          |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

#### TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |        |      |      |       |            |

|--------------------|--------|-------------------------------------------------------|--------|------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                        | Min.   | Тур. | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2)                    | Тѕск/2 | _    |      | ns    | _          |

| MSP11              | TSCH   | SCKx Output High Time<br>(Note 1,2)                   | Тѕск/2 | _    | _    | ns    | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

NOTES:

## **Revision E (October 2012)**

All singular pin diagram occurrences of CVREF were changed to: CVREFOUT. In addition, minor text and formatting changes were incorporated throughout the document.

All major changes are referenced by their respective section in Table A-4.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                                | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>128 KB Flash and 32 KB SRAM)<br>with Audio and Graphics<br>Interfaces, USB, and Advanced<br>Analog" | <ul> <li>Updated the following feature sections:</li> <li>"Operating Conditions"</li> <li>"Communication Interfaces"</li> </ul>                                                                                                                                                                                                                                                                                                             |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | Removed Section 2.8 "Configuration of Analog and Digital Pins During ICSP Operations".                                                                                                                                                                                                                                                                                                                                                      |

| 3.0 "CPU"                                                                                                                              | Removed references to GPR shadow registers in <b>3.1 "Features"</b> and <b>3.2.1 "Execution Unit"</b> .                                                                                                                                                                                                                                                                                                                                     |

| 4.0 "Memory Organization"                                                                                                              | Updated the BRG bit range in the SPI1 and SPI2 Register Map (see Table 4-8).<br>Added the PWP<6> bit to the Device Configuration Word Summary<br>(see Table 4-17).                                                                                                                                                                                                                                                                          |

| 5.0 "Flash Program Memory"                                                                                                             | Added a note with Flash page size and row size information.                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.0 "Interrupt Controller"                                                                                                             | Updated the TPC<2:0> bit definitions (see Register 7-1).<br>Updated the IPTMR<31:0> bit definition (see Register 7-3).                                                                                                                                                                                                                                                                                                                      |

| 8.0 "Oscillator Configuration"                                                                                                         | Updated the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).<br>Updated the RODIV<14:0> bit definitions (see Register 8-3).                                                                                                                                                                                                                                                                                                            |

| 10.0 "USB On-The-Go (OTG)"                                                                                                             | Updated the Notes in the USB Interface Diagram (see Figure 10-1).                                                                                                                                                                                                                                                                                                                                                                           |

| 18.0 "Universal Asynchronous<br>Receiver Transmitter (UART)"                                                                           | Updated the baud rate range in the list of primary features.                                                                                                                                                                                                                                                                                                                                                                                |

| 26.0 "Special Features"                                                                                                                | Added the PWP<6> bit to the Device Configuration Word 0 (see Register 26-1).                                                                                                                                                                                                                                                                                                                                                                |

| 29.0 "Electrical Characteristics"                                                                                                      | <ul> <li>Added Note 1 to Operating MIPS vs. Voltage (see Table 29-1).</li> <li>Added Note 2 to DC Temperature and Voltage Specifications (see Table 29-4).</li> <li>Updated the Conditions for parameter DC25 in DC Characteristics: Operating Current (IDD) (see Table 29-5).</li> <li>Added Note 2 to Electrical Characteristics: BOR (see Table 29-10).</li> <li>Added Note 4 to Comparator Specifications (see Table 29-12).</li> </ul> |

|                                                                                                                                        | <ul> <li>Added Note 5 to ADC Module Specifications (see Table 29-32).</li> <li>Updated the 10-bit Conversion Rate Parameters and added Note 3 (see Table 29-33).</li> <li>Added Note 4 to the Analog-to-Digital Conversion Timing Requirements (see Table 29-34).</li> <li>Added Note 3 to CTMU Current Source Specifications (see Table 29-39).</li> </ul>                                                                                 |

| 30.0 "50 MHz Electrical<br>Characteristics"                                                                                            | New chapter with electrical characteristics for 50 MHz devices.                                                                                                                                                                                                                                                                                                                                                                             |

| 31.0 "Packaging Information"                                                                                                           | The 36-pin and 44-pin VTLA packages have been updated.                                                                                                                                                                                                                                                                                                                                                                                      |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| (64 KB RAM, 256 KB Flash)                         | 42  |

|---------------------------------------------------|-----|

| Memory Organization                               | 37  |

| Microchip Internet Web Site                       | 341 |

| MPLAB ASM30 Assembler, Linker, Librarian          | 254 |

| MPLAB Integrated Development Environment Software | 253 |

| MPLAB PM3 Device Programmer                       | 255 |

| MPLAB REAL ICE In-Circuit Emulator System         | 255 |

| MPLINK Object Linker/MPLIB Object Librarian       | 254 |

|                                                   |     |

# 0

| Oscillator Configuration | 73  |

|--------------------------|-----|

| Output Compare           | 161 |

# Ρ

| -                                  |     |

|------------------------------------|-----|

| Packaging                          |     |

| Details                            | 313 |

| Marking                            |     |

| Parallel Master Port (PMP)         |     |

| PIC32 Family USB Interface Diagram | 104 |

| Pinout I/O Descriptions (table)    | 20  |

| Power-on Reset (POR)               |     |

| and On-Chip Voltage Regulator      |     |

| Power-Saving Features              |     |

| CPU Halted Methods                 | 233 |

| Operation                          |     |

| with CPU Running                   |     |

| -                                  |     |

## R

| Real-Time Clock and Calendar (RTCC)            | .199 |

|------------------------------------------------|------|

| Register Maps                                  | 5–?? |

| Registers                                      |      |

| [pin name]R (Peripheral Pin Select Input)      |      |

| AD1CHS (ADC Input Select)                      | .217 |

| AD1CON1 (ADC Control 1)                        | 213  |

| AD1CON2 (ADC Control 2)                        | 215  |

| AD1CON3 (ADC Control 3)                        | 216  |

| AD1CSSL (ADC Input Scan Select)                | .218 |

| ALRMDATE (Alarm Date Value)                    | 208  |

| ALRMTIME (Alarm Time Value)                    | 207  |

| BMXBOOTSZ (Boot Flash (IFM) Size               | 51   |

| BMXCON (Bus Matrix Configuration)              | 46   |

| BMXDKPBA (Data RAM Kernel Program              |      |

| Base Address)                                  |      |

| BMXDRMSZ (Data RAM Size Register)              |      |

| BMXDUDBA (Data RAM User Data Base Address)     | 48   |

| BMXDUPBA (Data RAM User Program                |      |

| Base Address)                                  |      |

| BMXPFMSZ (Program Flash (PFM) Size)            | 51   |

| BMXPUPBA (Program Flash (PFM) User Program     |      |

| Base Address)                                  |      |

| CFGCON (Configuration Control)                 |      |

| CM1CON (Comparator 1 Control)                  |      |

| CMSTAT (Comparator Status Register)            |      |

| CNCONx (Change Notice Control for PORTx)       |      |

| CTMUCON (CTMU Control)                         |      |

| CVRCON (Comparator Voltage Reference Control). |      |

| DCHxCON (DMA Channel 'x' Control)              |      |

| DCHxCPTR (DMA Channel 'x' Cell Pointer)        |      |

| DCHxCSIZ (DMA Channel 'x' Cell-Size)           |      |

| DCHxDAT (DMA Channel 'x' Pattern Data)         |      |

| DCHxDPTR (Channel 'x' Destination Pointer)     | 99   |

| DCHxDSA (DMA Channel 'x' Destination           |      |

| Start Address)                                 |      |

| DCHxDSIZ (DMA Channel 'x' Destination Size)    |      |

| DCHxECON (DMA Channel 'x' Event Control)       |      |

| DCHxINT (DMA Channel 'x' Interrupt Control)    | 95   |

|                                                |      |

| DCHxSPTR (DMA Channel 'x' Source Pointer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|