Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 010.00                   |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032dt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| TABLE 1-1 | : PING            | DUT I/O D                         |                     | IONS (CO                        | NTINU       | ED)                  | 1                                                 |

|-----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------------|---------------------------------------------------|

|           |                   | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                      |                                                   |

| Pin Name  | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                       |

| SDA1      | 15                | 18                                | 19                  | 1                               | I/O         | ST                   | Synchronous serial data input/output for I2C1     |

| SCL2      | 4                 | 7                                 | 2                   | 24                              | I/O         | ST                   | Synchronous serial clock input/output for<br>I2C2 |

| SDA2      | 3                 | 6                                 | 1                   | 23                              | I/O         | ST                   | Synchronous serial data input/output for I2C2     |

| TMS       | 19 <b>(2)</b>     | 22 <sup>(2)</sup>                 | 25 <sup>(2)</sup>   | 12                              | 1           | ST                   | JTAG Test mode select pin                         |

| _         | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <b>(3)</b>       | 12                              | 1           | _                    | STAG Test mode select pin                         |

| TCK       | 14                | 17                                | 18                  | 13                              | I           | ST                   | JTAG test clock input pin                         |

| TDI       | 13                | 16                                | 17                  | 35                              | 0           | —                    | JTAG test data input pin                          |

| TDO       | 15                | 18                                | 19                  | 32                              | 0           | —                    | JTAG test data output pin                         |

| RTCC      | 4                 | 7                                 | 2                   | 24                              | 0           | ST                   | Real-Time Clock alarm output                      |

| CVREF-    | 28                | 3                                 | 34                  | 20                              | Ι           | Analog               | Comparator Voltage Reference (low)                |

| CVREF+    | 27                | 2                                 | 33                  | 19                              | I           | Analog               | Comparator Voltage Reference (high)               |

| CVREFOUT  | 22                | 25                                | 28                  | 14                              | 0           | Analog               | Comparator Voltage Reference output               |

| C1INA     | 4                 | 7                                 | 2                   | 24                              | I           | Analog               | Comparator Inputs                                 |

| C1INB     | 3                 | 6                                 | 1                   | 23                              | I           | Analog               |                                                   |

| C1INC     | 2                 | 5                                 | 36                  | 22                              | I           | Analog               |                                                   |

| C1IND     | 1                 | 4                                 | 35                  | 21                              | I           | Analog               |                                                   |

| C2INA     | 2                 | 5                                 | 36                  | 22                              | 1           | Analog               | 7                                                 |

| C2INB     | 1                 | 4                                 | 35                  | 21                              | I           | Analog               |                                                   |

| C2INC     | 4                 | 7                                 | 2                   | 24                              | I           | Analog               |                                                   |

| C2IND     | 3                 | 6                                 | 1                   | 23                              | I           | Analog               |                                                   |

| C3INA     | 23                | 26                                | 29                  | 15                              | I           | Analog               |                                                   |

| C3INB     | 22                | 25                                | 28                  | 14                              | I           | Analog               | 1                                                 |

| C3INC     | 27                | 2                                 | 33                  | 19                              | I           | Analog               | 1                                                 |

| C3IND     | 1                 | 4                                 | 35                  | 21                              | I           | Analog               | 1                                                 |

| C1OUT     | PPS               | PPS                               | PPS                 | PPS                             | 0           | —                    | Comparator Outputs                                |

| C2OUT     | PPS               | PPS                               | PPS                 | PPS                             | 0           | —                    | 1                                                 |

| C3OUT     | PPS               | PPS                               | PPS                 | PPS                             | 0           | —                    | 1                                                 |

|           |                   | MOS compa<br>itt Trigger in       |                     |                                 | •           | Analog =<br>O = Outp | Analog input P = Power<br>but I = Input           |

#### DINOUT 1/0 DECODIDITIONS (CONTINUED)

TTL = TTL input buffer PPS = Peripheral Pin Select Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

— = N/A

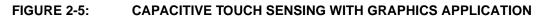

# 2.9 Typical Application Connection Examples

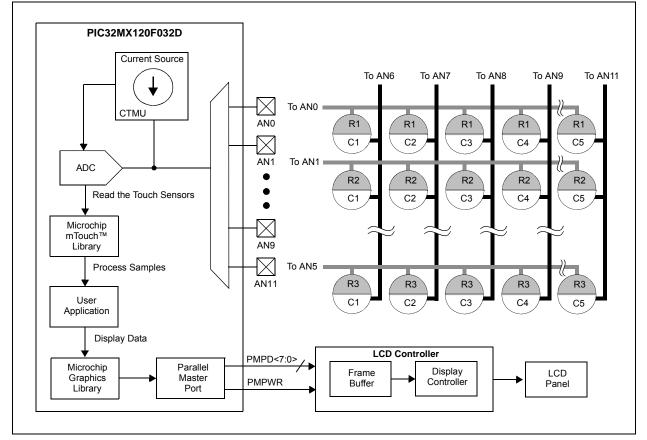

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

# 5.1 Flash Controller Control Registers

# TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |       |                  |       |        |         |       |      | Bit     | s       |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|-------|------------------|-------|--------|---------|-------|------|---------|---------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14            | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>  | 31:16     | —     | —                | -     | —      | —       | —     | _    | -       | —       | _    | —    | _    | —    | —    | -      | -    | 0000       |

| F400                        | INVIVICOIN**           | 15:0      | WR    | WREN             | WRERR | LVDERR | LVDSTAT | _     |      | —       |         | —    | —    | —    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |                  |       |        |         |       |      |         | <31·0>  |      |      |      |      |      |        |      | 0000       |

| 1410                        |                        | 15:0      |       | NVMKEY<31:0>     |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

| F420                        | NVMADDR <sup>(1)</sup> | 31:16     |       | NVMADDR<31:0>    |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

| 1 420                       | NVINADDR               | 15:0      |       |                  |       |        |         |       |      | NVINADD | N~51.02 |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       | NVMDATA<31:0>    |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

| 1 430                       |                        | 15:0      |       | NVMDATA<51.0>    |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

| E440                        | NVMSRCADDR             | 31:16     |       |                  |       |        |         |       | N    |         |         |      |      |      |      |      |        |      | 0000       |

| 1 440                       | NVINGRCADDR            | 15:0      |       | NVMSRCADDR<31:0> |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

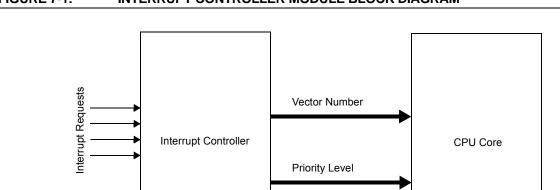

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

# FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

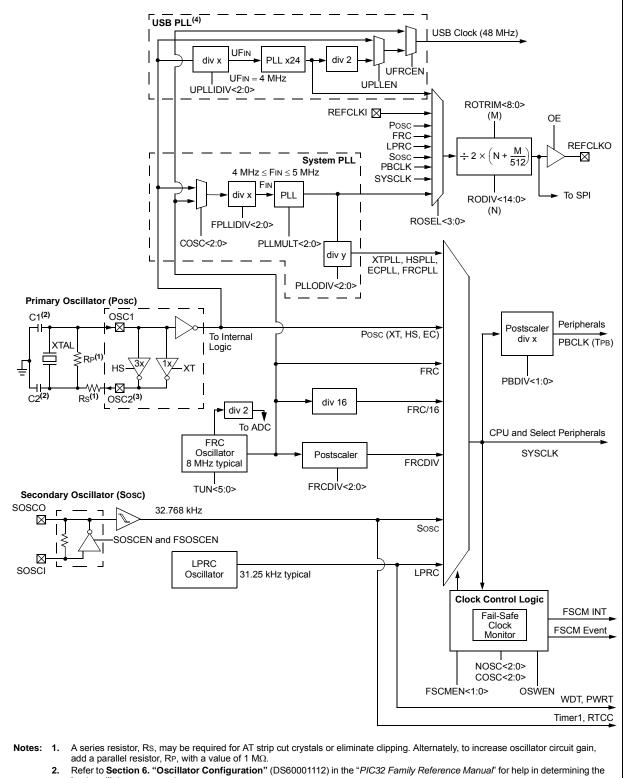

# FIGURE 8-1: OSCILLATOR DIAGRAM

Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determinin best oscillator components.

3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

4. The USB PLL is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRI             | //<8:1>           |                   |                  |                  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |

## REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

## Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

#### **USB Control Registers** 10.1

# TABLE 10-1: USB REGISTER MAP

| ess                         |                                 |           |       | Bits  |                                                                                                                                                                                                                                                                                                                       |       |       |       |      |      |                        |          |          |                  |          |          |                 |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|------|------------------------|----------|----------|------------------|----------|----------|-----------------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13                                                                                                                                                                                                                                                                                                                 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6     | 21/5     | 20/4             | 19/3     | 18/2     | 17/1            | 16/0     | All Resets |

| 5040                        | (4)                             | 31:16     | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     |      | _    | —                      | —        | —        | —                | —        | —        | _               | —        | 000        |

| 5040                        | UTUTUIK /                       | 15:0      |       | _     | _                                                                                                                                                                                                                                                                                                                     | —     | _     | _     |      | _    | IDIF                   | T1MSECIF | LSTATEIF | ACTVIF           | SESVDIF  | SESENDIF | 1               | VBUSVDIF | 000        |

| 5050                        | <b>U10TGIE</b>                  | 31:16     | —     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | —    | —    | —                      |          | —        | —                | —        | —        | _               | —        | 000        |

| 0000                        | OTOTOLE                         | 15:0      | —     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | —    | —    | IDIE                   | T1MSECIE | LSTATEIE | ACTVIE           | SESVDIE  | SESENDIE | _               | VBUSVDIE | 000        |

| 5060                        | U10TGSTAT <sup>(3)</sup>        | 31:16     | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | 0101001/11                      | 15:0      | —     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | —    | —    | ID                     |          | LSTATE   | —                | SESVD    | SESEND   | _               | VBUSVD   | 000        |

| 5070                        | U10TGCON                        | 31:16     | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0070                        | UTOTOOON                        | 15:0      | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | _    | —    | DPPULUP                | DMPULUP  | DPPULDWN | DMPULDWN         | VBUSON   | OTGEN    | VBUSCHG         | VBUSDIS  | 000        |

| 5080                        | U1PWRC                          | 31:16     | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | on wite                         | 15:0      | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | _    | —    | UACTPND <sup>(4)</sup> |          | —        | USLPGRD          | USBBUSY  | —        | USUSPEND        | USBPWR   | 000        |

|                             |                                 | 31:16     | _     | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _                                                                                                                                                                                                                                                                                                                     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF | RESUMEIF | IDLEIF           | TRNIF    | SOFIF    | UERRIF          | URSTIF   | 000        |

|                             |                                 | 04.40     |       |       |                                                                                                                                                                                                                                                                                                                       |       |       |       |      |      |                        |          |          |                  |          |          |                 | DETACHIF | 000        |

| 5210                        | U1IE                            | 31:16     | _     | _     |                                                                                                                                                                                                                                                                                                                       |       |       |       |      | _    | —                      | —        |          | —                | —        | —        | —               |          | 000        |

| 5210                        | OTIE                            | 15:0      | —     | —     | STALLE LATTACHE RESUMEET IDLETE I TRNE - SOFIE I UERRIE                                                                                                                                                                                                                                                               |       |       |       |      |      |                        |          |          |                  |          |          | 000             |          |            |

|                             |                                 | 31:16     | _     | _     |                                                                                                                                                                                                                                                                                                                       |       |       |       |      |      |                        |          |          |                  |          |          |                 | _        |            |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | -     -     -     -     -     -     -     -     0000       -     -     -     -     -     -     -     -     -     0000       -     -     -     -     -     -     -     -     -     0000       -     -     -     -     -     -     -     -     -     0000       0000     -     -     -     -     -     -     -     0000 |       |       |       |      |      |                        |          |          |                  |          |          |                 |          |            |

|                             |                                 | 31:16     | _     | _     |                                                                                                                                                                                                                                                                                                                       | _     | _     | _     | _    | _    | _                      |          | _        | _                | _        | _        | _               |          | 000        |

| 5230                        | U1EIE                           | 15:0      | _     | _     | _                                                                                                                                                                                                                                                                                                                     | _     | _     | _     | _    | _    | BTSEE                  | BMXEE    | DMAEE    | BTOEE            | DFN8EE   | CRC16EE  | CRC5EE<br>EOFEE | PIDEE    | 000        |

|                             | (2)                             | 31:16     | _     | _     |                                                                                                                                                                                                                                                                                                                       | _     | _     |       |      | _    |                        | _        |          | _                | _        |          | _               | _        | 000        |

| 5240                        | U1STAT <sup>(3)</sup>           | 15:0      | _     | _     | _                                                                                                                                                                                                                                                                                                                     | _     | _     | _     |      | _    |                        |          | PT<3:0>  |                  | DIR      | PPBI     | _               | _        | 000        |

|                             |                                 | 31:16     | _     |       | _                                                                                                                                                                                                                                                                                                                     | _     | _     | _     |      | _    | _                      | _        |          |                  | _        | _        | _               | _        | 000        |

| 5250                        | U1CON                           |           |       |       |                                                                                                                                                                                                                                                                                                                       |       |       |       |      |      |                        |          | PKTDIS   |                  |          |          |                 | USBEN    | 000        |

|                             |                                 | 15:0      |       | —     | —                                                                                                                                                                                                                                                                                                                     | —     | —     | —     |      | —    | JSTATE                 | SE0      | TOKBUSY  | USBRST           | HOSTEN   | RESUME   | PPBRST          | SOFEN    | 000        |

| 5260                        | U1ADDR                          | 31:16     | _     | _     | _                                                                                                                                                                                                                                                                                                                     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | —        | 000        |

| 5260                        | UTADDR                          | 15:0      | _     | _     | _                                                                                                                                                                                                                                                                                                                     | _     | _     | —     | _    | _    | LSPDEN                 |          |          | DE               | VADDR<6: | 0>       |                 |          | 000        |

| 5070                        |                                 | 31:16     | -     | _     | _                                                                                                                                                                                                                                                                                                                     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | _        | 000        |

| 5270                        | U1BDTP1                         | 15:0      | —     |       |                                                                                                                                                                                                                                                                                                                       | —     |       |       |      | _    |                        |          | BC       | )<br>TPTRL<15:9> | >        |          |                 |          | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

2: This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 |                   |                   |                   | _                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 |                   |                   |                   | _                 | _                | —                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  |                  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| TABL                        | E 11-7:              | PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED) Bits |       |       |       |       |       |       |      |      |      |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| SS                          |                      |                                                            |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range                                                  | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16                                                      | _     | -     | —     | -     | _     | -     | _    | _    | -    | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0                                                       | _     |       |       |       | —     |       | _    | —    |      |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16                                                      | —     | —     | —     | —     | —     | —     | _    | —    | —    | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0                                                       | —     | _     | —     | _     | —     | —     | -    |      | _    | —    | —    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16                                                      | —     | _     | —     | _     | —     | —     | -    |      | _    | —    | —    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0                                                       | —     | —     | _     | —     | —     | _     |      |      | —    | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16                                                      | —     | —     | _     | —     | —     | _     |      |      | —    | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        | KPD14K               | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R               | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBIOR               | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0                                                       | —     | —     | —     | —     | —     | —     | -    |      | —    | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16                                                      | —     | —     | _     | —     | —     | —     |      |      | —    | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>V</sup>   | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16                                                      | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>   | 15:0                                                       | _     | —     | _     | _     | -     | —     | _    | _    | _    | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 31:16                                                      |       | —     | —     | —     | —     | —     | _    |      | —    | _    | —    | —    | _    | _    | _      | _    | 0000       |

| FB80                        | KPUSK"               | 15:0                                                       |       |       |       |       | —     | _     | _    | _    | —    |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 31:16                                                      |       |       |       |       | —     | _     | _    | _    | _    |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"               | 15:0                                                       |       |       |       |       | —     | _     | _    | _    | —    |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 31:16                                                      |       | —     |       | —     | —     | —     | _    |      | —    |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | RPU/R <sup>(1)</sup> | 15:0                                                       | _     | _     | —     | _     | _     | —     | —    | _    | —    |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

# 12.2 Timer1 Control Registers

# TABLE 12-1: TIMER1 REGISTER MAP

| ess                       |                                 | 0         | Bits  |       |       |       |       |       |      |      |        |      |       |        |      | s     |      |      |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | _     | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON    | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —     | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      |       |       |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000       |

| 0620                      | PR1                             | 31:16     | —     | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                             | 15:0      |       |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        | —                 | —                 | —                 |                   | R                 | XBUFELM<4:(       | )>               |                  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | —                 | —                 | —                 |                   | Tک                | KBUFELM<4:0       | )>               |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         | —                 | —                 | —                 | FRMERR            | SPIBUSY           | —                 | _                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            |                   | SPITBF           | SPIRBF           |

## REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware   |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 21.24        | U-0                 | U-0                 |

| 31:24        |                   | -                 | _                 | -                 | _                 |                   | _                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | FORM<2:0>         |                     |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          | SSRC<2:0>         |                   |                   | CLRASAM           |                   | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

## REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 =Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

## bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|--------------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0                      | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                        | —                 | —                 | _                        | —                 | —                 | —                | -                |  |  |

| 00.40        | U-0                      | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                        | —                 | —                 | _                        | _                 | —                 | _                | -                |  |  |

| 45.0         | R/W-0                    | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ADRC                     | _                 | —                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0                    | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |

|              | ADCS<7:0> <sup>(2)</sup> |                   |                   |                          |                   |                   |                  |                  |  |  |

# Legend:

| =ogona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- **2:** This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

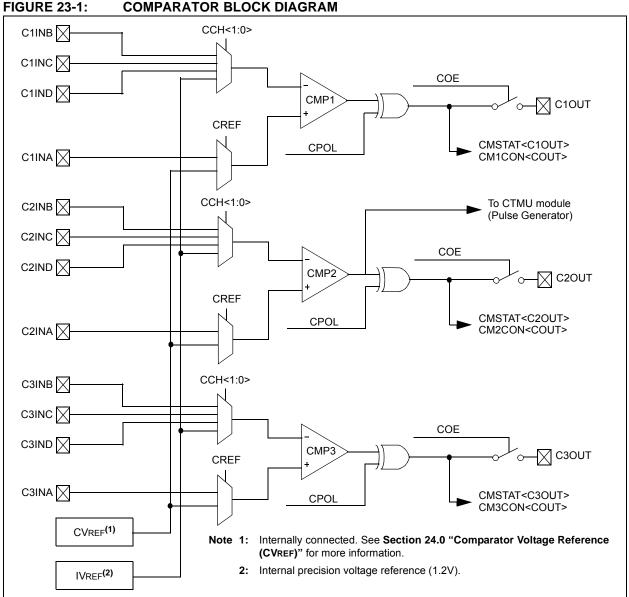

#### 23.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains three comparators that can be configured in a variety of ways.

Following are some of the key features of this module:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 23-1.

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

## 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

# 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

# TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS                   |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                |  |

|---------------|---------|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|

| Param.<br>No. | Symbol  | Charact                  | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Max. | Units | Conditions                     |  |

| IM10          | TLO:SCL | Clock Low Time           | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μs    | —                              |  |

|               |         |                          | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS    | —                              |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | —    | μs    | _                              |  |

| IM11          | THI:SCL | Clock High Time          | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS    | —                              |  |

|               |         |                          | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    | —                              |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       |      | μs    | -                              |  |

| IM20          | TF:SCL  | SDAx and SCLx            | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                     | 300  | ns    | CB is specified to be          |  |

|               |         | Fall Time                | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | from 10 to 400 pF              |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                     | 100  | ns    |                                |  |

| IM21          | TR:SCL  | SDAx and SCLx            | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                     | 1000 | ns    | CB is specified to be          |  |

|               |         | Rise Time                | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | from 10 to 400 pF              |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                     | 300  | ns    |                                |  |

| IM25          | TSU:DAT | Data Input<br>Setup Time | 100 kHz mode                  | 250                                                                                                                                                                                                                                                                                   |      | ns    | —                              |  |

|               |         |                          | 400 kHz mode                  | 100                                                                                                                                                                                                                                                                                   | _    | ns    |                                |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                                                                                   |      | ns    |                                |  |

| IM26          | THD:DAT | Data Input<br>Hold Time  | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                     |      | μS    | —                              |  |

|               |         |                          | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                     | 0.9  | μS    |                                |  |

|               |         |                          | 1 MHz mode<br>(Note 2)        | 0                                                                                                                                                                                                                                                                                     | 0.3  | μS    |                                |  |

| IM30          | TSU:STA | Start Condition          | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS    | Only relevant for              |  |

|               |         | Setup Time               | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    | Repeated Start condition       |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    | condition                      |  |

| IM31          | THD:STA | Start Condition          | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS    | After this period, the         |  |

|               |         | Hold Time                | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | -    | μS    | first clock pulse is generated |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       |      | μS    | generaleu                      |  |

| IM33          | Tsu:sto | Stop Condition           | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    |                                |  |