Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx220f032dt-v-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

## TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

## 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

## 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | —                 | _                 | -                 | _                 | —                 |                  | _                |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |

## REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | NVMDA             | TA<15:8>          |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

## REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | >                 |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | NVMSRC/           | ADDR<15:8>        |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | J = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |

| 10.0         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                    |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |  |  |

| 7:0          | —                 | —                 | _                 | —                 | _                 | —                 | —                | SWRST <sup>(1)</sup> |  |  |  |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | Legend: HC = Cleared by hardware |                           |                    |  |  |  |

|-------------------|----------------------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                 | U = Unimplemented bit, re | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set                 | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable Software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit is written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Interrupt Source <sup>(1)</sup>       | IRQ | Vector |          | Interru       | pt Bit Location |              | Persistent |

|---------------------------------------|-----|--------|----------|---------------|-----------------|--------------|------------|

| Interrupt Source.                     | #   | #      | Flag     | Enable        | Priority        | Sub-priority | Interrupt  |

| U1E – UART1 Fault                     | 39  | 32     | IFS1<7>  | IEC1<7>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1RX – UART1 Receive Done             | 40  | 32     | IFS1<8>  | IEC1<8>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1TX – UART1 Transfer Done            | 41  | 32     | IFS1<9>  | IEC1<9>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| I2C1B – I2C1 Bus Collision Event      | 42  | 33     | IFS1<10> | IEC1<10>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1S – I2C1 Slave Event              | 43  | 33     | IFS1<11> | IEC1<11>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1M – I2C1 Master Event             | 44  | 33     | IFS1<12> | IEC1<12>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNA – PORTA Input Change<br>Interrupt | 45  | 34     | IFS1<13> | IEC1<13>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNB – PORTB Input Change<br>Interrupt | 46  | 34     | IFS1<14> | IEC1<14>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNC – PORTC Input Change<br>Interrupt | 47  | 34     | IFS1<15> | IEC1<15>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMP – Parallel Master Port            | 48  | 35     | IFS1<16> | IEC1<16>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| PMPE – Parallel Master Port Error     | 49  | 35     | IFS1<17> | IEC1<17>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2E – SPI2 Fault                    | 50  | 36     | IFS1<18> | IEC1<18>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2RX – SPI2 Receive Done            | 51  | 36     | IFS1<19> | IEC1<19>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2TX – SPI2 Transfer Done           | 52  | 36     | IFS1<20> | IEC1<20>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2E – UART2 Error                     | 53  | 37     | IFS1<21> | IEC1<21>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2RX – UART2 Receiver                 | 54  | 37     | IFS1<22> | IEC1<22>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2TX – UART2 Transmitter              | 55  | 37     | IFS1<23> | IEC1<23>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2B – I2C2 Bus Collision Event      | 56  | 38     | IFS1<24> | IEC1<24>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2S – I2C2 Slave Event              | 57  | 38     | IFS1<25> | IEC1<25>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2M – I2C2 Master Event             | 58  | 38     | IFS1<26> | IEC1<26>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| CTMU – CTMU Event                     | 59  | 39     | IFS1<27> | IEC1<27>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| DMA0 – DMA Channel 0                  | 60  | 40     | IFS1<28> | IEC1<28>      | IPC10<4:2>      | IPC10<1:0>   | No         |

| DMA1 – DMA Channel 1                  | 61  | 41     | IFS1<29> | IEC1<29>      | IPC10<12:10>    | IPC10<9:8>   | No         |

| DMA2 – DMA Channel 2                  | 62  | 42     | IFS1<30> | IEC1<30>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA3 – DMA Channel 3                  | 63  | 43     | IFS1<31> | IEC1<31>      | IPC10<28:26>    | IPC10<25:24> | No         |

|                                       |     | Lowes  |          | rder Priority | E 4. ((DIOOON)) |              |            |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | ROTRI             | //<8:1>           |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |

### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

### Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

## TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 |           |        |       |       |       |        |       |      | Bi                   | ts      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------|--------|-------|-------|-------|--------|-------|------|----------------------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8                 | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16     | —      | _     | —     | _     |        | _     | _    | _                    | _       |        | -      | _      | -      | —      | _      |        | 0000       |

| 5170                        | DOITIOOIZ                       |           |        |       |       |       |        |       |      |                      |         |        | 0000   |        |        |        |        |        |            |

| 3180                        | DCH1DSIZ                        | 31:16     | _      | _     | —     | —     | —      | —     | _    | -                    | —       | —      | _      |        | _      | —      | _      | —      | 0000       |

| 5100                        | DOITIDOIZ                       | 15:0      |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16     | _      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | _      | _      | 0000       |

| 0100                        |                                 | 15:0      |        |       |       |       |        |       |      | CHSPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16     | —      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

| 017.00                      |                                 | 15:0      |        |       |       |       |        |       |      | CHDPT                | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16     | _      | _     | —     | —     | —      | —     | _    | _                    | —       | —      | _      | —      | —      | —      | —      | -      | 0000       |

| 0.20                        |                                 | 15:0      |        |       |       |       |        |       |      | CHCSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16     | _      | _     | _     | —     | —      | —     | _    | _                    | —       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.00                        |                                 | 15:0      |        |       |       |       |        |       |      | CHCPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16     | —      | _     | —     | —     | —      | —     | —    | _                    | _       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.20                        | Bonnbra                         | 15:0      | —      | _     | —     | —     | —      | —     | —    | _                    |         |        |        | CHPDA  |        |        |        |        | 0000       |

| 31F0                        | DCH2CON                         | 31:16     | —      | _     | —     | —     | —      | —     | —    | _                    |         | _      | _      | _      | _      | —      | —      |        | 0000       |

| 0.20                        |                                 |           | CHBUSY | _     | _     | —     | _      | _     |      | CHCHNS               | CHEN    | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | <1:0>  | 0000       |

| 31F0                        | DCH2ECON                        |           |        |       |       |       |        |       |      | 00FF                 |         |        |        |        |        |        |        |        |            |

|                             |                                 | 15:0      |        |       |       | CHSIR | Q<7:0> |       |      |                      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      | —      | —      | FF00       |

| 3200                        | DCH2INT                         | 31:16     | —      | —     | —     | —     | —      | —     | _    | —                    | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0      | _      | _     |       | —     | —      | —     |      |                      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16     |        |       |       |       |        |       |      | CHSSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      |                      |         |        |        |        |        |        |        |        | 0000       |

| 3220                        |                                 | 31:16     |        |       |       |       |        |       |      | CHDSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | 1                    |         |        |        |        |        |        |        |        | 0000       |

| 3230                        | DCH2SSIZ                        | 31:16     |        | —     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3240                        | DCH2DSIZ                        | 31:16     |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      | —      | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3250                        | DCH2SPTR                        | 31:16     |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHSPTI               | ≺<15:0> |        |        |        |        |        |        |        | 0000       |

| 3260                        | DCH2DPTR                        | 31:16     |        |       | —     | _     | —      | _     | _    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHDPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3270                        | DCH2CSIZ                        | 31:16     |        | _     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0      |        |       |       |       |        |       |      | CHCSI2<br>exadecimal |         |        |        |        |        |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   | —                 | —                 |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 3-1 Unimplemented: Read as '0'

### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | LSPD              | RETRYDIS          |                   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |  |

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| ======================================= |                  |                                    |                    |  |  |  |

|-----------------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit                        | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                       | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a Low-Speed device enabled

- 0 = Direct connection to a Low-Speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

NOTES:

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

## 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

## 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

## 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to "*MIPS32*<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

## TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHA        | RACTERI                   | STICS                                                               | (unless ot | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |                                |                                      |  |  |  |

|---------------|---------------------------|---------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------------------------------|--------------------------------------|--|--|--|

| Param.<br>No. | Symbol Characteristics '' |                                                                     |            | Min.                                                                                                                                                                                               | Typical | Max. | Units                          | Conditions                           |  |  |  |

| OS50          | Fplli                     | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |            | 3.92                                                                                                                                                                                               | _       | 5    | MHz                            | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |  |  |  |

| OS51          | Fsys                      | On-Chip VCO System<br>Frequency                                     |            | 60                                                                                                                                                                                                 | —       | 120  | MHz                            | _                                    |  |  |  |

| OS52          | TLOCK                     | PLL Start-up Time (Lock Time)                                       |            | _                                                                                                                                                                                                  | _       | 2    | ms                             | —                                    |  |  |  |

| OS53          | DCLK                      | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cum              | -0.25      | —                                                                                                                                                                                                  | +0.25   | %    | Measured over 100 ms<br>period |                                      |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

## TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА        | RACTERISTICS                                    | (unless | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |  |  |

|---------------|-------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Characteristics                                 |         | Typical                                                                                                                                                                                            | Max. | Units | Conditions |  |  |  |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |         |                                                                                                                                                                                                    |      |       |            |  |  |  |  |

| F20b          | FRC                                             | -0.9    |                                                                                                                                                                                                    | +0.9 | %     | _          |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

## TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА                          | RACTERISTICS    | (unless | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |  |

|---------------------------------|-----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No.                   | Characteristics |         | Typical                                                                                                                                                                                                                                                                               | Max. | Units | Conditions |  |  |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |         |                                                                                                                                                                                                                                                                                       |      |       |            |  |  |  |  |

| F21 LPRC                        |                 | -15     | —                                                                                                                                                                                                                                                                                     | +15  | %     | _          |  |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

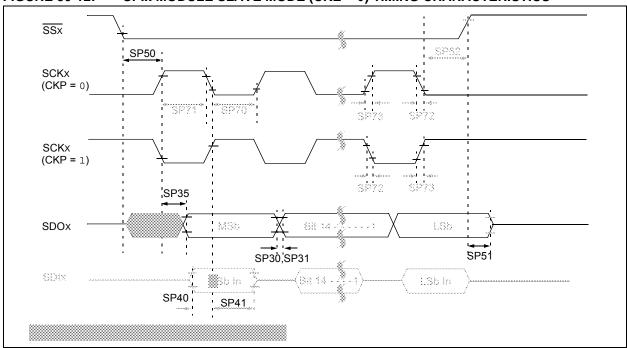

### FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

## TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | TICS                                                               | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |      |       |                    |  |  |  |

|---------------|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                          | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                       | TSCK/2                                                                                                                                                                                                        | —                   | _    | ns    | —                  |  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                      | TSCK/2                                                                                                                                                                                                        | —                   | _    | ns    | —                  |  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                               | —                                                                                                                                                                                                             | _                   |      | ns    | See parameter DO32 |  |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                               | —                                                                                                                                                                                                             | —                   | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                | —                                                                                                                                                                                                             | —                   |      | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                | _                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                       | —                                                                                                                                                                                                             | _                   | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2DoV              | SCKx Edge                                                          | —                                                                                                                                                                                                             | —                   | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10                                                                                                                                                                                                            |                     |      | ns    | —                  |  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                       | 10                                                                                                                                                                                                            | _                   | _    | ns    | —                  |  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                           |                     |      | ns    | —                  |  |  |  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>             | 5                                                                                                                                                                                                             | —                   | 25   | ns    | _                  |  |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20                                                                                                                                                                                                     | —                   |      | ns    | —                  |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

| AC CHA        | RACTERIS          | STICS           |                        | (unless other | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |                                            |  |  |  |

|---------------|-------------------|-----------------|------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------|--|--|--|

| Param.<br>No. | Symbol Characteri |                 | eristics               | Min.          | Max.                                                                                                                                                                                                                                                                                | Units | Conditions                                 |  |  |  |

| IS10          | TLO:SCL           | Clock Low Time  | 100 kHz mode           | 4.7           | —                                                                                                                                                                                                                                                                                   | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |  |

|               |                   |                 | 400 kHz mode           | 1.3           | —                                                                                                                                                                                                                                                                                   | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 0.5           | —                                                                                                                                                                                                                                                                                   | μS    | _                                          |  |  |  |

| IS11          | THI:SCL           | Clock High Time | 100 kHz mode           | 4.0           | _                                                                                                                                                                                                                                                                                   | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |  |

|               |                   |                 | 400 kHz mode           | 0.6           | _                                                                                                                                                                                                                                                                                   | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 0.5           | —                                                                                                                                                                                                                                                                                   | μS    |                                            |  |  |  |

| IS20          | TF:SCL            | SDAx and SCLx   | 100 kHz mode           | —             | 300                                                                                                                                                                                                                                                                                 | ns    | CB is specified to be from                 |  |  |  |

|               |                   | Fall Time       | 400 kHz mode           | 20 + 0.1 Св   | 300                                                                                                                                                                                                                                                                                 | ns    | 10 to 400 pF                               |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | _             | 100                                                                                                                                                                                                                                                                                 | ns    |                                            |  |  |  |

| IS21          | TR:SCL            | SDAx and SCLx   | 100 kHz mode           |               | 1000                                                                                                                                                                                                                                                                                | ns    | CB is specified to be from                 |  |  |  |

|               |                   | Rise Time       | 400 kHz mode           | 20 + 0.1 Св   | 300                                                                                                                                                                                                                                                                                 | ns    | 10 to 400 pF                               |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | —             | 300                                                                                                                                                                                                                                                                                 | ns    |                                            |  |  |  |

| IS25          | TSU:DAT           | Data Input      | 100 kHz mode           | 250           |                                                                                                                                                                                                                                                                                     | ns    | _                                          |  |  |  |

|               |                   | Setup Time      | 400 kHz mode           | 100           |                                                                                                                                                                                                                                                                                     | ns    |                                            |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 100           | —                                                                                                                                                                                                                                                                                   | ns    |                                            |  |  |  |

| IS26          | THD:DAT           | Data Input      | 100 kHz mode           | 0             |                                                                                                                                                                                                                                                                                     | ns    |                                            |  |  |  |

|               |                   | Hold Time       | 400 kHz mode           | 0             | 0.9                                                                                                                                                                                                                                                                                 | μs    |                                            |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 0             | 0.3                                                                                                                                                                                                                                                                                 | μS    |                                            |  |  |  |

| IS30          | TSU:STA           | Start Condition | 100 kHz mode           | 4700          | —                                                                                                                                                                                                                                                                                   | ns    | Only relevant for Repeated                 |  |  |  |

|               |                   | Setup Time      | 400 kHz mode           | 600           | —                                                                                                                                                                                                                                                                                   | ns    | Start condition                            |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 250           | —                                                                                                                                                                                                                                                                                   | ns    |                                            |  |  |  |

| IS31          | THD:STA           | Start Condition | 100 kHz mode           | 4000          |                                                                                                                                                                                                                                                                                     | ns    | After this period, the first               |  |  |  |

|               |                   | Hold Time       | 400 kHz mode           | 600           | —                                                                                                                                                                                                                                                                                   | ns    | clock pulse is generated                   |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 250           | —                                                                                                                                                                                                                                                                                   | ns    |                                            |  |  |  |

| IS33          | Tsu:sto           | Stop Condition  | 100 kHz mode           | 4000          |                                                                                                                                                                                                                                                                                     | ns    |                                            |  |  |  |

|               |                   | Setup Time      | 400 kHz mode           | 600           |                                                                                                                                                                                                                                                                                     | ns    | ]                                          |  |  |  |

|               |                   |                 | 1 MHz mode<br>(Note 1) | 600           |                                                                                                                                                                                                                                                                                     | ns    |                                            |  |  |  |

## TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

# 31.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 30.0** "Electrical Characteristics", with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 30.0** "**Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      |                          |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               |                          |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

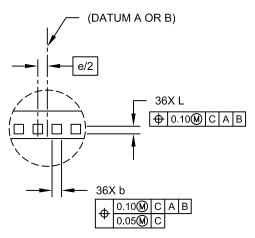

## 33.1 Package Marking Information (Continued)

## 44-Lead VTLA

## 44-Lead QFN

## 44-Lead TQFP

Example

## Example

## Example

## Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3) |