#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 010                      |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f064b-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 27                | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |

| AN6      | _                 | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

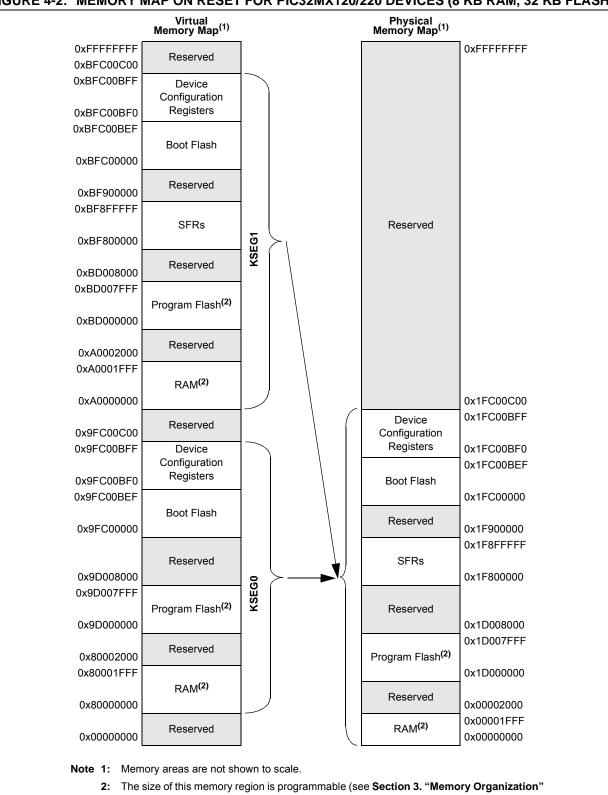

### FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX120/220 DEVICES (8 KB RAM, 32 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | ROTRI             | //<8:1>           |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

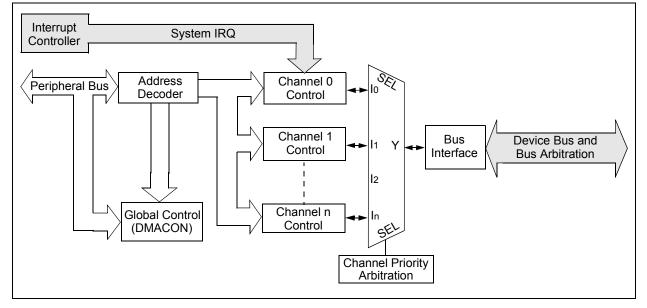

### 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

### FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

### TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP

| ess                         |                                 |           |             |            |            |             |             |            |            | Bi          | its      |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------------|------------|------------|-------------|-------------|------------|------------|-------------|----------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15       | 30/14      | 29/13      | 28/12       | 27/11       | 26/10      | 25/9       | 24/8        | 23/7     | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                        | DCH0CON                         | 31:16     | _           | _          | _          | —           | _           |            | _          | —           | _        | _      | _      | —      | _       | _      |        | -      | 0000       |

| 3000                        | DCHUCON                         | 15:0      | CHBUSY      | _          | —          | —           | —           |            | —          | CHCHNS      | CHEN     | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16     | _           | _          | —          |             |             | _          | —          | —           |          | •      |        | CHAIR  | Q<7:0>  |        |        |        | 00FF       |

| 3070                        | Denieleon                       | 15:0      |             |            |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | _      |        | FF00       |

| 3080                        | DCH0INT                         | 31:16     | —           | _          | —          | —           | —           | _          | —          | —           | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5000                        | DCHOINT                         | 15:0      | _           | _          | —          | —           | —           | _          | —          | —           | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16     |             |            |            |             |             |            |            | СНАЗА       | <31:0>   |        |        |        |         |        |        |        | 0000       |

| 0000                        | Donooon                         | 15:0      |             |            |            |             |             |            |            | 01100/      | ( 101.04 |        |        |        |         |        |        |        | 0000       |

| 3040                        | DCH0DSA                         | 31:16     |             |            |            |             |             |            |            | CHDSA       | \<31·0>  |        |        |        |         |        |        |        | 0000       |

| 3070                        | DOI 10DOA                       | 15:0      |             |            |            |             |             |            |            | 01100/      | 1.02     |        |        |        |         |        |        |        | 0000       |

| 30B0                        | DCH0SSIZ                        | 31:16     | —           | —          | —          | —           |             | _          | —          | —           | —        | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                        | DOI100012                       | 15:0      |             |            |            |             |             |            |            | CHSSIZ      | Z<15:0>  |        |        |        |         |        |        |        | 0000       |

| 3000                        | DCH0DSIZ                        | 31:16     | _           | —          | —          | —           | —           | —          | —          | —           | —        | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0000                        | DOMODOL                         | 15:0      |             |            |            |             |             |            |            | CHDSIZ      | Z<15:0>  | -      |        |        |         |        |        |        | 0000       |

| 3000                        | DCH0SPTR                        | 31:16     | —           | —          | —          | —           |             | _          | —          | —           | —        | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                        | Donioor IIX                     | 15:0      |             |            |            |             |             |            |            | CHSPTI      | R<15:0>  |        |        |        |         |        |        |        | 0000       |

| 30E0                        | DCH0DPTR                        | 31:16     | _           | _          | —          | —           |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| OOLO                        |                                 | 15:0      |             |            |            |             |             |            |            | CHDPT       | R<15:0>  |        |        |        |         |        |        |        | 0000       |

| 30E0                        | DCH0CSIZ                        | 31:16     | _           | _          | —          | —           |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 001 0                       | DOI100012                       | 15:0      |             |            |            |             |             |            |            | CHCSIZ      | Z<15:0>  |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16     | _           | _          | —          | —           |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0100                        | Donioor IIX                     | 15:0      |             |            |            |             |             |            |            | CHCPT       | R<15:0>  |        |        |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16     |             | _          | —          |             |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0110                        | DOITODAT                        | 15:0      | —           | —          | —          |             |             |            | —          | —           |          |        |        | CHPDA  | \T<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16     |             | _          | —          |             |             |            | —          | —           | —        | —      | —      |        | —       | —      |        | —      | 0000       |

| 0120                        | Donnoon                         | 15:0      | CHBUSY      | —          | —          |             |             |            | —          | CHCHNS      | CHEN     | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16     | —           | _          | —          | —           | —           | -          | —          | —           |          |        |        | CHAIR  | Q<7:0>  |        |        |        | OOFF       |

| 5150                        | DOITILOON                       | 15:0      |             |            |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | _      | FF00       |

| 3140                        | DCH1INT                         | 31:16     | _           | _          | —          |             |             | _          | —          | —           | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5140                        | DOLLING                         | 15:0      | _           | _          | _          | _           | —           | _          | _          | —           | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16     | 1:16 0000   |            |            |             |             |            |            |             |          |        |        |        |         |        |        |        |            |

| 5150                        | DOITIOGA                        | 15:0      | 5:0         |            |            |             |             |            |            |             |          |        |        |        |         |        |        |        |            |

| 3160                        | DCH1DSA                         | 31:16     | CHDSA<31:0> |            |            |             |             |            |            |             |          |        |        |        |         |        |        |        |            |

| 3100                        | DONIDSA                         | 15:0      |             |            |            |             |             |            |            |             | ~~~~     |        |        |        |         |        |        |        | 0000       |

| Leger                       | od∙ v=u                         | nknown    | value on R  | leset: — = | unimplemer | nted read a | s '0' Reset | values are | shown in h | nexadecimal |          |        |        |        |         |        |        |        |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | S    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7.0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |  |  |  |

### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24              | _                 | —                 | -                 | —                 | -                 | —                 | —                | —                |  |  |  |  |

| 22:16              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16              | -                 | _                 |                   | —                 | -                 |                   |                  | —                |  |  |  |  |

| 15:8               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0               | _                 | —                 | _                 | —                 | -                 | —                 | —                | —                |  |  |  |  |

| 7:0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0 BDTPTRH<23:16> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

### REGISTER 10-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

| REGIOT             | Constent 10-19. OTBOTTS. OSB BOTTEN DESCRIPTON TABLE FAGE 5 REGISTEN |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------------|----------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range       | Bit<br>31/23/15/7                                                    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 31:24              | U-0                                                                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24              | —                                                                    | —                 |                   |                   | _                 | _                 | —                | —                |  |  |  |  |

| 23:16              | U-0                                                                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10              | _                                                                    |                   |                   |                   |                   |                   | _                | _                |  |  |  |  |

| 15:8               | U-0                                                                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0               | —                                                                    | _                 |                   |                   |                   | -                 | —                | —                |  |  |  |  |

| 7:0                | R/W-0                                                                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0 BDTPTRU<31:24> |                                                                      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

### REGISTER 10-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRU<31:24>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

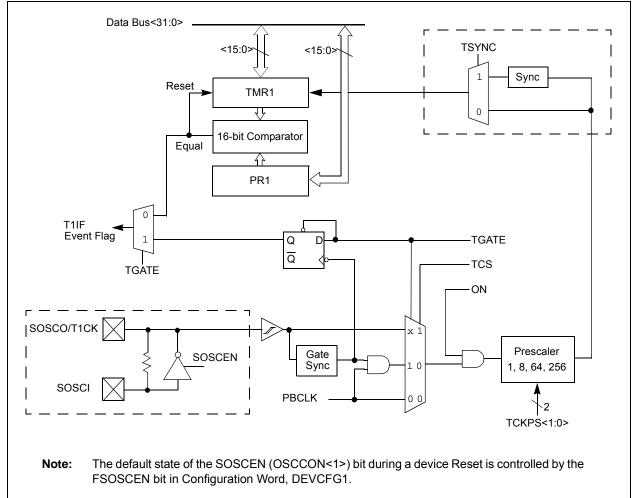

### 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

### 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

### PIC32MX1XX/2XX 28/36/44-PIN FAMILY

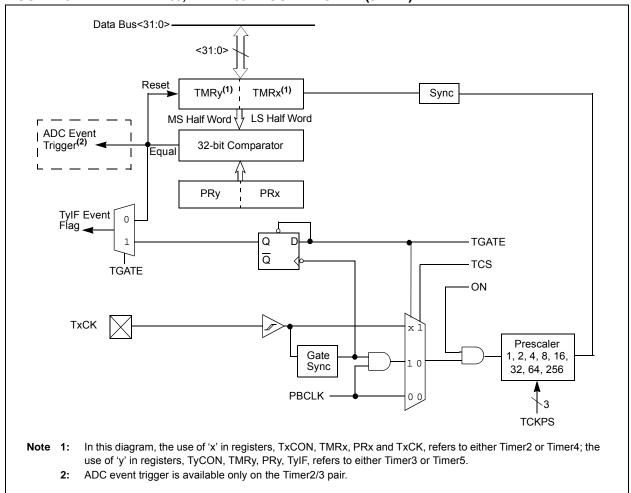

### FIGURE 13-2: TIMER2/3, TIMER4/5 BLOCK DIAGRAM (32-BIT)

### 16.1 Output Compare Control Registers

### TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| Bits                        |                                 |                   |             |            |       |       |       |       |      |       |          |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|-------------------|-------------|------------|-------|-------|-------|-------|------|-------|----------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15       | 30/14      | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7     | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16             | —           | —          | —     | —     | —     | —     | —    | _     | —        | —    | —    | —     | —      | _    | —        | _    | 0000         |

| 0000                        | 001001                          | 15:0              | ON          | —          | SIDL  | —     | —     | —     |      | —     | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0     |             |            |       |       |       |       |      | OC1R  | <31:0>   |      |      |       |        |      |          |      | xxxx         |

| 3020                        | OC1RS                           | 31:16<br>15:0     |             |            |       |       |       |       |      | OC1RS | \$<31:0> |      |      |       |        |      |          |      | xxxx         |

| 0000                        | 00000                           | 31:16             | —           | _          | _     | _     | _     | _     |      | _     | —        | —    | _    | —     | —      | —    | —        | —    | 0000         |

| 3200                        | OC2CON                          | 15:0              | ON          | _          | SIDL  | _     | _     | _     | _    | _     | _        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3210                        | OC2R                            | 31:16             | OC2R<31:0>  |            |       |       |       |       |      |       |          |      |      |       |        |      |          |      |              |

| 3210                        | UCZR                            | 15:0              | UC2R<31:0>  |            |       |       |       |       |      |       |          |      |      |       |        |      |          |      |              |

| 31:16                       |                                 |                   |             |            |       |       |       |       | XXXX |       |          |      |      |       |        |      |          |      |              |

| 3220                        | OC2RS                           | 15:0              | OC2RS<31:0> |            |       |       |       |       |      |       |          |      |      |       |        |      |          |      |              |

| 3400                        | OC3CON                          | 31:16             | _           | _          | _     | _     | _     | _     | _    | _     | _        | _    | _    | _     | —      |      | —        |      | 0000         |

| 3400                        | 003001                          | 15:0              | ON          | _          | SIDL  | _     | _     | _     | _    | _     | -        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0     |             |            |       |       |       |       |      | OC3R  | <31:0>   |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16             |             |            |       |       |       |       |      |       |          |      |      | XXXX  |        |      |          |      |              |

| 3420                        | 00383                           | 15:0              | 5:0         |            |       |       |       |       |      |       |          |      |      | XXXX  |        |      |          |      |              |

| 3600                        | OC4CON                          | 31:16             | —           | _          | _     | _     | _     | _     | _    | _     | —        | —    | _    | —     | —      |      | —        | _    | 0000         |

| 3000                        |                                 | 15:0              | ON          | _          | SIDL  | _     | _     | _     | _    | _     | -        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16             |             | OC4R<31:0> |       |       |       |       |      |       |          |      |      |       | XXXX   |      |          |      |              |

| 3010                        | 004R                            | 15:0              |             |            |       |       |       |       |      |       |          |      | xxxx |       |        |      |          |      |              |

| 3620                        | OC4RS                           | 31:16             |             |            |       |       |       |       |      | OC4RS | 221.05   |      |      |       |        |      |          |      | xxxx         |

| 3020                        |                                 | 15:0              |             |            |       |       |       |       |      | 00400 | 0<01.02  |      |      |       |        |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16             | -           | _          | —     | _     | _     | _     | _    | _     | -        | _    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | UCSCON                          | 15:0              | ON          | _          | SIDL  | _     | —     | —     | _    | —     | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16             |             |            |       |       |       |       |      | OC5R  | <31.0>   |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0000                            | 15:0              |             |            |       |       |       |       |      | OUJK  | -01.02   |      |      |       |        |      |          |      | xxxx         |

| 3820                        | OC5RS                           | 31:16             |             |            |       |       |       |       |      | OC5RS |          |      |      |       |        |      |          |      | XXXX         |

| 3020                        | 00010                           | 15 <sup>.</sup> 0 |             |            |       |       |       |       |      | 00000 | -01.02   |      |      |       |        |      |          |      | xxxx         |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        | —                 | —                 | —                 |                   | R                 | XBUFELM<4:(       | )>               |                  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | —                 | —                 | —                 |                   | Tک                | KBUFELM<4:0       | )>               |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         | —                 | —                 | —                 | FRMERR            | SPIBUSY           | —                 | _                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            |                   | SPITBF           | SPIRBF           |

### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware               |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

### PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

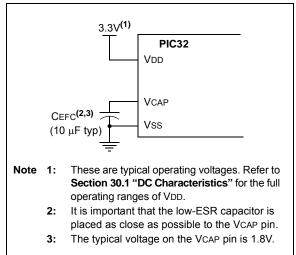

### 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

### 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

### 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

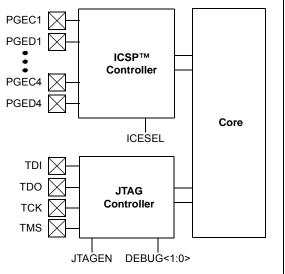

### 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC CHA                                    | RACTERIS | TICS  | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                                      |                                        |  |  |  |

|-------------------------------------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|--|--|--|

| Param.<br>No. Typical <sup>(2)</sup> Max. |          | Units | Conditions                                                                                                                                                                                                                                                                 |                                                      |                                        |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5)     |          |       |                                                                                                                                                                                                                                                                            |                                                      |                                        |  |  |  |

| DC40k                                     | 44       | 70    | μA                                                                                                                                                                                                                                                                         | -40°C                                                |                                        |  |  |  |

| DC40I                                     | 44       | 70    | μA                                                                                                                                                                                                                                                                         | +25°C                                                | Base Power-Down Current                |  |  |  |

| DC40n                                     | 168      | 259   | μA                                                                                                                                                                                                                                                                         | +85°C                                                |                                        |  |  |  |

| DC40m                                     | 335      | 536   | μA                                                                                                                                                                                                                                                                         | +105°C                                               |                                        |  |  |  |

| Module Differential Current               |          |       |                                                                                                                                                                                                                                                                            |                                                      |                                        |  |  |  |

| DC41e                                     | 5        | 20    | μA                                                                                                                                                                                                                                                                         | 3.6V                                                 | Watchdog Timer Current: AlWDT (Note 3) |  |  |  |

| DC42e                                     | 23       | 50    | μA                                                                                                                                                                                                                                                                         | 3.6V RTCC + Timer1 w/32 kHz Crystal: △IRTCC (Note 3) |                                        |  |  |  |

| DC43d                                     | 1000     | 1100  | μA                                                                                                                                                                                                                                                                         | 3.6V                                                 | ADC: Aladc (Notes 3,4)                 |  |  |  |

### TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

### 31.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 30.0** "Electrical Characteristics", with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 30.0** "**Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

### Absolute Maximum Ratings

### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      |                          |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               |                          |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

### **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

### TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |