#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f064b-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                         | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                      |                                                                                      |

|----------|-------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------------|--------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN           | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                          |

| MCLR     | 26                      | 1                                 | 32                  | 18                              | I/P         | ST                   | Master Clear (Reset) input. This pin is an active-low Reset to the device.           |

| AVDD     | 25                      | 28                                | 31                  | 17                              | Р           | _                    | Positive supply for analog modules. This pin must be connected at all times.         |

| AVss     | 24                      | 27                                | 30                  | 16                              | Р           | —                    | Ground reference for analog modules                                                  |

| Vdd      | 10                      | 13                                | 5, 13, 14,<br>23    | 28, 40                          | Р           | _                    | Positive supply for peripheral logic and<br>I/O pins                                 |

| VCAP     | 17                      | 20                                | 22                  | 7                               | Р           | —                    | CPU logic filter capacitor connection                                                |

| Vss      | 5, 16                   | 8, 19                             | 6, 12, 21           | 6, 29, 39                       | Р           | _                    | Ground reference for logic and I/O pins.<br>This pin must be connected at all times. |

| VREF+    | 27                      | 2                                 | 33                  | 19                              | I           | Analog               | Analog voltage reference (high) input                                                |

| VREF-    | 28                      | 3                                 | 34                  | 20                              | I           | Analog               | Analog voltage reference (low) input                                                 |

| Legend:  | CMOS = CM<br>ST = Schmi |                                   | •                   |                                 |             | Analog =<br>O = Outp | Analog input P = Power<br>ut I = Input                                               |

#### TADI E 4 4. DINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

| . , .     |

|-----------|

| P = Powe  |

| l = Input |

| — = N/A   |

|           |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming™ (ICSP™)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively). NOTES:

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

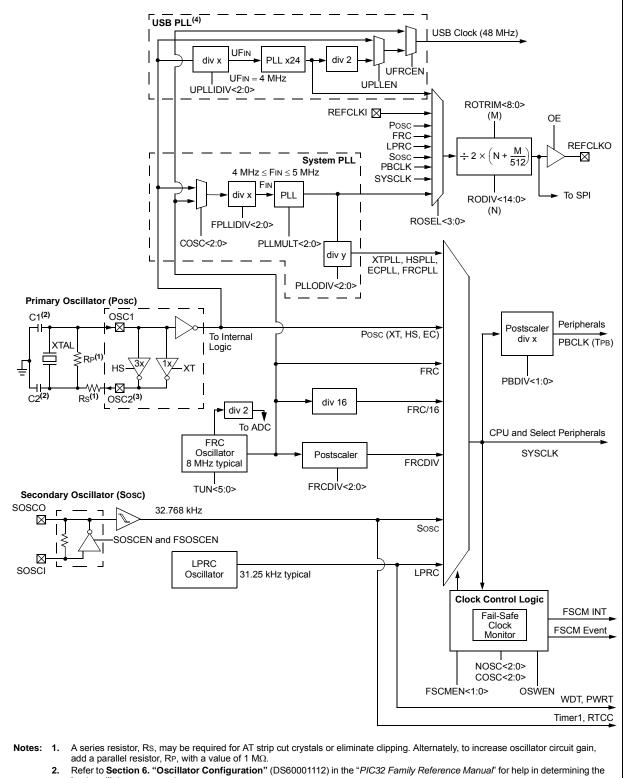

#### FIGURE 8-1: OSCILLATOR DIAGRAM

Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determinin best oscillator components.

3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

4. The USB PLL is only available on PIC32MX2XX devices.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

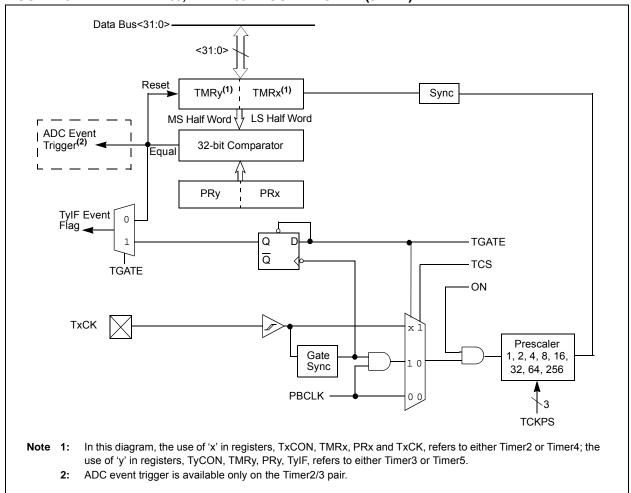

#### FIGURE 13-2: TIMER2/3, TIMER4/5 BLOCK DIAGRAM (32-BIT)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | -                 | -                 | _                 | _                 | -                | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             | ICM<2:0>          |                  |                  |

#### REGISTER 15-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

## Legend:

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit |                  |

|--------------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = unkn | own)             | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                    |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                                                           |

|           | <ul> <li>1 = Halt in Idle mode</li> <li>0 = Continue to operate in Idle mode</li> </ul>                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                                               |

|           | 1 = Capture rising edge first                                                                                                                                                            |

|           | 0 = Capture falling edge first                                                                                                                                                           |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                                                           |

|           | 1 = 32-bit timer resource capture                                                                                                                                                        |

|           | 0 = 16-bit timer resource capture                                                                                                                                                        |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                                                    |

|           | 0 = Timer3 is the counter source for capture                                                                                                                                             |

|           | 1 = Timer2 is the counter source for capture                                                                                                                                             |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                    |

|           | 01 = Interrupt on every second capture event                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                    |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                 |

|           | 1 = Input capture overflow has occurred                                                                                                                                                  |

|           | 0 = No input capture overflow has occurred                                                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                                             |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                        |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

|           | STOCEN Gyole infinediately following the instruction that deals the module's ON bit.                                                                                                     |

NOTES:

### 17.1 SPI Control Registers

#### TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| ess                         |                                 | Ċ,        |                 |         |        |              |              |              |           | Bi     | ts      |        |        |        |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|-----------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|--------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15           | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN           | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —      | _      | -      | —           | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SPITCON                         |           | ON              | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | —               | _       | _      |              | RXE          | BUFELM<4:    | 0>        |        | —       | —      | -      |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| 5610                        |                                 | 15:0      | _               | —       | —      | FRMERR       | SPIBUSY      | —            | —         | SPITUR | SRMT    | SPIROV | SPIRBE | —      | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI1BUF                         | 31:16     |                 |         |        |              |              |              |           | DATA<  | 31.0>   |        |        |        |             |          |        |         | 0000       |

| 3020                        |                                 | 15:0      |                 |         |        |              |              |              |           | Brance | .01.0   |        |        |        |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | —               | —       | _      | —            | —            | —            | —         | —      | —       | —      | —      | —      | —           | —        | —      | —       | 0000       |

| 0000                        |                                 | 15:0      | — — — BRG<12:0> |         |        |              |              |              |           |        |         |        | 0000   |        |             |          |        |         |            |

|                             |                                 | 31:16     | —               | —       | —      | —            | —            | —            | —         | —      | —       | —      | _      | _      | —           | _        | —      | —       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT   | —       |        | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | -      | -      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN           | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —      |        |        | _           |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 3F1200N                         | 15:0      | ON              | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5410                        | SPI2STAT                        | 31:16     | —               | _       |        |              | RXE          | BUFELM<4:    | 0>        |        | _       | -      |        |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _               | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16     |                 |         |        |              |              |              |           | DATA<  | 31.0>   |        |        |        |             |          |        |         | 0000       |

| 5420                        |                                 | 15:0      |                 |         |        |              |              |              |           | Brance |         |        |        |        |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | —               | —       | _      | —            | —            | —            | —         | —      | —       | —      | —      | —      | —           | —        | —      | —       | 0000       |

| 15:0 BRG<12:0>              |                                 |           |                 |         |        |              |              |              | 0000      |        |         |        |        |        |             |          |        |         |            |

|                             |                                 | 31:16     | —               | —       | —      | _            | —            | _            | —         | —      | —       | —      | _      | —      | —           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT   | —       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | _      | _      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### 18.1 I2C Control Registers

## TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |              |            |                  |              |              |                  |              | Bi                  | ts               |            |                |              |           |          |           |          |            |

|-----------------------------|---------------------------------|---------------|--------------|------------|------------------|--------------|--------------|------------------|--------------|---------------------|------------------|------------|----------------|--------------|-----------|----------|-----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14      | 29/13            | 28/12        | 27/11        | 26/10            | 25/9         | 24/8                | 23/7             | 22/6       | 21/5           | 20/4         | 19/3      | 18/2     | 17/1      | 16/0     | All Resets |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON      |            | —<br>SIDL        | —<br>SCLREL  | —<br>STRICT  | —<br>A10M        | —<br>DISSLW  | —<br>SMEN           | —<br>GCEN        | —<br>STREN | —<br>ACKDT     | —<br>ACKEN   | —<br>RCEN | —<br>PEN | —<br>RSEN | —<br>SEN | 0000       |

|                             | 100 10717                       | 31:16         | _            | _          | _                | _            | _            | _                | _            | _                   | _                | _          | _              | _            | _         | _        | _         | _        | 0000       |

| 5010                        | I2C1STAT                        | 15:0          | ACKSTAT      | TRSTAT     | _                | _            | _            | BCL              | GCSTAT       | ADD10               | IWCOL            | I2COV      | D_A            | Р            | S         | R_W      | RBF       | TBF      | 0000       |

| 5000                        | I2C1ADD                         | 31:16         | _            | _          | _                | —            | —            | -                | —            | _                   | —                | _          | _              | _            | -         | _        | _         | _        | 0000       |

| 5020                        | IZCIADD                         | 15:0          | _            | —          | _                | —            | —            | _                |              |                     |                  |            | Address        | Register     |           |          |           |          | 0000       |

| 5030                        | I2C1MSK                         | 31:16         | _            | _          |                  | -            | -            |                  | —            | _                   | _                | _          |                | _            |           | _        | _         | _        | 0000       |

| 5050                        | 130 12C1MSK 15:0                |               |              |            | -                | -            |              |                  |              |                     |                  | Address Ma | ask Register   | ſ            |           |          |           | 0000     |            |

| 5040                        | 5040 I2C1BRG                    |               | _            | —          | _                |              | _            | —                | —            | —                   | _                | —          | _              | —            | —         | —        | —         | —        | 0000       |

| Baud Rate Gener             |                                 |               |              |            | nerator Register |              |              |                  |              |                     |                  |            |                |              |           |          |           |          |            |

| 5050                        | 5050 I2C1TRN                    |               | —            | —          | —                | —            | —            | —                | —            | —                   | —                | —          | —              | —            | —         |          | —         | —        | 0000       |

|                             |                                 | 15:0          | _            | —          | _                | —            | —            | _                | —            | — Transmit Register |                  |            |                |              |           |          |           | 0000     |            |

| 5060                        | I2C1RCV                         | 31:16         | _            | _          |                  |              |              |                  |              | _                   | _                | —          |                | —            | —         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | _            | —          |                  |              | —            |                  | —            | _                   | Receive Register |            |                |              |           |          |           |          | 0000       |

| 5100                        | I2C2CON                         | 31:16         | _            | —          | _                | —            | —            | _                | —            | _                   | —                | —          | _              | —            | _         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | ON           | _          | SIDL             | SCLREL       | STRICT       | A10M             | DISSLW       | SMEN                | GCEN             | STREN      | ACKDT          | ACKEN        | RCEN      | PEN      | RSEN      | SEN      | 1000       |

| 5110                        | I2C2STAT                        | 31:16         | -            | -          |                  |              |              | -                | —            | -                   | -                | —          | —              | -            | _         | _        | -         | -        | 0000       |

|                             |                                 |               | ACKSTAT      | TRSTAT     |                  | —            | —            | BCL              | GCSTAT       | ADD10               | IWCOL            | I2COV      | D_A            | Р            | S         | R_W      | RBF       | TBF      | 0000       |

| 5120                        | I2C2ADD                         | 31:16         | _            | _          | —                | _            | _            | _                | _            | _                   | _                | _          |                | —            | -         | _        |           | _        | 0000       |

|                             |                                 | 15:0<br>31:16 |              |            |                  |              |              |                  |              |                     |                  |            | Address        | Register     |           |          |           |          | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _            |            | _                |              |              |                  | _            | _                   | _                | _          | <br>Addross Mr | ask Register | -         | _        | _         | _        | 0000       |

|                             |                                 | 31:16         | _            | _          |                  |              | _            | _                |              |                     |                  |            |                |              | _         |          |           | _        | 0000       |

| 5140 I2C2BRG 15:0           |                                 |               |              |            |                  |              | Bai          | I<br>Id Rate Ger | erator Reg   | ister               |                  |            |                |              | 0000      |          |           |          |            |

|                             |                                 | 31:16         | _            | _          | _                |              | _            | _                | _            | _                   |                  | _          | _              | _            | _         |          | _         | _        | 0000       |

| 5150                        | I2C2TRN                         | 15:0          | _            | _          | _                | _            | _            | _                | _            | _                   |                  |            |                | Transmit     | Register  |          |           |          | 0000       |

|                             |                                 | 31:16         | _            | _          | _                | _            | _            | _                | _            | _                   | _                | _          | _              | _            | _         |          | _         | _        | 0000       |

| 5160                        | I2C2RCV                         | 15:0          | _            | _          | _                | _            | _            | _                | _            | _                   |                  |            |                | Receive      | Register  |          |           |          | 0000       |

| Legen                       | d: x=u                          | nknow         | n value on l | Reset; — = | unimpleme        | nted, read a | as '0'. Rese | t values are     | e shown in h | exadecimal          |                  |            |                |              | •         |          |           |          |            |

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

NOTES:

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 21.24        | U-0                 | U-0                 |

| 31:24        |                   | -                 | _                 | -                 | _                 |                   | _                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | F                 | ORM<2:0>            |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           |                   | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 =Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

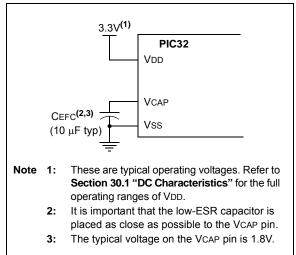

### 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

#### 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

## FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

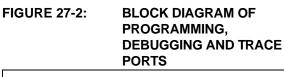

### 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

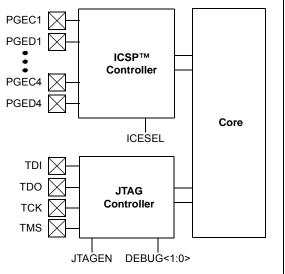

#### FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                      | rics                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: } 2.3V \ to \ 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ for \ Industrial \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \ for \ V-temp \end{array}$ |                     |      |       |                    |  |  |  |

|---------------|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>               | Min.                                                                                                                                                                                                                                                                               | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP10          | TscL                 | SCKx Output Low Time (Note 3)                | Tsck/2                                                                                                                                                                                                                                                                             | —                   | _    | ns    | _                  |  |  |  |

| SP11          | TscH                 | SCKx Output High Time (Note 3)               | Tsck/2                                                                                                                                                                                                                                                                             | —                   | _    | ns    | —                  |  |  |  |

| SP20          | TscF                 | SCKx Output Fall Time (Note 4)               | —                                                                                                                                                                                                                                                                                  | —                   | —    | ns    | See parameter DO32 |  |  |  |

| SP21          | TscR                 | SCKx Output Rise Time (Note 4)               | _                                                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                 | SDOx Data Output Fall Time (Note 4)          | _                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                 | SDOx Data Output Rise Time (Note 4)          | _                                                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2doV,            | SDOx Data Output Valid after                 |                                                                                                                                                                                                                                                                                    |                     | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2doV             | SCKx Edge                                    | _                                                                                                                                                                                                                                                                                  |                     | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP36          | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                                                                                                                                                                                                                                                 | —                   |      | ns    | _                  |  |  |  |

| SP40          | TDIV2scH,            | Setup Time of SDIx Data Input to             | 15                                                                                                                                                                                                                                                                                 | _                   | _    | ns    | VDD > 2.7V         |  |  |  |

| TDIV2scL      |                      | SCKx Edge                                    | 20                                                                                                                                                                                                                                                                                 | _                   |      | ns    | VDD < 2.7V         |  |  |  |

| SP41          | TscH2DIL,            | Hold Time of SDIx Data Input                 | 15                                                                                                                                                                                                                                                                                 | _                   | _    | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2DIL             | to SCKx Edge                                 | 20                                                                                                                                                                                                                                                                                 | _                   |      | ns    | VDD < 2.7V         |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| AC CHARACTERISTICS |           |                                                                      |         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |       |                                                           |  |

|--------------------|-----------|----------------------------------------------------------------------|---------|------------------------------------------------------|---------|-------|-----------------------------------------------------------|--|

| Param.<br>No.      | Symbol    | Characteristics                                                      | Min.    | Typical <sup>(1)</sup>                               | Max.    | Units | Conditions                                                |  |

| Clock P            | arameters | S                                                                    | •       | •                                                    |         |       | ·                                                         |  |

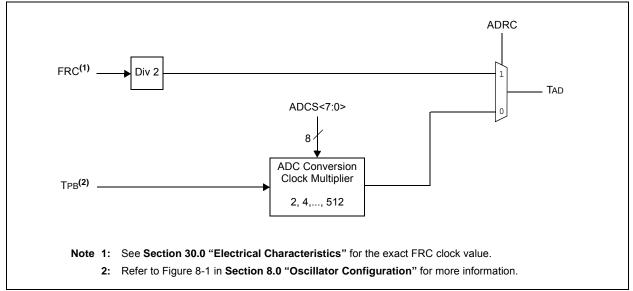

| AD50               | TAD       | ADC Clock Period <sup>(2)</sup>                                      | 65      | _                                                    | —       | ns    | See Table 30-35                                           |  |

| Convers            | sion Rate |                                                                      |         |                                                      |         |       | ·                                                         |  |

| AD55               | TCONV     | Conversion Time                                                      | _       | 12 Tad                                               | —       | _     | —                                                         |  |

| AD56               | FCNV      | Throughput Rate<br>(Sampling Speed)                                  | _       | —                                                    | 1000    | ksps  | AVDD = 3.0V to 3.6V                                       |  |

|                    |           |                                                                      | —       | —                                                    | 400     | ksps  | AVDD = 2.5V to 3.6V                                       |  |

| AD57               | TSAMP     | Sample Time                                                          | 1 Tad   | —                                                    | —       | —     | TSAMP must be $\geq$ 132 ns                               |  |

| Timing             | Paramete  | rs                                                                   |         |                                                      |         |       |                                                           |  |

| AD60               | TPCS      | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               | _       | 1.0 Tad                                              |         | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |  |

| AD61               | TPSS      | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 Tad | —                                                    | 1.5 Tad | _     | —                                                         |  |

| AD62               | TCSS      | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | —       | 0.5 Tad                                              | —       |       | _                                                         |  |

| AD63               | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _       | _                                                    | 2       | μS    | —                                                         |  |

#### TABLE 30-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

NOTES:

### 33.1 Package Marking Information (Continued)

#### 44-Lead VTLA

#### 44-Lead QFN

#### 44-Lead TQFP

Example

#### Example

## Example

## Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3) |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                                                                                          | can be found on the outer packaging for this package.                                                                                                                                                                                                                                                               |

| Note:  | If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                     |

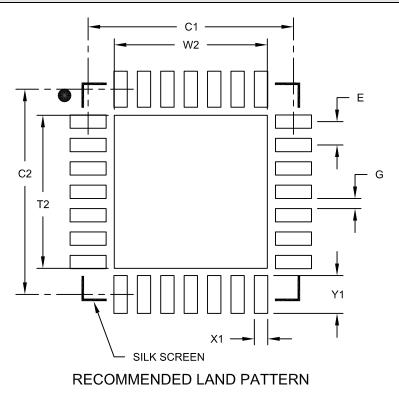

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimensi                    | MIN         | NOM  | MAX      |      |

| Contact Pitch              | Е           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 4.25 |

| Optional Center Pad Length | T2          |      |          | 4.25 |

| Contact Pad Spacing        | C1          |      | 5.70     |      |

| Contact Pad Spacing        | C2          |      | 5.70     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.37 |

| Contact Pad Length (X28)   | Y1          |      |          | 1.00 |

| Distance Between Pads      | G           | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

## APPENDIX A: REVISION HISTORY

## Revision A (May 2011)

This is the initial released version of this document.

## **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX130F064C

- PIC32MX130F064D

- PIC32MX150F128B

- PIC32MX150F128CPIC32MX150F128D

- PIC32MX250F128C

PIC32MX250F128D

PIC32MX230F064B

PIC32MX230F064C

PIC32MX230F064D

PIC32MX250F128B

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

| Section                                                                    | Update Description                                                                                                                                                        |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |  |  |

| and Graphics Interfaces, USB, and Advanced Analog"                         | Added the SPDIP package reference (see Table 1, Table 2, and " <b>Pin Diagrams</b> ").                                                                                    |  |  |

|                                                                            | Added the new devices to the applicable pin diagrams.                                                                                                                     |  |  |

|                                                                            | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |  |  |

| 1.0 "Device Overview"                                                      | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |  |  |

|                                                                            | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |  |  |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"          | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |  |  |

#### TABLE A-1: MAJOR SECTION UPDATES