Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f064b-v-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

• VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

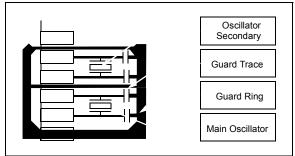

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |

|---------------------------|-----------|-----------------|

| Peripheral                | Base      | Offset<br>Start |

| Watchdog Timer            |           | 0x0000          |

| RTCC                      |           | 0x0200          |

| Timer1-5                  |           | 0x0600          |

| Input Capture 1-5         |           | 0x2000          |

| Output Compare 1-5        |           | 0x3000          |

| IC1 and IC2               |           | 0x5000          |

| SPI1 and SPI2             |           | 0x5800          |

| UART1 and UART2           |           | 0x6000          |

| PMP                       |           | 0x7000          |

| ADC                       | 0xBF80    | 0x9000          |

| CVREF                     |           | 0x9800          |

| Comparator                |           | 0xA000          |

| CTMU                      |           | 0xA200          |

| Oscillator                |           | 0xF000          |

| Device and Revision ID    |           | 0xF220          |

| Peripheral Module Disable |           | 0xF240          |

| Flash Controller          |           | 0xF400          |

| Reset                     |           | 0xF600          |

| PPS                       |           | 0xFA04          |

| Interrupts                |           | 0x1000          |

| Bus Matrix                |           | 0x2000          |

| DMA                       | 0xBF88    | 0x3000          |

| USB                       |           | 0x5050          |

| PORTA-PORTC               |           | 0x6000          |

| Configuration             | 0xBFC0    | 0x0BF0          |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

# **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

## **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

## TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | —         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | —     | _     | _     | —     | _     | —    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |       |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         | •        | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —     |       | _     |       |       | _    | _    | _     | —        | _     | —        | —      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | OIBDIF3                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTRI  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        | UTCNI UT                        | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | _     | —     | _     | —    | _    | —     | —        | —     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     |       | —     | —     | —     | —    |      |       | —        | _     |          | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —     | —     | —     | —     |       | —    | —    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —     | —     | —     | —     |       | —    | —    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | —     | _     | —     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | -     | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

# 11.4 Ports Control Registers

# TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |                          |                       | Bits                    | 6                       |      |      |          |          |          |          |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-----------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                  | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       |      | _    | _        | _        | —        | —        | _        | 0000       |

|                             |                                 | 15:0      | _     | —     | —     | —     | —     | -                        |                       |                         | —                       | _    | _    | —        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | —     | —     | —     | —     | —                        |                       |                         | —                       | _    | _    |          | —        | _        | _        | —        | 0000       |

| 0010                        |                                 | 15:0      | —     | —     | —     | —     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup> | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | —    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | —     | —     | —     | —     | _     | —                        | —                     | _                       | —                       | _    | —    |          |          |          |          |          | 0000       |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | _     | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>    | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | —    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | LATA                            | 31:16     | _     | —     | —     | —     | _     |                          | _                     | _                       | —                       | —    | —    | _        | _        | _        |          | _        | 0000       |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | —     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>  | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | —    | —    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | —     | —     | —     | —     | —     | —                        |                       | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0040                        | ODOA                            | 15:0      | —     | —     | —     | —     | —     | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>  | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    | —    | —    | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0030                        | CINFUA                          | 15:0      | _     | _     | —     | —     | _     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup> | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | —    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 6060                        | CNPDA                           | 31:16     | —     | —     | —     | —     |       | _                        |                       |                         |                         | —    | —    |          |          | —        |          |          | 0000       |

| 0000                        | CINFDA                          | 15:0      | _     | _     | —     | —     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup> | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | —    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 6070                        | CNCONA                          | 31:16     | —     | —     | —     | —     |       | _                        |                       | _                       | _                       | —    | —    |          |          | —        |          |          | 0000       |

| 0070                        | CINCONA                         | 15:0      | ON    | —     | SIDL  | —     | _     | _                        | _                     | _                       | —                       | _    | _    | _        | —        | —        | —        | —        | 0000       |

| 6080                        | CNENA                           | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       | _    | —    | —        | _        | _        | _        | _        | 0000       |

| 0000                        | CINEINA                         | 15:0      | _     | _     | —     | —     |       | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup> | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   |      |      | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

| 6000                        | CNISTATA                        | 31:16     | _     | _     | —     | —     |       |                          |                       |                         | _                       |      | _    |          |          | —        | _        |          | 0000       |

| 0090                        | CNSTATA                         | 15:0      | _     | _     | —     | —     |       | CNSTATA10 <sup>(2)</sup> | CNSTATA9(2)           | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> |      |      | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is only available on 44-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

## bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

## REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| KEOISTE      |                      |                   |                     |                   |                    |                   |                    |                  |  |  |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 31:24        | —                    |                   | —                   | -                 | —                  | -                 | —                  | —                |  |  |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 23:16        | —                    | -                 | —                   | _                 | _                  | _                 | —                  | —                |  |  |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | —                  | —                 | —                  | —                |  |  |  |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |  |  |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> | —                 | TCS <sup>(3)</sup> | —                |  |  |  |

## REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

#### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 **TCKPS<2:0>:** Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

## 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

# REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

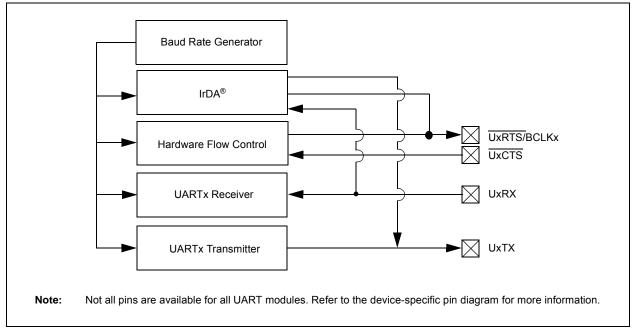

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

## FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

# 25.1 CTMU Control Registers

# TABLE 25-1: CTMU REGISTER MAP

| ess                        |                                 | 6         |         |         |          |       |          |          |          | Bits     |         |         |        |       |          |      |      |       | ú          |

|----------------------------|---------------------------------|-----------|---------|---------|----------|-------|----------|----------|----------|----------|---------|---------|--------|-------|----------|------|------|-------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11    | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5   | 20/4  | 19/3     | 18/2 | 17/1 | 16/0  | All Reset: |

| 1000                       | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |        | EDG2S | SEL<3:0> |      | —    | -     | 0000       |

| A200                       | CINUCON                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM< | <5:0> |          |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | _                | _                |  |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 23.10        | —                 | —                 | _                 | —                 | _                 |                   | -                | —                |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 15:8         |                   |                   |                   | USERID<1          | 5:8>              |                   |                  |                  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

## REGISTER 27-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUSON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDI1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Reserved: Write '1'

- bit 15-0 USERID<15:0>: User ID bits

This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG.

NOTES:

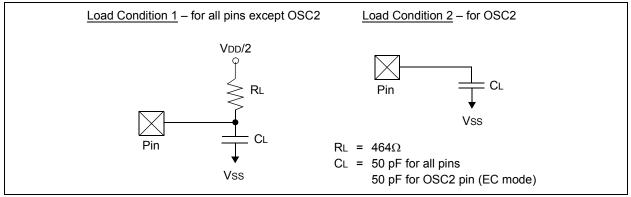

# 30.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX1XX/2XX 28/36/44-pin Family AC characteristics and timing parameters.

## FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |    |         |  |  |

|--------------------|--------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|----|---------|--|--|

| Param.<br>No.      | Symbol | Characteristics                                                              | Min.                                                                                                                                                                                                                                                                                | Typical <sup>(1)</sup> | Conditions |    |         |  |  |

| DO56               | Сю     | All I/O pins and OSC2                                                        | _                                                                                                                                                                                                                                                                                   | —                      | 50         | pF | EC mode |  |  |

| DO58               | Св     | SCLx, SDAx         —         400         pF         In I <sup>2</sup> C mode |                                                                                                                                                                                                                                                                                     |                        |            |    |         |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

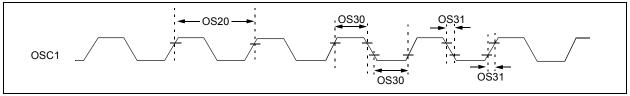

## FIGURE 30-2: EXTERNAL CLOCK TIMING

## TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHA        | RACTERI | STICS                                                               | (unless ot        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |       |       |                                      |  |  |  |

|---------------|---------|---------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|--------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristi                                                       | cs <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Typical | Max.  | Units | Conditions                           |  |  |  |

| OS50          | Fplli   | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                   | 3.92                                                                                                                                                                                                                                                                                  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |  |  |  |

| OS51          | Fsys    | On-Chip VCO Syste<br>Frequency                                      | m                 | 60                                                                                                                                                                                                                                                                                    | —       | 120   | MHz   | _                                    |  |  |  |

| OS52          | TLOCK   | PLL Start-up Time (Lock Time)                                       |                   | _                                                                                                                                                                                                                                                                                     | _       | 2     | ms    | —                                    |  |  |  |

| OS53          | DCLK    | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      |                   | -0.25                                                                                                                                                                                                                                                                                 | —       | +0.25 | %     | Measured over 100 ms<br>period       |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

# TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА        | RACTERISTICS                                    | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |  |  |

|---------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Characteristics                                 | Min.                                                                                                                                                                                                                                                                                 | Typical | Max. | Units | Conditions |  |  |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                                      |         |      |       |            |  |  |  |

| F20b          | FRC                                             | -0.9 — +0.9 % —                                                                                                                                                                                                                                                                      |         |      |       |            |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

## TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА        | RACTERISTICS                    | (unless | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |  |

|---------------|---------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Characteristics                 | Min.    | Typical                                                                                                                                                                                                                                                                                | Max. | Units | Conditions |  |  |  |  |

| LPRC @        | LPRC @ 31.25 kHz <sup>(1)</sup> |         |                                                                                                                                                                                                                                                                                        |      |       |            |  |  |  |  |

| F21           | LPRC                            | -15     | -15 — +15 % —                                                                                                                                                                                                                                                                          |      |       |            |  |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

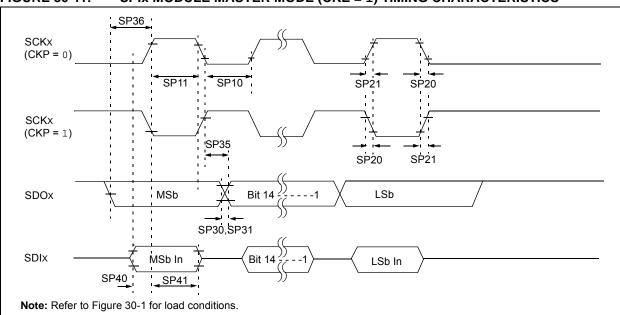

#### FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                      | rics                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                    |  |  |

|---------------|----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>               | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP10          | TscL                 | SCKx Output Low Time (Note 3)                | Tsck/2                                                | —                   | _    | ns    | _                  |  |  |

| SP11          | TscH                 | SCKx Output High Time (Note 3)               | Tsck/2                                                | —                   | _    | ns    | —                  |  |  |

| SP20          | TscF                 | SCKx Output Fall Time (Note 4)               | —                                                     | —                   | —    | ns    | See parameter DO32 |  |  |

| SP21          | TscR                 | SCKx Output Rise Time (Note 4)               | _                                                     | _                   | _    | ns    | See parameter DO31 |  |  |

| SP30          | TDOF                 | SDOx Data Output Fall Time (Note 4)          | _                                                     | —                   | _    | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                 | SDOx Data Output Rise Time (Note 4)          | _                                                     | _                   | _    | ns    | See parameter DO31 |  |  |

| SP35          | TscH2doV,            | SDOx Data Output Valid after                 |                                                       |                     | 15   | ns    | VDD > 2.7V         |  |  |

|               | TscL2doV             | SCKx Edge                                    | _                                                     |                     | 20   | ns    | VDD < 2.7V         |  |  |

| SP36          | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                    | —                   |      | ns    | _                  |  |  |

| SP40          | TDIV2scH,            | Setup Time of SDIx Data Input to             | 15                                                    | _                   | _    | ns    | VDD > 2.7V         |  |  |

|               | TDIV2scL             | SCKx Edge                                    | 20                                                    | _                   |      | ns    | VDD < 2.7V         |  |  |

| SP41          | TscH2DIL,            | Hold Time of SDIx Data Input                 | 15                                                    | _                   | _    | ns    | VDD > 2.7V         |  |  |

|               | TscL2DIL             | to SCKx Edge                                 | 20                                                    | _                   |      | ns    | VDD < 2.7V         |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

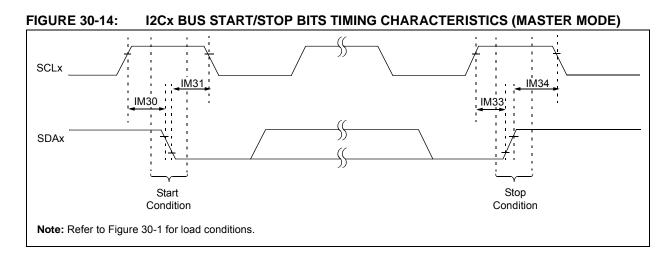

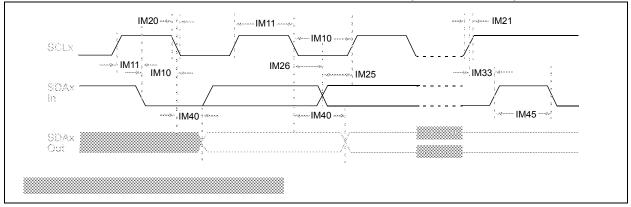

## TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS          |                               | Standard Operatin<br>(unless otherwise<br>Operating tempera | <b>stated)</b><br>iture -40 | )°C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+105°C for V-temp |

|---------------|---------|-----------------|-------------------------------|-------------------------------------------------------------|-----------------------------|------------|--------------------------------------------------------|

| Param.<br>No. | Symbol  | Charact         | eristics                      | Min. <sup>(1)</sup>                                         | Max.                        | Units      | Conditions                                             |

| IM10          | TLO:SCL | Clock Low Time  | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μs         | —                                                      |

|               |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | —                                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | _                           | μs         | _                                                      |

| IM11          | THI:SCL | Clock High Time | 100 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | —                                                      |

|               |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μs         | —                                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μs         | —                                                      |

| IM20          | TF:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 300                         | ns         | CB is specified to be                                  |

|               |         | Fall Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                         | ns         | from 10 to 400 pF                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 100                         | ns         |                                                        |

| IM21          | TR:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 1000                        | ns         | CB is specified to be                                  |

|               |         | Rise Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                         | ns         | from 10 to 400 pF                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 300                         | ns         |                                                        |

| IM25          | TSU:DAT | Data Input      | 100 kHz mode                  | 250                                                         | _                           | ns         | —                                                      |

|               |         | Setup Time      | 400 kHz mode                  | 100                                                         | —                           | ns         |                                                        |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | 100                                                         | _                           | ns         |                                                        |

| IM26          | THD:DAT | Data Input      | 100 kHz mode                  | 0                                                           | _                           | μS         | —                                                      |

|               |         | Hold Time       | 400 kHz mode                  | 0                                                           | 0.9                         | μs         |                                                        |

|               |         |                 | 1 MHz mode<br>(Note 2)        | 0                                                           | 0.3                         | μs         |                                                        |

| IM30          | TSU:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | Only relevant for                                      |

|               |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μS         | Repeated Start condition                               |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μs         | condition                                              |

| IM31          | THD:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μS         | After this period, the                                 |

|               |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μs         | first clock pulse is generated                         |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μS         | generaleu                                              |

| IM33          | Tsu:sto | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                             | μS         |                                                        |

|               |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             |                             | μs         |                                                        |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             |                             | μs         |                                                        |

| IM34          | THD:STO | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                             | ns         | —                                                      |

|               |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             |                             | ns         | ]                                                      |

|               |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | ns         |                                                        |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

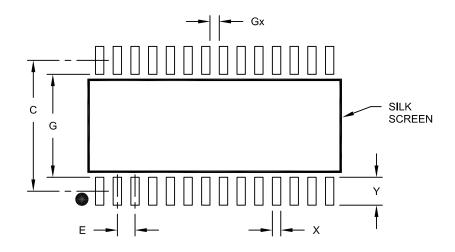

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units    |      |          |      |  |

|--------------------------|----------|------|----------|------|--|

| Dimensio                 | n Limits | MIN  | NOM      | MAX  |  |

| Contact Pitch            | E        |      | 1.27 BSC |      |  |

| Contact Pad Spacing      | С        |      | 9.40     |      |  |

| Contact Pad Width (X28)  | X        |      |          | 0.60 |  |

| Contact Pad Length (X28) | Y        |      |          | 2.00 |  |

| Distance Between Pads    | Gx       | 0.67 |          |      |  |

| Distance Between Pads    | G        | 7.40 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

# Revision J (April 2016)

This revision includes the following major changes as described in Table A-8, as well as minor updates to text and formatting, which were incorporated throughout the document.

# TABLE A-8: MAJOR SECTION UPDATES

| Section                                                                                                                                | Update Description                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>256 KB Flash and 64 KB<br>SRAM) with Audio and<br>Graphics Interfaces, USB, and<br>Advanced Analog" | The PIC32MX270FDB device and Note 4 were added to <b>TABLE 2: "PIC32MX2XX</b><br><b>28/36/44-pin USB Family Features"</b> .       |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | EXAMPLE 2-1: "Crystal Load Capacitor Calculation" was updated.                                                                    |

| 30.0 "Electrical<br>Characteristics"                                                                                                   | Parameter DO50a (Csosc) was removed from the Capacitive Loading Requirements on Output Pins AC Characteristics (see Table 30-16). |

| "Product Identification<br>System"                                                                                                     | The device mapping was updated to include type B for Software Targeting.                                                          |