Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

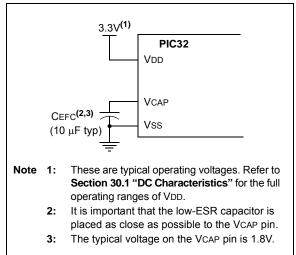

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f064d-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

## 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

| Pin # | Full Pin Name                        | Pi | in # | Full Pin Name                                  |

|-------|--------------------------------------|----|------|------------------------------------------------|

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 | 1  | 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   | 2  | 20   | RPC9/CTED7/RC9                                 |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   | 2  | 21   | Vss                                            |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   | 2  | 22   | VCAP                                           |

| 5     | Vdd                                  | 2  | 23   | Vdd                                            |

| 6     | Vss                                  | 2  | 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 7     | OSC1/CLKI/RPA2/RA2                   | 2  | 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              | 2  | 26   | AN12/PMD0/RB12                                 |

| 9     | SOSCI/RPB4/RB4                       | 2  | 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       | 2  | 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 11    | RPC3/RC3                             | 2  | 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 12    | Vss                                  | 3  | 30   | AVss                                           |

| 13    | Vdd                                  | 3  | 31   | AVdd                                           |

| 14    | Vdd                                  | 3  | 32   | MCLR                                           |

| 15    | PGED3/RPB5/PMD7/RB5                  | 3  | 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 16    | PGEC3/RPB6/PMD6/RB6                  | 3  | 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         | 3  | 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        | 3  | 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

#### TABLE 8: **PIN NAMES FOR 36-PIN USB DEVICES**

## 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016C

|       | PIC32MX220F032C<br>PIC32MX230F064C<br>PIC32MX250F128C |       |                                                  |

|-------|-------------------------------------------------------|-------|--------------------------------------------------|

|       |                                                       |       | 36                                               |

|       |                                                       |       | 1                                                |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name                                    |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2             | 19    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3               | 20    | RPC9/CTED7/RC9                                   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0                    | 21    | Vss                                              |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1                    | 22    | VCAP                                             |

| 5     | VDD                                                   | 23    | VDD                                              |

| 6     | Vss                                                   | 24    | PGED2/RPB10/D+/CTED11/RB10                       |

| 7     | OSC1/CLKI/RPA2/RA2                                    | 25    | PGEC2/RPB11/D-/RB11                              |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3                               | 26    | VUSB3V3                                          |

| 9     | SOSCI/RPB4/RB4                                        | 27    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                        | 28    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 11    | AN12/RPC3/RC3                                         | 29    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 12    | Vss                                                   | 30    | AVss                                             |

| 13    | Vdd                                                   | 31    | AVdd                                             |

| 14    | VDD                                                   | 32    | MCLR                                             |

| 15    | TMS/RPB5/USBID/RB5                                    | 33    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 16    | VBUS                                                  | 34    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7                          | 35    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 18    | TCK/RP88/SCL1/CTED10/PM04/RB8                         | 36    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin 1: Select" for restrictions.

Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information. 2:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 3:

4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

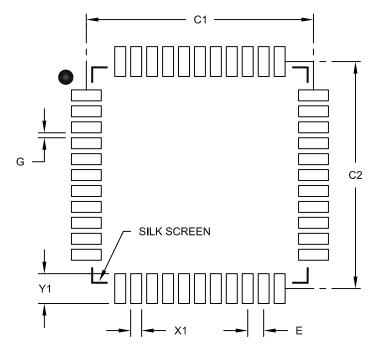

## TABLE 9: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

## 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

44

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

## 5.1 Flash Controller Control Registers

## TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                                        |                        | 0         |       |                        |       |       |       |       |        | Bit     | s       |      |      |      |      |      |      |      | 6          |

|--------------------------------------------|------------------------|-----------|-------|------------------------|-------|-------|-------|-------|--------|---------|---------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#)                | Register<br>Name       | Bit Range | 31/15 | 30/14                  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| F400                                       | NVMCON <sup>(1)</sup>  | 31:16     | —     | —                      |       |       |       |       |        |         |         |      |      |      |      | 0000 |      |      |            |

| 15:0 WR WREN WRERR LVDERR LVDSTAT NVMOP<3: |                        |           |       |                        |       |       |       |       | P<3:0> |         | 0000    |      |      |      |      |      |      |      |            |

| F410                                       | NVMKEY                 | 31:16     |       | NVMKEY<31:0>           |       |       |       |       |        |         |         |      |      |      |      |      |      |      |            |

| 1410                                       |                        | 15:0      |       |                        |       |       |       |       |        |         | ~51.02  |      |      |      |      |      |      |      | 0000       |

| F420                                       | NVMADDR <sup>(1)</sup> | 31:16     |       |                        |       |       |       |       |        | NVMADD  | P<31.0> |      |      |      |      |      |      |      | 0000       |

| 1 420                                      | NVINADDR               | 15:0      |       |                        |       |       |       |       |        | NVINADD | N~51.02 |      |      |      |      |      |      |      | 0000       |

| F430                                       | NVMDATA                | 31:16     |       |                        |       |       |       |       |        |         | N~31·0> |      |      |      |      |      |      |      | 0000       |

| 1 430                                      |                        | 15:0      |       | NVMDATA<31:0>          |       |       |       |       |        |         |         |      |      |      |      |      |      |      |            |

| E440                                       | NVMSRCADDR             | 31:16     |       | NV/ASPCADDP<21:0> 0000 |       |       |       |       |        |         |         |      |      |      |      |      |      |      |            |

| 1 440                                      | NVINGRCADDR            | 15:0      |       | NVMSRCADDR<31:0>       |       |       |       |       |        |         |         |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | ¢,        |       |       |       |       |             |            |          | Bits        |      |      |      |                           |            |        |               |        |                           |  |       |                  |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|------------|----------|-------------|------|------|------|---------------------------|------------|--------|---------------|--------|---------------------------|--|-------|------------------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10      | 25/9     | 24/8        | 23/7 | 22/6 | 21/5 | 20/4                      | 19/3       | 18/2   | 17/1          | 16/0   | All<br>Resets             |  |       |                  |      |

| 1100                        | 1007                            | 31:16     | _     | —     | —     |       | SPI1IP<2:0> |            | SPI1IS<1 |             | -    | —    | —    | USBIP<2:0> <sup>(2)</sup> |            |        | USBIP<2:0>(2) |        | USBIP<2:0> <sup>(2)</sup> |  | USBIS | <1:0> <b>(2)</b> | 0000 |

| 1100                        | IPC7                            | 15:0      | _     | -     | —     | (     | CMP3IP<2:0> | IP3IP<2:0> |          | CMP3IS<1:0> |      | _    | _    | CI                        | MP2IP<2:0> | •      | CMP2IS<1:0>   |        | 0000                      |  |       |                  |      |

| 1110                        | IPC8                            | 31:16     | _     | _     | —     |       | PMPIP<2:0>  |            | PMPIS    | S<1:0>      | _    | —    | _    | (                         | CNIP<2:0>  |        | CNIS          | <1:0>  | 0000                      |  |       |                  |      |

| 1110                        | IPCo                            | 15:0      |       | —     | _     |       | I2C1IP<2:0> | 21IP<2:0>  |          | I2C1IS<1:0> |      | —    | _    | U1IP<2:0>                 |            |        | U1IS          | <1:0>  | 0000                      |  |       |                  |      |

| 1120                        | IPC9                            | 31:16     |       | —     | _     | (     | CTMUIP<2:0  | >          | CTMU     | S<1:0>      | —    | —    | _    | I2C2IP<2:0>               |            | 12C218 | 6<1:0>        | 0000   |                           |  |       |                  |      |

| 1120                        | IFC9                            | 15:0      | -     | —     | _     |       | U2IP<2:0>   |            | U2IS<    | <1:0>       | _    | _    | _    | SPI2IP<2:0>               |            |        | SPI2IS        | S<1:0> | 0000                      |  |       |                  |      |

| 1130                        | IPC10                           | 31:16     | —     | _     | —     | [     | DMA3IP<2:0> | 1A3IP<2:0> |          | S<1:0>      | _    | —    | _    | DMA2IP<2:0>               |            | DMA2I  | S<1:0>        | 0000   |                           |  |       |                  |      |

| 1130                        | IFC IU                          | 15:0      | _     | _     | _     | [     | DMA1IP<2:0> | A1IP<2:0>  |          | DMA1IS<1:0> |      | _    | _    | DMA0IP<2:0>               |            | DMA0I  | S<1:0>        | 0000   |                           |  |       |                  |      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | _                | —                |

| 23:16        | U-0               | U-0 R-0           |                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| R = Readable bit W = Writable bit I |                  |                           |                    |  |

|-------------------------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit                    | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR                   | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### **REGISTER 9-9:** DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

## Legend:

| •                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31-24  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| bit 23     | CHSDIE: Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 22     | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| DIL 22     | CHSHIE: Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 21     | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|            | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| bit 20     | CHDHIE: Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| bit 19     | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 18     | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 17     | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 16     | CHERIE: Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| bit 15-8   | 0 = Interrupt is disabled<br>Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| bit 7      | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|            | <ul> <li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 6      | <b>CHSHIF:</b> Channel Source Half Empty Interrupt Flag bit<br>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)<br>0 = No interrupt is pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )   |

| bit 5      | CHDDIF: Channel Destination Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSI</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IZ) |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| © 2011-201 | 16 Microchip Technology Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DS  |

| 2 2011 20  | is more any restricted from the second s | 20  |

DS60001168J-page 95

## TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5390                        |                                 | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UTEPTU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        |                                 | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

## 11.1 Parallel I/O (PIO) Ports

All port pins have 10 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

## 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Pin Diagrams"** section for the available pins and their functionality.

## 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

## 11.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX1XX/2XX 28/36/44-pin Family devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

An additional control register (CNCONx) is shown in Register 11-3.

## 11.2 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR, or INV register, the base register must be read.

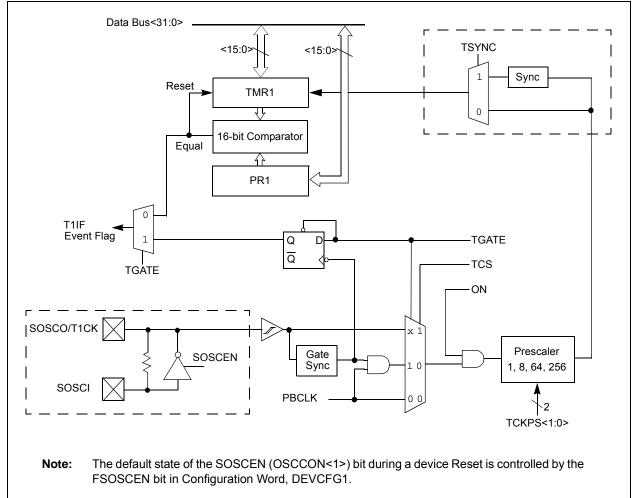

## 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

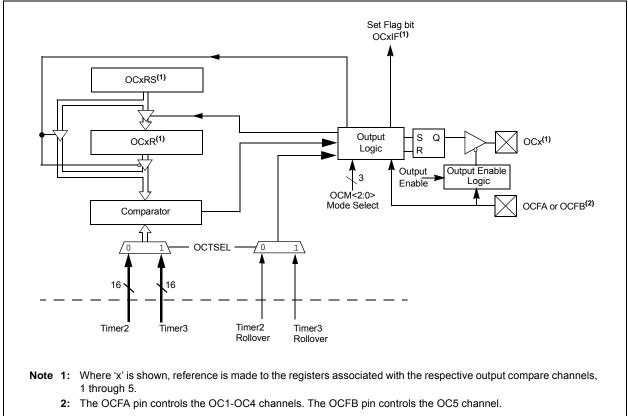

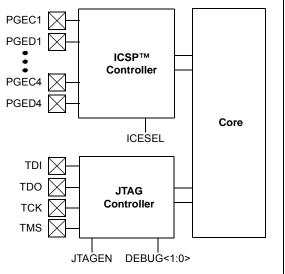

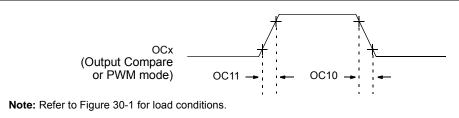

## 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

## **REGISTER 18-2:** I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| bit 4 | <b>P:</b> Stop bit<br>1 = Indicates that a Stop bit has been detected last                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>         |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                         |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> </ul> |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                             |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                      |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                 |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                       |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                  |

0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 21.24        | U-0                 | U-0                 |

| 31:24        |                   | -                 | _                 | -                 | _                 |                   | _                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | F                 | ORM<2:0>            |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           |                   | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 =Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |  |