Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f064dt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

44

1

#### TABLE 14: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

5: Shaded pins are 5V tolerant.

|          |                                        | Pin Nu                                | mber <sup>(1)</sup>                    |                                        |             |                |                                                                         |  |  |  |  |

|----------|----------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|-------------------------------------------------------------------------|--|--|--|--|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC     | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                             |  |  |  |  |

| USBID    | <sub>11</sub> (3)                      | 14 <sup>(3)</sup>                     | 15 <b>(3)</b>                          | 41 <sup>(3)</sup>                      | I           | ST             | USB OTG ID detect                                                       |  |  |  |  |

| CTED1    | 27                                     | 2                                     | 33                                     | 19                                     | I           | ST             | CTMU External Edge Input                                                |  |  |  |  |

| CTED2    | 28                                     | 3                                     | 34                                     | 20                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED3    | 13                                     | 16                                    | 17                                     | 43                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED4    | 15                                     | 18                                    | 19                                     | 1                                      | I           | ST             | 7                                                                       |  |  |  |  |

| CTED5    | 22                                     | 25                                    | 28                                     | 14                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED6    | 23                                     | 26                                    | 29                                     | 15                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED7    | _                                      | _                                     | 20                                     | 5                                      | I           | ST             | 7                                                                       |  |  |  |  |

| CTED8    | _                                      |                                       | _                                      | 13                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED9    | 9                                      | 12                                    | 10                                     | 34                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED10   | 14                                     | 17                                    | 18                                     | 44                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED11   | 18                                     | 21                                    | 24                                     | 8                                      | I           | ST             | 7                                                                       |  |  |  |  |

| CTED12   | 2                                      | 5                                     | 36                                     | 22                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTED13   | 3                                      | 6                                     | 1                                      | 23                                     | I           | ST             | 7                                                                       |  |  |  |  |

| CTPLS    | 21                                     | 24                                    | 27                                     | 11                                     | 0           | _              | CTMU Pulse Output                                                       |  |  |  |  |

| PGED1    | 1                                      | 4                                     | 35                                     | 21                                     | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 1        |  |  |  |  |

| PGEC1    | 2                                      | 5                                     | 36                                     | 22                                     | Ι           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |  |  |  |  |

| PGED2    | 18                                     | 21                                    | 24                                     | 8                                      | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 2        |  |  |  |  |

| PGEC2    | 19                                     | 22                                    | 25                                     | 9                                      | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |  |  |  |  |

| PGED3    | 11 <sup>(2)</sup><br>27 <sup>(3)</sup> | 14 <sup>(2)</sup><br>2 <sup>(3)</sup> | 15 <sup>(2)</sup><br>33 <sup>(3)</sup> | 41 <sup>(2)</sup><br>19 <sup>(3)</sup> | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 3        |  |  |  |  |

|          | 12 <b>(2)</b>                          | 15 <b>(2)</b>                         | 16 <b>(2)</b>                          | 42 <sup>(2)</sup>                      |             | OT             | Clock input pin for Programming/                                        |  |  |  |  |

| PGEC3    | 28 <sup>(3)</sup>                      | 3 <b>(3)</b>                          | 34 <sup>(3)</sup>                      | 20 <sup>(3)</sup>                      |             | ST             | Debugging Communication Channel 3                                       |  |  |  |  |

| PGED4    | —                                      | —                                     | 3                                      | 12                                     | I/O         | ST             | Data I/O pin for Programming/Debuggir<br>Communication Channel 4        |  |  |  |  |

| PGEC4    | —                                      | —                                     | 4                                      | 13                                     | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer PPS = Peripheral Pin Select

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**2:** Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

— = N/A

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDU             | DBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

### Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

#### bit 9-0 BMXDUDBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### 6.1 Reset Control Registers

#### TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         |                                                             | 0         |       |       |       |       |       |       |      |       | Bits |      |      |      |       |      |      |       | s         |

|-----------------------------|-------------------------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|-----------|

| Virtual Address<br>(BF80_#) | VIrtual Addr<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset |

| F600                        | RCON                                                        | 31:16     | _     | _     | _     |       | —     | _     |      | —     | _    | _    |      | _    |       | -    | -    | _     | 0000      |

| 1 000                       | ROOM                                                        | 15:0      | _     |       | -     |       | _     | -     | CMR  | VREGS | EXTR | SWR  |      | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx(2)   |

| E610                        | RSWRST                                                      | 31:16     |       | —     | -     | —     | —     | —     | —    | —     |      | —    | —    | _    | —     | _    | —    | —     | 0000      |

| 1010                        | N31/K31                                                     | 15:0      | _     | _     | _     | -     | _     | —     |      | —     | _    | _    | -    | _    | _     | _    | -    | SWRST | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

#### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | IRQ | Vector |              | Interru                | pt Bit Location |              | Persistent |  |  |  |  |

|-------------------------------------|-----|--------|--------------|------------------------|-----------------|--------------|------------|--|--|--|--|

| Interrupt Source <sup>(1)</sup>     | #   | #      | Flag         | Enable                 | Priority        | Sub-priority | Interrupt  |  |  |  |  |

|                                     |     | Highes | st Natural C | Natural Order Priority |                 |              |            |  |  |  |  |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>      | IEC0<0>                | IPC0<4:2>       | IPC0<1:0>    | No         |  |  |  |  |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>      | IEC0<1>                | IPC0<12:10>     | IPC0<9:8>    | No         |  |  |  |  |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>      | IEC0<2>                | IPC0<20:18>     | IPC0<17:16>  | No         |  |  |  |  |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>      | IEC0<3>                | IPC0<28:26>     | IPC0<25:24>  | No         |  |  |  |  |

| T1 – Timer1                         | 4   | 4      | IFS0<4>      | IEC0<4>                | IPC1<4:2>       | IPC1<1:0>    | No         |  |  |  |  |

| IC1E – Input Capture 1 Error        | 5   | 5      | IFS0<5>      | IEC0<5>                | IPC1<12:10>     | IPC1<9:8>    | Yes        |  |  |  |  |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>      | IEC0<6>                | IPC1<12:10>     | IPC1<9:8>    | Yes        |  |  |  |  |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>      | IEC0<7>                | IPC1<20:18>     | IPC1<17:16>  | No         |  |  |  |  |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>      | IEC0<8>                | IPC1<28:26>     | IPC1<25:24>  | No         |  |  |  |  |

| T2 – Timer2                         | 9   | 8      | IFS0<9>      | IEC0<9>                | IPC2<4:2>       | IPC2<1:0>    | No         |  |  |  |  |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10>     | IEC0<10>               | IPC2<12:10>     | IPC2<9:8>    | Yes        |  |  |  |  |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11>     | IEC0<11>               | IPC2<12:10>     | IPC2<9:8>    | Yes        |  |  |  |  |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12>     | IEC0<12>               | IPC2<20:18>     | IPC2<17:16>  | No         |  |  |  |  |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13>     | IEC0<13>               | IPC2<28:26>     | IPC2<25:24>  | No         |  |  |  |  |

| T3 – Timer3                         | 14  | 12     | IFS0<14>     | IEC0<14>               | IPC3<4:2>       | IPC3<1:0>    | No         |  |  |  |  |

| IC3E – Input Capture 3              | 15  | 13     | IFS0<15>     | IEC0<15>               | IPC3<12:10>     | IPC3<9:8>    | Yes        |  |  |  |  |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16>     | IEC0<16>               | IPC3<12:10>     | IPC3<9:8>    | Yes        |  |  |  |  |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17>     | IEC0<17>               | IPC3<20:18>     | IPC3<17:16>  | No         |  |  |  |  |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18>     | IEC0<18>               | IPC3<28:26>     | IPC3<25:24>  | No         |  |  |  |  |

| T4 – Timer4                         | 19  | 16     | IFS0<19>     | IEC0<19>               | IPC4<4:2>       | IPC4<1:0>    | No         |  |  |  |  |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20>     | IEC0<20>               | IPC4<12:10>     | IPC4<9:8>    | Yes        |  |  |  |  |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21>     | IEC0<21>               | IPC4<12:10>     | IPC4<9:8>    | Yes        |  |  |  |  |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22>     | IEC0<22>               | IPC4<20:18>     | IPC4<17:16>  | No         |  |  |  |  |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23>     | IEC0<23>               | IPC4<28:26>     | IPC4<25:24>  | No         |  |  |  |  |

| T5 – Timer5                         | 24  | 20     | IFS0<24>     | IEC0<24>               | IPC5<4:2>       | IPC5<1:0>    | No         |  |  |  |  |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25>     | IEC0<25>               | IPC5<12:10>     | IPC5<9:8>    | Yes        |  |  |  |  |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26>     | IEC0<26>               | IPC5<12:10>     | IPC5<9:8>    | Yes        |  |  |  |  |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27>     | IEC0<27>               | IPC5<20:18>     | IPC5<17:16>  | No         |  |  |  |  |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28>     | IEC0<28>               | IPC5<28:26>     | IPC5<25:24>  | Yes        |  |  |  |  |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29>     | IEC0<29>               | IPC6<4:2>       | IPC6<1:0>    | No         |  |  |  |  |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30>     | IEC0<30>               | IPC6<12:10>     | IPC6<9:8>    | No         |  |  |  |  |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31>     | IEC0<31>               | IPC6<20:18>     | IPC6<17:16>  | No         |  |  |  |  |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>      | IEC1<0>                | IPC6<28:26>     | IPC6<25:24>  | No         |  |  |  |  |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>      | IEC1<1>                | IPC7<4:2>       | IPC7<1:0>    | No         |  |  |  |  |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>      | IEC1<2>                | IPC7<12:10>     | IPC7<9:8>    | No         |  |  |  |  |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>      | IEC1<3>                | IPC7<20:18>     | IPC7<17:16>  | Yes        |  |  |  |  |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>      | IEC1<4>                | IPC7<28:26>     | IPC7<25:24>  | Yes        |  |  |  |  |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>      | IEC1<5>                | IPC7<28:26>     | IPC7<25:24>  | Yes        |  |  |  |  |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>      | IEC1<6>                | IPC7<28:26>     | IPC7<25:24>  | Yes        |  |  |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

| ILCIOIC L    |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | _                | _                |  |  |  |  |  |

| 22:16        | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |  |  |  |

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

1111111111111111 = 65,535 bytes transferred on an event

#### REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

|              |                   |                   | •••••••••••       |                   |                   |                   | -                |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHCPTR            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |

| Legend:           |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

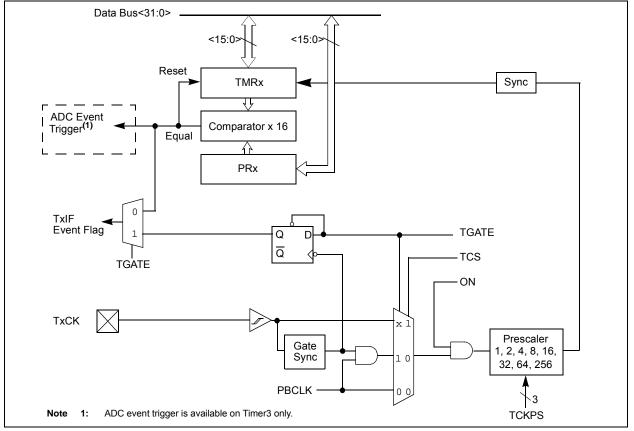

#### 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

#### **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

#### FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

#### 17.1 SPI Control Registers

#### TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| ess                         |                                 | Ċ,                                     |               |         |        |              |              |              |           | Bi     | ts      |           |        |        |             |          |        |         |            |

|-----------------------------|---------------------------------|----------------------------------------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|-----------|--------|--------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range                              | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6      | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16                                  | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —         | _      | -      | —           | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0                                   | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | STAT 31:16 TXBUFELM<4:0> TXBUFELM<4:0> |               |         |        |              |              |              |           | 0000   |         |           |        |        |             |          |        |         |            |

| 5610                        |                                 | 15:0                                   | _             | —       | —      | FRMERR       | SPIBUSY      | —            | —         | SPITUR | SRMT    | SPIROV    | SPIRBE | —      | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI1BUF                         | 31:16                                  | DATA<31:0>    |         |        |              |              |              |           |        | 0000    |           |        |        |             |          |        |         |            |

| 3020                        |                                 | 15:0                                   |               | 00      |        |              |              |              |           |        |         |           | 0000   |        |             |          |        |         |            |

| 5830                        | SPI1BRG                         | 31:16                                  | —             | —       | _      | —            | —            | —            | —         | —      | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 0000                        |                                 | 15:0                                   |               |         |        |              |              |              |           |        |         |           | 0000   |        |             |          |        |         |            |

|                             |                                 | 31:16                                  | —             | —       | —      | —            | —            | —            | —         | —      | —       | —         | _      | _      | —           | _        | —      | —       | 0000       |

| 5840                        | SPI1CON2                        | 15:0                                   | SPI<br>SGNEXT | _       |        | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —         | -      | -      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16                                  | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —         |        |        | _           |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 3F1200N                         | 15:0                                   | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5410                        | SPI2STAT                        | 31:16                                  | —             | _       |        |              | RXE          | BUFELM<4:    | 0>        |        | _       | -         |        |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0                                   | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV    | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16                                  |               |         |        |              |              |              |           | DATA<  | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 5420                        |                                 | 15:0                                   | 000           |         |        |              |              |              |           |        |         | 0000      |        |        |             |          |        |         |            |

| 5A30                        | SPI2BRG                         | 31:16                                  | —             | —       | _      | —            | —            | —            | —         | —      | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 5730                        |                                 | 15:0                                   |               | —       | —      |              |              |              |           |        | E       | 3RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16                                  | —             | —       | —      | _            | —            | _            | —         | —      | —       | —         | _      | —      | —           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0                                   | SPI<br>SGNEXT | —       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —         | _      | _      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

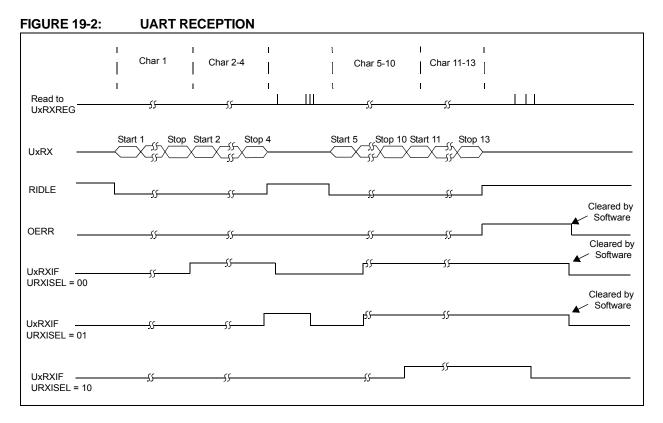

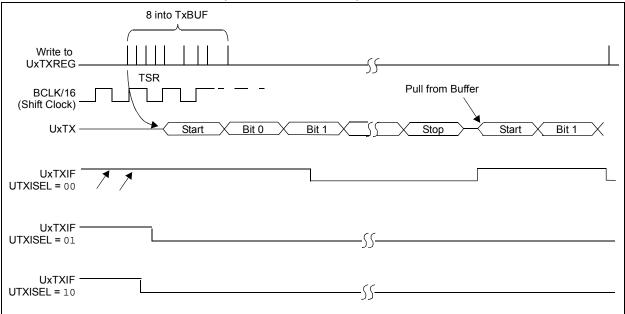

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | CH0NB             | _                 | _                 | _                 |                   | CH0SB             | <3:0>            |                  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | CH0NA             |                   | _                 | _                 | CH0SA<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 |                   | _                | -                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31 |          | CH0NB: Negative Input Select bit for Sample B                                                                                        |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

|        |          | 1 = Channel 0 negative input is AN1                                                                                                  |

|        |          | 0 = Channel 0 negative input is VREFL                                                                                                |

| bit 30 | -28      | Unimplemented: Read as '0'                                                                                                           |

| bit 27 | -24      | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                  |

|        |          | 1111 = Channel 0 positive input is Open <sup>(1)</sup>                                                                               |

|        |          | 1110 = Channel 0 positive input is IVREF <sup>(2)</sup>                                                                              |

|        |          | 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(3)</sup>                                                    |

|        |          | 1100 = Channel 0 positive input is AN12 <sup>(4)</sup>                                                                               |

|        |          | •                                                                                                                                    |

|        |          | •                                                                                                                                    |

|        |          | •                                                                                                                                    |

|        |          | 0001 = Channel 0 positive input is AN1                                                                                               |

|        |          | 0000 = Channel 0 positive input is AN0                                                                                               |

| bit 23 |          | <b>CH0NA:</b> Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                              |

|        |          | 1 = Channel 0 negative input is AN1                                                                                                  |

|        | ~ ~      | 0 = Channel 0 negative input is VREFL                                                                                                |

| bit 22 | -20      | Unimplemented: Read as '0'                                                                                                           |

| bit 19 | -16      | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting                                                              |

|        |          | 1111 = Channel 0 positive input is Open <sup>(1)</sup>                                                                               |

|        |          | 1110 = Channel 0 positive input is IVREF <sup>(2)</sup>                                                                              |

|        |          | 1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup> |

|        |          |                                                                                                                                      |

|        |          |                                                                                                                                      |

|        |          |                                                                                                                                      |

|        |          | - Channel O positive input in AN1                                                                                                    |

|        |          | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                     |

| bit 15 | 0        | Unimplemented: Read as '0'                                                                                                           |

| bit 15 | -0       | Ommplemented. Nead as 0                                                                                                              |

| Note   | 1:       | This selection is only used with CTMU capacitive and time measurement.                                                               |

|        | 2:       | See Section 24.0 "Comparator Voltage Reference (CVREF)" for more information.                                                        |

|        | 3:       | See Section 25.0 "Charge Time Measurement Unit (CTMU)" for more information.                                                         |

|        | 3.<br>4: | AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices.                                               |

|        | т.       |                                                                                                                                      |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 |                   | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | —                 | _                 | —                 | —                 | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

#### Legend:

| Logena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan

0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | —                     |                   |                   | -                 | _                 |                   | _                | -                |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 23:16        | —                     | _                 | —                 | -                 | —                 | FPLLODIV<2:0>     |                  |                  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | UPLLEN <sup>(1)</sup> |                   | —                 | _                 | _                 | UF                | PLLIDIV<2:0>     | .(1)             |

| 7:0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |

|              | —                     | FPLLMUL<2:0>      |                   |                   | _                 | F                 | PLLIDIV<2:0      | >                |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 27-3:**

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1'

- bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

- 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier

- 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is only available on PIC32MX2XX devices.

#### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 31.0** "**50 MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

#### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

3: See the "Pin Diagrams" section for the 5V tolerant pins.

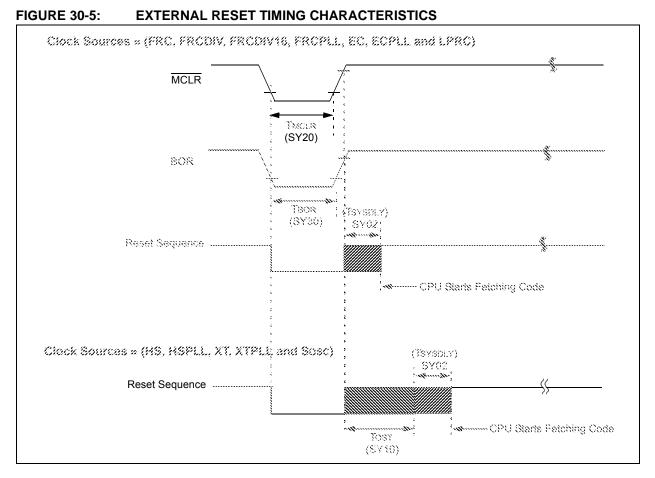

| TABLE              | TABLE 30-22: RESETS TIMING |                                                                                                                                            |      |                                                                                                                                                                                                   |      |       |            |  |

|--------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| AC CHARACTERISTICS |                            |                                                                                                                                            |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |

| Param.<br>No.      | Symbol                     | Characteristics <sup>(1)</sup>                                                                                                             | Min. | Typical <sup>(2)</sup>                                                                                                                                                                            | Max. | Units | Conditions |  |

| SY00               | Τρυ                        | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | —    | 400                                                                                                                                                                                               | 600  | μS    | _          |  |

| SY02               | TSYSDLY                    | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. | _    | 1 μs +<br>8 SYSCLK<br>cycles                                                                                                                                                                      | _    | _     | _          |  |

| SY20               | TMCLR                      | MCLR Pulse Width (low)                                                                                                                     | 2    | _                                                                                                                                                                                                 | _    | μS    | —          |  |

| SY30               | TBOR                       | BOR Pulse Width (low)                                                                                                                      |      | 1                                                                                                                                                                                                 | _    | μS    | —          |  |

These parameters are characterized, but not tested in manufacturing. Note 1:

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

#### TABLE 30-34: ADC MODULE SPECIFICATIONS

|               | AC CHAR    | ACTERISTICS                       | (unless otl     | herwise stat | <b>ed)</b><br>-40°C ≤ TA | √≤ +85° | e 5): 2.5V to 3.6V<br>C for Industrial<br>°C for V-temp |

|---------------|------------|-----------------------------------|-----------------|--------------|--------------------------|---------|---------------------------------------------------------|

| Param.<br>No. | Symbol     | Characteristics                   | Min. Typical Ma |              |                          | Units   | Conditions                                              |

| ADC Ac        | curacy – N | leasurements with Inter           | nal VREF+/V     | REF-         |                          |         | •                                                       |

| AD20d         | Nr         | Resolution                        |                 | 10 data bits | 3                        | bits    | (Note 3)                                                |

| AD21d         | INL        | Integral Non-linearity            | > -1            | _            | < 1                      | LSb     | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |

| AD22d         | DNL        | Differential Non-linearity        | > -1            | —            | < 1                      | LSb     | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |

| AD23d         | Gerr       | Gain Error                        | > -4            | _            | < 4                      | LSb     | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |

| AD24d         | EOFF       | Offset Error                      | > -2            | _            | < 2                      | Lsb     | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |

| AD25d         |            | Monotonicity                      |                 |              | _                        | _       | Guaranteed                                              |

| Dynami        | c Performa | ance                              | ·               |              |                          |         | <u> </u>                                                |

| AD32b         | SINAD      | Signal to Noise and<br>Distortion | 55              | 58.5         | _                        | dB      | (Notes 3,4)                                             |

| AD34b         | ENOB       | Effective Number of bits          | 9.0             | 9.5          |                          | bits    | (Notes 3,4)                                             |

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

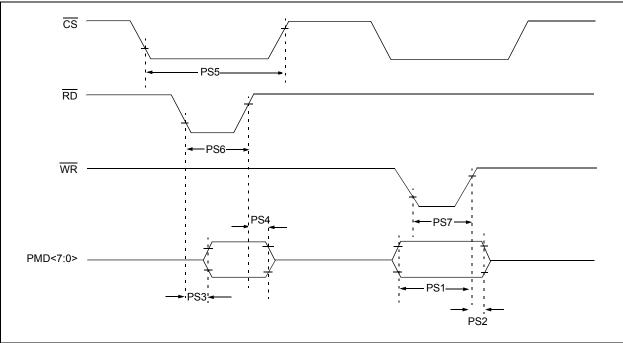

#### FIGURE 30-20: PARALLEL SLAVE PORT TIMING

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Program Memory Size<br>Pin Count<br>Software Targeting<br>Tape and Reel Flag (if<br>Speed (if applicable)<br>Temperature Range<br>Package | 32-bit RISC MCU with M4K <sup>®</sup> core,<br>32 KB program memory, 44-pin,                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           | Flash Memory Family                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Architecture                                                                                                                              | $MX = M4K^{\odot} MCU \text{ core}$                                                                                                                                                                                                                                                                                                                                                                                                    |

| Product Groups                                                                                                                            | 1XX = General purpose microcontroller family<br>2XX = General purpose microcontroller family                                                                                                                                                                                                                                                                                                                                           |

| Flash Memory Family                                                                                                                       | F = Flash program memory                                                                                                                                                                                                                                                                                                                                                                                                               |

| Program Memory Size                                                                                                                       | 016 = 16K<br>032 = 32K<br>064 = 64K<br>128 = 128K<br>256 = 256K                                                                                                                                                                                                                                                                                                                                                                        |

| Pin Count                                                                                                                                 | B = 28-pin<br>C = 36-pin<br>D = 44-pin                                                                                                                                                                                                                                                                                                                                                                                                 |

| Software Targeting                                                                                                                        | B = Targeted for Bluetooth <sup>®</sup> Audio Break-in devices                                                                                                                                                                                                                                                                                                                                                                         |

| Speed                                                                                                                                     | <ul> <li>= 40 MHz - () indicates a blank field; package markings for 40 MHz devices do not include the Speed</li> <li>= 50 MHz</li> </ul>                                                                                                                                                                                                                                                                                              |

| Temperature Range                                                                                                                         | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>V = $-40^{\circ}$ C to $+105^{\circ}$ C (V-temp)                                                                                                                                                                                                                                                                                                                                |

| Package                                                                                                                                   | ML= 28-Lead (6x6 mm) QFN (Plastic Quad Flatpack)ML= 44-Lead (8x8 mm) QFN (Plastic Quad Flatpack)PT= 44-Lead (10x10x1 mm) TQFP (Plastic Thin Quad Flatpack)SO= 28-Lead (7.50 mm) SOIC (Plastic Small Outline)SP= 28-Lead (300 mil) SPDIP (Skinny Plastic Dual In-line)SS= 28-Lead (5.30 mm) SSOP (Plastic Shrink Small Outline)TL= 36-Lead (5x5 mm) VTLA (Very Thin Leadless Array)TL= 44-Lead (6x6 mm) VTLA (Very Thin Leadless Array) |

| Pattern                                                                                                                                   | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                                                                                       |