Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f064dt-v-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4: PIN NAMES FOR 28-PIN USB DEVICES

28-PIN SOIC, SPDIP, SSOP (TOP VIEW) $^{(1,2,3)}$

1 28 1 28 1 28 SSOP SOIC SPDIP

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX270F256B

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 1    | MCLR                                             |

| 2    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 3    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 4    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 5    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| 6    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2        |

| 7    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3          |

| 8    | Vss                                              |

| 9    | OSC1/CLKI/RPA2/RA2                               |

| 10   | OSC2/CLKO/RPA3/PMA0/RA3                          |

| 11   | SOSCI/RPB4/RB4                                   |

| 12   | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                   |

| 13   | VDD                                              |

| 14   | TMS/RPB5/USBID/RB5                               |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 15   | VBUS                                             |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                     |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                    |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 19   | Vss                                              |

| 20   | VCAP                                             |

| 21   | PGED2/RPB10/D+/CTED11/RB10                       |

| 22   | PGEC2/RPB11/D-/RB11                              |

| 23   | Vusb3v3                                          |

| 24   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 25   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 27   | AVss                                             |

| 28   | AVDD                                             |

#### Note 1

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information

- 3: Shaded pins are 5V tolerant.

#### TABLE 9: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

44-PIN QFN (TOP VIEW)(1,2,3,5)

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

| Pin # | Full Pin Name                                  |

|-------|------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       |

| 2     | RPC6/PMA1/RC6                                  |

| 3     | RPC7/PMA0/RC7                                  |

| 4     | RPC8/PMA5/RC8                                  |

| 5     | RPC9/CTED7/PMA6/RC9                            |

| 6     | Vss                                            |

| 7     | VCAP                                           |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          |

| 10    | AN12/PMD0/RB12                                 |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 16    | AVss                                           |

| 17    | AVDD                                           |

| 18    | MCLR                                           |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

| Pin # | Full Pin Name                        |

|-------|--------------------------------------|

| 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 25    | AN6/RPC0/RC0                         |

| 26    | AN7/RPC1/RC1                         |

| 27    | AN8/RPC2/PMA2/RC2                    |

| 28    | VDD                                  |

| 29    | Vss                                  |

| 30    | OSC1/CLKI/RPA2/RA2                   |

| 31    | OSC2/CLKO/RPA3/RA3                   |

| 32    | TDO/RPA8/PMA8/RA8                    |

| 33    | SOSCI/RPB4/RB4                       |

| 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 35    | TDI/RPA9/PMA9/RA9                    |

| 36    | RPC3/RC3                             |

| 37    | RPC4/PMA4/RC4                        |

| 38    | RPC5/PMA3/RC5                        |

| 39    | Vss                                  |

| 40    | VDD                                  |

| 41    | PGED3/RPB5/PMD7/RB5                  |

| 42    | PGEC3/RPB6/PMD6/RB6                  |

| 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- **5:** Shaded pins are 5V tolerant.

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the following documents, refer to the *Documentation > Reference Manuals* section of the Microchip PIC32 website: http://www.microchip.com/pic32

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |               | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                                |

|----------|---------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|------------------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                    |

| RC0      | _             | _                                 | 3                   | 25                              | I/O         | ST             | PORTC is a bidirectional I/O port              |

| RC1      | _             | _                                 | 4                   | 26                              | I/O         | ST             |                                                |

| RC2      |               | _                                 |                     | 27                              | I/O         | ST             |                                                |

| RC3      | _             | _                                 | 11                  | 36                              | I/O         | ST             |                                                |

| RC4      | _             | _                                 | _                   | 37                              | I/O         | ST             |                                                |

| RC5      | _             | _                                 | _                   | 38                              | I/O         | ST             |                                                |

| RC6      | _             | _                                 | _                   | 2                               | I/O         | ST             |                                                |

| RC7      | _             | _                                 | _                   | 3                               | I/O         | ST             |                                                |

| RC8      | _             | _                                 | _                   | 4                               | I/O         | ST             |                                                |

| RC9      | _             | _                                 | 20                  | 5                               | I/O         | ST             |                                                |

| T1CK     | 9             | 12                                | 10                  | 34                              | I           | ST             | Timer1 external clock input                    |

| T2CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer2 external clock input                    |

| T3CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer3 external clock input                    |

| T4CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer4 external clock input                    |

| T5CK     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Timer5 external clock input                    |

| U1CTS    | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART1 clear to send                            |

| U1RTS    | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART1 ready to send                            |

| U1RX     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART1 receive                                  |

| U1TX     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART1 transmit                                 |

| U2CTS    | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART2 clear to send                            |

| U2RTS    | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART2 ready to send                            |

| U2RX     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | UART2 receive                                  |

| U2TX     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | UART2 transmit                                 |

| SCK1     | 22            | 25                                | 28                  | 14                              | I/O         | ST             | Synchronous serial clock input/output for SPI1 |

| SDI1     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | SPI1 data in                                   |

| SDO1     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | SPI1 data out                                  |

| SS1      | PPS           | PPS                               | PPS                 | PPS                             | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O  |

| SCK2     | 23            | 26                                | 29                  | 15                              | I/O         | ST             | Synchronous serial clock input/output for SPI2 |

| SDI2     | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | SPI2 data in                                   |

| SDO2     | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | SPI2 data out                                  |

| SS2      | PPS           | PPS                               | PPS                 | PPS                             | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O  |

| SCL1     | 14            | 17                                | 18                  | 44                              | I/O         | ST             | Synchronous serial clock input/output for I2C1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer Analog = Analog input

O = Output

PPS = Peripheral Pin Select

P = Power I = Input — = N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

- 2: Pin number for PIC32MX1XX devices only.

- 3: Pin number for PIC32MX2XX devices only.

# 2.9 Typical Application Connection Examples

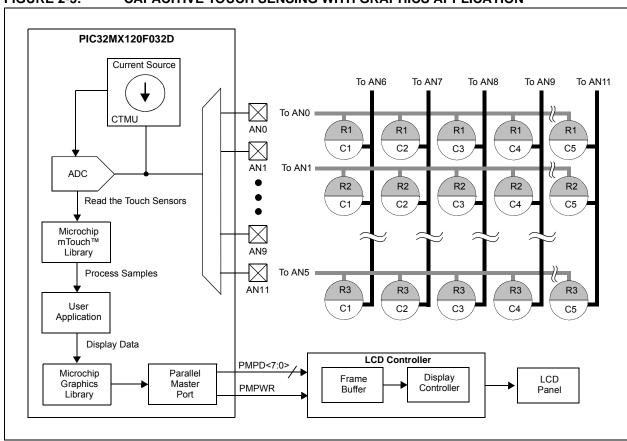

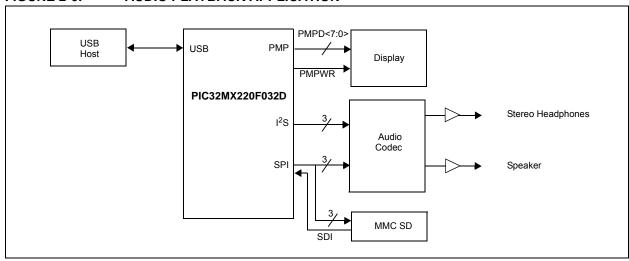

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-5: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        |                   |                       | BYTO              | <1:0>             | WBO <sup>(1)</sup> | -                 | _                | BITO             |

| 22.46        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                     | _                 | _                 | _                  | _                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       | •                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

- bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit (1)

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) =  $\underline{1}$  (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 PLEN<4:0>: Polynomial Length bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

These bits are unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Denotes the length of the polynomial – 1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

### 10.0 USB ON-THE-GO (OTG)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 27. "USB On-The-Go (OTG)"** (DS60001126), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- · Low-Speed Host support

- · USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

Note:

The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | )>                |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 |                   |                   | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | 1                 | -                 | _                 | -                 | -                 | _                 | -                | -                |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 FRML<7:0>: The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

### 11.4 Ports Control Registers

### TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |                          |                         | Bits                    | 3                       |      |      |          |          |          |          |          | "          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-------------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                    | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | _     | _     | _     | 1     | _                        | _                       | _                       | 1                       | _    | _    | _        | _        | _        |          | _        | 0000       |

|                             |                                 | 15:0      | _     | _     | _     | _     |       | _                        | _                       | _                       | _                       |      |      | _        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | _     | _     | _     |       | _                        |                         |                         | _                       | _    | _    | _        | _        | _        | _        | _        | 0000       |

| 00.0                        | 1111071                         | 15:0      | _     | _     | _     | _     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup>   | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | _    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | _     | _     | _     | _     | _     |                          |                         |                         | _                       | _    | _    |          |          |          |          |          | 0000       |

| 0020                        | TOITIN                          | 15:0      | _     | _     | _     | _     |       | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>      | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | _    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | LATA                            | 31:16     | _     | _     | _     | _     | _     | -                        | _                       | _                       |                         | _    | _    | _        | _        | _        | _        | _        | 0000       |

| 0030                        | LAIA                            | 15:0      | _     | _     | _     | _     | -     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>    | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | _    | _    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | _     | _     | _     |       |       | 1                        | _                       | _                       |                         |      |      | -        | -        | _        | -        | _        | 0000       |

| 6040                        | ODCA                            | 15:0      | _     | _     | _     |       |       | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>    | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    |      |      | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | _     | _     | _     |       |       | 1                        | _                       | _                       |                         |      |      | -        | -        | _        | -        | _        | 0000       |

| 6050                        | CNPUA                           | 15:0      | _     | _     | _     | 1     | 1     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup>   | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | _    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 0000                        | ONDDA                           | 31:16     |       |       | _     | 1     |       | _                        | _                       | _                       | _                       | _    | _    | _        | _        | _        | _        | _        | 0000       |

| 6060                        | CNPDA                           | 15:0      | _     | _     | _     | _     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup>   | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | _    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 0070                        | ONIOONIA                        | 31:16     | _     | _     | _     | _     | _     | _                        | _                       | _                       | _                       | _    | _    | _        | _        | _        | _        | _        | 0000       |

| 6070                        | CNCONA                          | 15:0      | ON    | _     | SIDL  | _     | _     | _                        | _                       | _                       | _                       | _    | _    | _        | _        | _        | _        | _        | 0000       |

|                             | 0115114                         | 31:16     | _     | _     | _     | _     |       | _                        | _                       | _                       | _                       | _    | _    | _        | _        | _        | _        | _        | 0000       |

| 6080                        | CNENA                           | 15:0      | _     | _     | _     | _     | _     | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup>   | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   | _    | _    | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _                        | _                       | _                       |                         | _    | _    | _        | _        | _        | _        | _        | 0000       |

| 6090                        | CNSTATA                         | 15:0      | _     | _     | _     | _     | _     | CNSTATA10 <sup>(2)</sup> | CNSTATA9 <sup>(2)</sup> | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> | _    | _    | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: This bit is only available on 44-pin devices.

REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

bit 3 **Unimplemented:** Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized 0 = External clock input is not synchronized

$\frac{\text{When TCS = }0:}{\text{This bit is ignored.}}$

bit 1 TCS: Timer Clock Source Select bit

1 = External clock from TxCKI pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| PIC32WX1XX/2XX 28/36/44-PIN FAMILY |  |  |  |  |  |  |  |

|------------------------------------|--|--|--|--|--|--|--|

| NOTES:                             |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send a NACK during an Acknowledge sequence

- 0 = Send an ACK during an Acknowledge sequence

- bit 4 **ACKEN:** Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-2: UxSTA: UARTX STATUS AND CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |

| 31:24        |                   | _                 | _                 | -                 | _                 | -                 | _                | ADM_EN           |  |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-25 Unimplemented: Read as '0'

bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

1 = Automatic Address Detect mode is enabled

0 = Automatic Address Detect mode is disabled

bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

11 = Reserved, do not use

10 = Interrupt is generated and asserted while the transmit buffer is empty

01 = Interrupt is generated and asserted when all characters have been transmitted

00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

bit 13 **UTXINV:** Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

1 = UxTX Idle state is '0'

0 = UxTX Idle state is '1'

### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

1 = IrDA encoded UxTX Idle state is '1'

0 = IrDA encoded UxTX Idle state is '0'

bit 12 URXEN: Receiver Enable bit

1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

bit 11 UTXBRK: Transmit Break bit

1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

0 = Break transmission is disabled or completed

bit 10 UTXEN: Transmit Enable bit

1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1).

0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

1 = Transmit buffer is full

0 = Transmit buffer is not full, at least one more character can be written

bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

#### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        | _                 | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |

| 22.46        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        | _                 |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x             | R/W-x R/W-x       |                   | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | _                 |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 |                   |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | -                 | _                 | -                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan0 = Skip ANx for input scan

**Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects VSS for scan.

2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

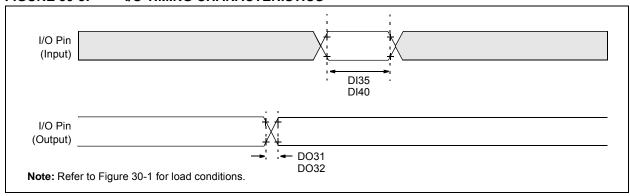

### FIGURE 30-3: I/O TIMING CHARACTERISTICS

### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |            |            |

|--------------------|--------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------------|------------|

| Param.<br>No.      | Symbol | Characteris               | Min.                                                                                                                                                                                                                                           | Typical <sup>(1)</sup> | Max. | Units | Conditions |            |

| DO31               | TioR   | Port Output Rise Time     |                                                                                                                                                                                                                                                | 1                      | 5    | 15    | ns         | VDD < 2.5V |

|                    |        |                           |                                                                                                                                                                                                                                                | 1                      | 5    | 10    | ns         | VDD > 2.5V |

| DO32               | TioF   | Port Output Fall Time     |                                                                                                                                                                                                                                                | 1                      | 5    | 15    | ns         | VDD < 2.5V |

|                    |        |                           |                                                                                                                                                                                                                                                | 1                      | 5    | 10    | ns         | VDD > 2.5V |

| DI35               | TINP   | INTx Pin High or Low Time |                                                                                                                                                                                                                                                | 10                     | _    |       | ns         | _          |

| DI40               | TRBP   | CNx High or Low Tir       | me (input)                                                                                                                                                                                                                                     | 2                      | _    | _     | Tsysclk    | _          |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

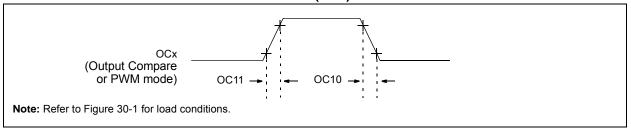

### FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |                    |  |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time           | _                                                                                                                                                                                                                                              | _                      |      | ns    | See parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time           |                                                                                                                                                                                                                                                | _                      | _    | ns    | See parameter DO31 |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

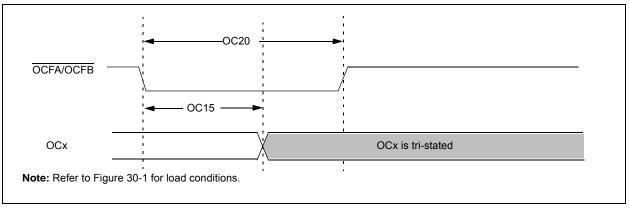

### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)   Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |     |       |            |  |

|--------------------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                                                                                                                                                                    | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15               | TFD    | Fault Input to PWM I/O Change  | _                                                                                                                                                                                                      | _                      | 50  | ns    | _          |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                                                                                                                                                                     | _                      | _   | ns    | _          |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

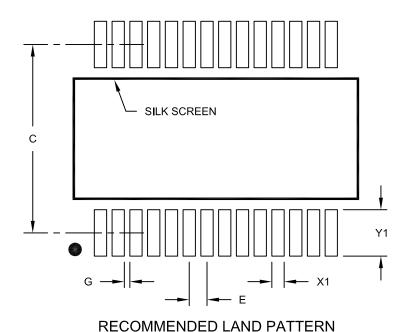

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units MILLIMETERS **Dimension Limits** MIN MOM MAX Contact Pitch 0.65 BSC Ε Contact Pad Spacing С 7.20 Contact Pad Width (X28) X1 0.45 <u>Y1</u> Contact Pad Length (X28) 1.75 G 0.20 Distance Between Pads

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

### **INDEX**

| Numerics                                        |     | Core Exception Types                                                |     |

|-------------------------------------------------|-----|---------------------------------------------------------------------|-----|

| 50 MHz Electrical Characteristics               | 301 | EJTAG Debug Support                                                 |     |

| ۸                                               |     | Power Management                                                    |     |

| A                                               |     | CPU Module                                                          |     |

| AC Characteristics                              |     | Customer Change Notification Service  Customer Notification Service |     |

| 10-Bit Conversion Rate Parameters               |     | Customer Support                                                    |     |

| ADC Specifications                              |     | Customer Support                                                    | 341 |

| Analog-to-Digital Conversion Requirements       |     | D                                                                   |     |

| EJTAG Timing Requirements                       |     | DC and AC Characteristics                                           |     |

| Internal FRC Accuracy                           |     | Graphs and Tables                                                   | 307 |

| Internal RC Accuracy                            |     | DC Characteristics                                                  |     |

| OTG Electrical Specifications                   |     | I/O Pin Input Specifications                                        |     |

| Parallel Master Port Read Requirements          |     | I/O Pin Output Specifications                                       | ,   |

| Parallel Master Port Write                      |     | Idle Current (IDLE)                                                 |     |

| Parallel Master Port Write Requirements         |     | Power-Down Current (IPD)                                            |     |

| Parallel Slave Port Requirements                |     | Program Memory                                                      |     |

| PLL Clock Timing                                |     | Temperature and Voltage Specifications                              |     |

| Analog-to-Digital Converter (ADC)               | 209 | DC Characteristics (50 MHz)                                         |     |

| Assembler                                       |     | , ,                                                                 |     |

| MPASM Assembler                                 | 254 | Idle Current (IDLE)Power-Down Current (IPD)                         |     |

| В                                               |     | Development Support                                                 |     |

|                                                 |     | · ··                                                                |     |

| Block Diagrams                                  |     | Direct Memory Access (DMA) Controller                               | 03  |

| ADC Module                                      |     | E                                                                   |     |

| Comparator I/O Operating Modes                  |     | Electrical Characteristics                                          | 257 |

| Comparator Voltage Reference                    |     | AC                                                                  |     |

| Connections for On-Chip Voltage Regulator       |     | Errata                                                              |     |

| Core and Peripheral Modules                     |     | External Clock                                                      |     |

| CPU                                             | 33  | Timer1 Timing Requirements                                          | 275 |

| CTMU Configurations                             |     | Timer2, 3, 4, 5 Timing Requirements                                 |     |

| Time Measurement                                |     | Timing Requirements                                                 |     |

| DMA                                             |     | External Clock (50 MHz)                                             | 270 |

| I2C Circuit                                     |     | Timing Requirements                                                 | 304 |

| Input Capture                                   |     |                                                                     |     |

| Interrupt Controller                            |     | F                                                                   |     |

| JTAG Programming, Debugging and Trace Ports     |     | Flash Program Memory                                                | 53  |

| Output Compare Module                           |     | RTSP Operation                                                      |     |

| PMP Pinout and Connections to External Devices. |     |                                                                     |     |

| Reset System                                    |     | I                                                                   |     |

| RTCC                                            |     | I/O Ports                                                           | 127 |

| SPI Module                                      |     | Parallel I/O (PIO)                                                  |     |

| Timer1                                          |     | Write/Read Timing                                                   |     |

| Timer2/3/4/5 (16-Bit)                           |     | Input Change Notification                                           |     |

| Typical Multiplexed Port Structure              | 127 | Instruction Set                                                     |     |

| UART                                            |     | Inter-Integrated Circuit (I2C                                       |     |

| WDT and Power-up Timer                          | 153 | Internal Voltage Reference Specifications                           |     |

| Brown-out Reset (BOR)                           |     | Internet Address                                                    |     |

| and On-Chip Voltage Regulator                   | 250 | Interrupt Controller                                                | 63  |

| С                                               |     | IRG, Vector and Bit Location                                        |     |

|                                                 |     | -                                                                   |     |

| C Compilers                                     |     | M                                                                   |     |

| MPLAB C18                                       | 254 | Memory Maps                                                         |     |

| Charge Time Measurement Unit. See CTMU.         |     | PIC32MX110/210 Devices                                              |     |

| Clock Diagram                                   | 74  | (4 KB RAM, 16 KB Flash)                                             | 38  |

| Comparator                                      |     | PIC32MX120/220 Devices                                              |     |

| Specifications                                  |     | (8 KB RAM, 32 KB Flash)                                             | 39  |

| Comparator Module                               |     | PIC32MX130/230                                                      |     |

| Comparator Voltage Reference (CVref             |     | (16 KB RAM, 256 KB Flash)                                           | 43  |

| Configuration Bit                               |     | PIC32MX130/230 Devices                                              |     |

| Configuring Analog Port Pins                    | 128 | (16 KB RAM, 64 KB Flash)                                            | 40  |

| CPU                                             |     | PIC32MX150/250 Devices                                              |     |

| Architecture Overview                           |     | (32 KB RAM, 128 KB Flash)                                           | 41  |

| Coprocessor 0 Registers                         | 35  | PIC32MX170/270                                                      |     |

| U1OTGSTAT (USB OTG Status)                     | 110  |

|------------------------------------------------|------|

| U1PWRC (USB Power Control)                     | 112  |

| U1SOF (USB SOF Threshold)                      | 123  |

| U1STAT (USB Status)                            | .118 |

| U1TOK (USB Token)                              | 122  |

| UxMODE (UARTx Mode)                            |      |

| UxSTA (UARTx Status and Control)               |      |

| WDTCON (Watchdog Timer Control)                | 155  |

| Resets                                         | 59   |

| Revision History                               | 329  |

| RTCALRM (RTC ALARM Control)                    | 203  |

| S                                              |      |

| Serial Peripheral Interface (SPI)              | 165  |

| Software Simulator (MPLAB SIM)                 | 255  |

| Special Features                               | 239  |

| т                                              |      |

| Timer1 Module                                  | 143  |

| Timer2/3, Timer4/5 Modules                     |      |

| Timing Diagrams                                |      |

| 10-Bit Analog-to-Digital Conversion            |      |

| (ASAM = 0, SSRC<2:0> = 000)                    | 293  |

| 10-Bit Analog-to-Digital Conversion (ASAM = 1, |      |

| SSRC<2:0> = 111, SAMC<4:0> = 00001)            | 294  |

| EJTAG                                          | 300  |

| External Clock                                 | 269  |

| I/O Characteristics                            | 272  |

| I2Cx Bus Data (Master Mode)                    | 283  |

| I2Cx Bus Data (Slave Mode)                     | 286  |

| I2Cx Bus Start/Stop Bits (Master Mode)         | 283  |

| I2Cx Bus Start/Stop Bits (Slave Mode)          | 286  |

| Input Capture (CAPx)                           | 276  |

| OCx/PWM                                        | 277  |

| Output Compare (OCx)                           |      |

| Parallel Master Port Read                      | 296  |

| Parallel Master Port Write                     | 297  |

|                                                |      |

| Parallel Slave Port                      | . 295 |

|------------------------------------------|-------|

| SPIx Master Mode (CKE = 0)               | . 278 |

| SPIx Master Mode (CKE = 1)               | . 279 |

| SPIx Slave Mode (CKE = 0)                | . 280 |

| SPIx Slave Mode (CKE = 1)                | . 281 |

| Timer1, 2, 3, 4, 5 External Clock        | . 275 |

| UART Reception                           | . 187 |

| UART Transmission (8-bit or 9-bit Data)  | . 187 |

| Timing Requirements                      |       |

| CLKO and I/O                             | . 272 |

| Timing Specifications                    |       |

| I2Cx Bus Data Requirements (Master Mode) | . 284 |

| I2Cx Bus Data Requirements (Slave Mode)  |       |

| Input Capture Requirements               | . 276 |

| Output Compare Requirements              |       |

| Simple OCx/PWM Mode Requirements         |       |

| SPIx Master Mode (CKE = 0) Requirements  |       |

| SPIx Master Mode (CKE = 1) Requirements  |       |

| SPIx Slave Mode (CKE = 1) Requirements   |       |

| SPIx Slave Mode Requirements (CKE = 0)   | . 280 |

| Timing Specifications (50 MHz)           |       |

| SPIx Master Mode (CKE = 0) Requirements  |       |

| SPIx Master Mode (CKE = 1) Requirements  |       |

| SPIx Slave Mode (CKE = 1) Requirements   |       |

| SPIx Slave Mode Requirements (CKE = 0)   | . 305 |

| U                                        |       |

|                                          | 404   |

| UART                                     |       |

| USB On-The-Go (OTG)                      | . 103 |

| V                                        |       |

| VCAP pin                                 | . 250 |

| Voltage Regulator (On-Chip)              | . 250 |

| w                                        |       |

| WWW Address                              | 341   |

| WWW. On Line Support                     |       |