Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 19                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256b-50i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 12: PIN NAMES FOR 44-PIN USB DEVICES

# 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

1

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| 1     |                                                  | 23    |                                           |

|       | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    |       | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | VDD                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

5: Shaded pins are 5V tolerant.

# **Table of Contents**

| 1.0   | Device Overview                                    |     |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    |     |

| 3.0   | CPU                                                |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Flash Program Memory                               | 53  |

| 6.0   | Resets                                             | 59  |

| 7.0   | Interrupt Controller                               |     |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 83  |

| 10.0  | USB On-The-Go (OTG)                                | 103 |

| 11.0  | I/O Ports                                          | 127 |

| 12.0  | Timer1                                             | 143 |

| 13.0  | Timer2/3, Timer4/5                                 | 147 |

| 14.0  | Watchdog Timer (WDT)                               | 153 |

| 15.0  | Input Capture                                      | 157 |

| 16.0  | Output Compare                                     | 161 |

| 17.0  | Serial Peripheral Interface (SPI)                  |     |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 181 |

|       | Parallel Master Port (PMP)                         |     |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 209 |

| 23.0  |                                                    |     |

| 24.0  | Comparator Voltage Reference (CVREF)               |     |

| 25.0  | Charge Time Measurement Unit (CTMU)                | 227 |

| 26.0  | Power-Saving Features                              | 233 |

| 27.0  | Special Features                                   | 239 |

| 28.0  | Instruction Set                                    |     |

| 29.0  | Development Support                                | 253 |

| 30.0  | Electrical Characteristics                         | 257 |

|       | 50 MHz Electrical Characteristics                  |     |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

| The I | Vicrochip Web Site                                 | 341 |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Prod  | uct Identification System                          | 342 |

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | _                 | —                 | —                 | _                 | -                 | _                                             | _                |

| 22:16        | U-0                                           | U-0              |

| 23:16        |                   | _                 | —                 | —                 |                   |                   | _                                             |                  |

| 15:0         | U-0                                           | U-0              |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | BMXEE DMAEE       |                   | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

# REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

### Legend:

| 0                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

|       | •                                                         |

|-------|-----------------------------------------------------------|

| bit 7 | BTSEE: Bit Stuff Error Interrupt Enable bit               |

|       | 1 = BTSEF interrupt is enabled                            |

|       | 0 = BTSEF interrupt is disabled                           |

| bit 6 | BMXEE: Bus Matrix Error Interrupt Enable bit              |

|       | 1 = BMXEF interrupt is enabled                            |

|       | 0 = BMXEF interrupt is disabled                           |

| bit 5 | DMAEE: DMA Error Interrupt Enable bit                     |

|       | 1 = DMAEF interrupt is enabled                            |

|       | 0 = DMAEF interrupt is disabled                           |

| bit 4 | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit |

|       | 1 = BTOEF interrupt is enabled                            |

|       | 0 = BTOEF interrupt is disabled                           |

| bit 3 | DFN8EE: Data Field Size Error Interrupt Enable bit        |

|       | 1 = DFN8EF interrupt is enabled                           |

|       | 0 = DFN8EF interrupt is disabled                          |

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

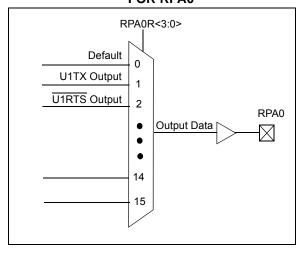

### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

# 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

# 11.3.6.1 Control Register Lock Sequence

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, IOLOCK (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

# 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The Configuration bit, IOL1WAY (DEVCFG3<29>), blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

|              |                   |                   |                   |                   |                   |                   |                  | ., _, _,         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | _                | _                |

# **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

# REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

# 14.1 Watchdog Timer Control Registers

# TABLE 14-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                       |                                 | 6         |       | Bits  |       |       |       |       |      |      |      |      |      |          |      |      |          |        | s          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|------|------|----------|--------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3 | 18/2 | 17/1     | 16/0   | All Resets |

| 0000                      | WDTCON                          | 31:16     | _     | —     | _     | —     | —     |       | _    | _    | -    | _    | —    | _        | _    | —    | -        | —      | 0000       |

| 0000                      | 0000 WDTCON                     | 15:0      | ON    | _     |       | _     | _     | _     |      | _    |      |      | SI   | VDTPS<4: | 0>   |      | WDTWINEN | WDTCLR | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                    | _                 | -                 | —                | —                |

| 00.10        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                    | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                    | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            | OCM<2:0>          |                  |                  |

# REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in hardware only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

# **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

# 17.1 SPI Control Registers

# TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| ess                         |                                 | Ċ,        |               |         |           |              |                        |                 |           | Bi      | ts      |           |        |        |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|-----------|--------------|------------------------|-----------------|-----------|---------|---------|-----------|--------|--------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13     | 28/12        | 27/11                  | 26/10           | 25/9      | 24/8    | 23/7    | 22/6      | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL    | MSSEN        | FRMSYPW                | FF              | RMCNT<2:( | )>      | MCLKSEL | —         | _      | -      | —           | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0      | ON            | _       | SIDL      | DISSDO       | MODE32                 | MODE16          | SMP       | CKE     | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | —             | _       | _         |              | RXE                    | BUFELM<4:       | 0>        |         | —       | —         | -      |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| 5610                        |                                 | 15:0      | _             | —       | —         | FRMERR       | SPIBUSY                | —               | —         | SPITUR  | SRMT    | SPIROV    | SPIRBE | —      | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |           |              |                        |                 |           | DATA<   | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 3020                        |                                 | 15:0      |               |         |           |              |                        |                 |           | Brance  | .01.0   |           |        |        |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | —             | —       | _         | —            | —                      | —               | —         | —       | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 0000                        |                                 | 15:0      | _             | —       | BRG<12:0> |              |                        |                 |           |         |         |           |        | 0000   |             |          |        |         |            |

|                             |                                 | 31:16     | —             | —       | —         | —            | —                      | —               | —         | —       | —       | —         | _      | _      | —           | _        | —      | —       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | _       |           | FRM<br>ERREN | SPI<br>ROVEN           | SPI<br>TUREN    | IGNROV    | IGNTUR  | AUDEN   | —         | -      | -      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL    | MSSEN        | EN FRMSYPW FRMCNT<2:0> |                 |           | MCLKSEL | —       |           |        | _      |             | SPIFE    | ENHBUF | 0000    |            |

| 5A00                        | 3F1200N                         | 15:0      | ON            | _       | SIDL      | DISSDO       | MODE32                 | MODE16          | SMP       | CKE     | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5410                        | SPI2STAT                        | 31:16     | —             | —       |           |              | RXE                    | RXBUFELM<4:0> — |           |         | _       | -         |        |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _             | _       | _         | FRMERR       | SPIBUSY                | _               | _         | SPITUR  | SRMT    | SPIROV    | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |           |              |                        |                 |           | DATA<   | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 5420                        |                                 | 15:0      |               |         |           |              |                        |                 |           | Brance  |         |           |        |        |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | —             | —       | _         | —            | —                      | —               | —         | —       | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 5730                        |                                 | 15:0      |               | —       | —         |              |                        |                 |           |         | E       | 3RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —         | _            | —                      | _               | —         | —       | —       | —         | _      | —      | —           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | —       | _         | FRM<br>ERREN | SPI<br>ROVEN           | SPI<br>TUREN    | IGNROV    | IGNTUR  | AUDEN   | —         | _      | _      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | —                 | _                | _                |

| 22:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

| Legend:           | HC = Cleared in Hardware                            |                      |                    |  |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2C$  module; all  $I^2C$  pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 20.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to Section 13. "Parallel<br>Master Port (PMP)" (DS60001128), |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | which is available from the <i>Documentation</i><br>> <i>Reference Manual</i> section of the<br>Microchip PIC32 web site<br>(www.microchip.com/pic32).                                                                                                                                       |

The PMP is a parallel 8-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Key features of the PMP module include:

- Fully multiplexed address/data mode

- Demultiplexed or partially multiplexed address/ data mode

- up to 11 address lines with single Chip Select

- up to 12 address lines without Chip Select

- One Chip Select line

- Programmable strobe options

- Individual read and write strobes or;

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- · Legacy parallel slave port support

- · Enhanced parallel slave support

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- · Selectable input voltage levels

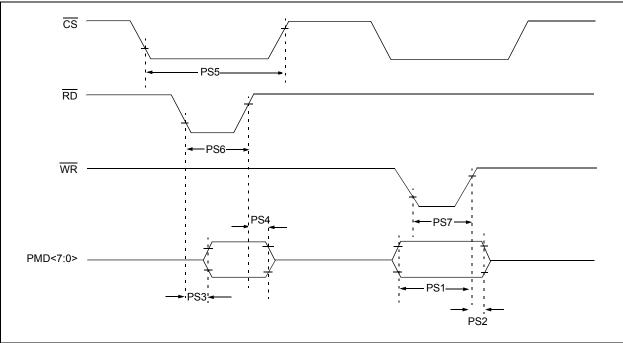

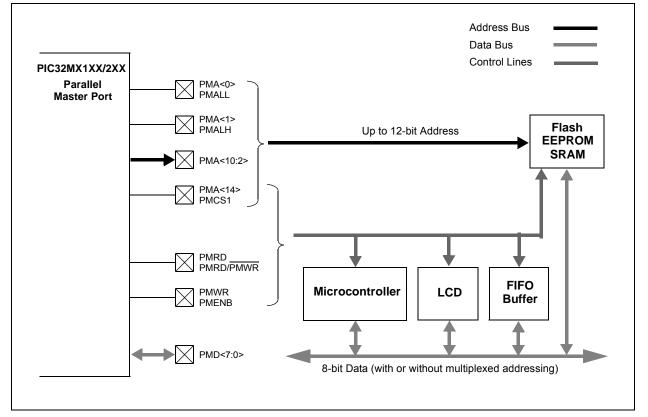

Figure 20-1 illustrates the PMP module block diagram.

# FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

# 20.1 PMP Control Registers

# TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 |               |       |               |       |       |         |        |        | Bi     | ts      |        |           |       |        |      |       |       |            |

|-----------------------------|---------------------------------|---------------|-------|---------------|-------|-------|---------|--------|--------|--------|---------|--------|-----------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14         | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5      | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000                        | PMCON                           | 31:16         | —     | —             | -     | _     |         |        | -      | _      | —       | —      | —         |       |        | —    | —     | _     | 0000       |

| 7000                        | FINCON                          | 15:0          | ON    | _             | SIDL  | ADRML | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF∙    | <1:0>  | ALP       |       | CS1P   | _    | WRSP  | RDSP  | 0000       |

| 7010                        | PMMODE                          | 31:16         | —     | _             |       | _     | _       |        | _      | _      | —       | _      | —         |       | -      | _    | —     | _     | 0000       |

| 7010                        | FININODE                        | 15:0          | BUSY  | IRQM          | <1:0> | INCM  | <1:0>   | _      | MODE   | <1:0>  | WAITE   | 3<1:0> |           | WAITM | /<3:0> |      | WAITE | <1:0> | 0000       |

|                             |                                 | 31:16         | _     | —             | _     | _     | —       | _      | —      | _      | _       | _      | _         | —     | —      | _    | _     | —     | 0000       |

| 7020                        | PMADDR                          | 15:0          | _     | CS1<br>ADDR14 | _     | _     | _       |        |        |        |         | /      | ADDR<10:0 | >     |        |      |       |       | 0000       |

| 7030                        | PMDOUT                          | 31:16<br>15:0 |       |               |       |       |         |        |        | DATAOU | T<31:0> |        |           |       |        |      |       |       | 0000       |

| 7040                        | PMDIN                           | 31:16<br>15:0 |       |               |       |       |         |        |        | DATAIN | <31:0>  |        |           |       |        |      |       |       | 0000       |

| 7050                        |                                 | 31:16         | _     | _             |       | _     | -       |        | -      | _      | _       | _      | —         |       |        | _    | _     |       | 0000       |

| 7050                        | PMAEN                           | 15:0          | _     | PTEN14        | _     | _     | _       |        |        |        |         |        | PTEN<10:0 | >     |        |      |       |       | 0000       |

| 7060                        | PMSTAT                          | 31:16         |       | —             | _     |       | _       | _      | —      | _      |         |        | —         | _     | —      |      | —     | _     | 0000       |

| 1000                        | FINISTAT                        | 15:0          | IBF   | IBOV          | _     | _     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —         | _     | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

# 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

### 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

| DC CHARACTERISTICS |        |                                      |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |        |                                               |  |  |  |  |

|--------------------|--------|--------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-----------------------------------------------|--|--|--|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min.   | Typical <sup>(1)</sup>                                                                                                                                                                                                                                                                | Max. | Units  | Conditions                                    |  |  |  |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |        |                                                                                                                                                                                                                                                                                       |      |        |                                               |  |  |  |  |

| D130               | Eр     | Cell Endurance                       | 20,000 | —                                                                                                                                                                                                                                                                                     | _    | E/W    | —                                             |  |  |  |  |

| D131               | Vpr    | VDD for Read                         | 2.3    | —                                                                                                                                                                                                                                                                                     | 3.6  | V      | —                                             |  |  |  |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.3    | —                                                                                                                                                                                                                                                                                     | 3.6  | V      | —                                             |  |  |  |  |

| D134               | Tretd  | Characteristic Retention             | 20     | —                                                                                                                                                                                                                                                                                     | _    | Year   | Provided no other specifications are violated |  |  |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | _      | 10                                                                                                                                                                                                                                                                                    | _    | mA     | —                                             |  |  |  |  |

|                    | Tww    | Word Write Cycle Time                | —      | 411                                                                                                                                                                                                                                                                                   | _    | es     | See Note 4                                    |  |  |  |  |

| D136               | Trw    | Row Write Cycle Time                 | —      | 6675                                                                                                                                                                                                                                                                                  | _    | Cycles | See Note 2,4                                  |  |  |  |  |

| D137               | TPE    | Page Erase Cycle Time                | —      | 20011                                                                                                                                                                                                                                                                                 | _    |        | See Note 4                                    |  |  |  |  |

|                    | TCE    | Chip Erase Cycle Time                | —      | 80180                                                                                                                                                                                                                                                                                 | _    | FRC    | See Note 4                                    |  |  |  |  |

# TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

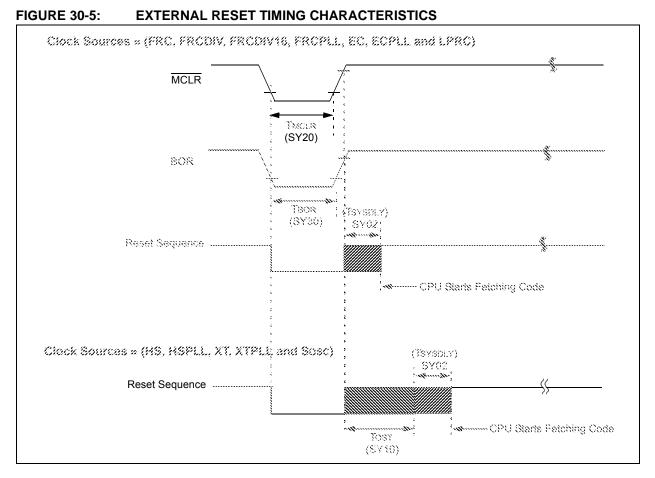

| TABLE              | 30-22: F | RESETS TIMING                                                                                                                              |      |                                                                                                                                                                                                   |      |       |            |  |  |  |  |  |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|--|

| AC CHARACTERISTICS |          |                                                                                                                                            |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |  |  |  |

| Param.<br>No.      | Symbol   | Characteristics <sup>(1)</sup>                                                                                                             | Min. | Typical <sup>(2)</sup>                                                                                                                                                                            | Max. | Units | Conditions |  |  |  |  |  |

| SY00               | Τρυ      | Power-up Period<br>Internal Voltage Regulator Enabled                                                                                      | —    | 400                                                                                                                                                                                               | 600  | μS    | _          |  |  |  |  |  |

| SY02               | TSYSDLY  | System Delay Period:<br>Time Required to Reload Device<br>Configuration Fuses plus SYSCLK<br>Delay before First instruction is<br>Fetched. | _    | 1 μs +<br>8 SYSCLK<br>cycles                                                                                                                                                                      | _    | _     | _          |  |  |  |  |  |

| SY20               | TMCLR    | MCLR Pulse Width (low)                                                                                                                     | 2    | _                                                                                                                                                                                                 | _    | μS    | —          |  |  |  |  |  |

| SY30               | TBOR     | BOR Pulse Width (low)                                                                                                                      |      | 1                                                                                                                                                                                                 | _    | μS    | —          |  |  |  |  |  |

These parameters are characterized, but not tested in manufacturing. Note 1:

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

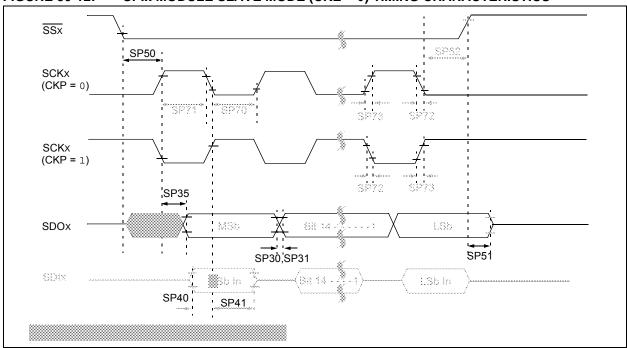

### FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

# TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |      |       |                    |  |  |  |

|--------------------|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)                                       | TSCK/2                                                                                                                                                                                                                                                                                | —                   |      | ns    | —                  |  |  |  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)                                      | TSCK/2                                                                                                                                                                                                                                                                                | —                   |      | ns    | —                  |  |  |  |

| SP72               | TscF                  | SCKx Input Fall Time                                               | —                                                                                                                                                                                                                                                                                     | _                   |      | ns    | See parameter DO32 |  |  |  |

| SP73               | TscR                  | SCKx Input Rise Time                                               | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See parameter DO31 |  |  |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)                                | —                                                                                                                                                                                                                                                                                     | —                   |      | ns    | See parameter DO32 |  |  |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)                                | _                                                                                                                                                                                                                                                                                     | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP35               | TscH2doV,             | SDOx Data Output Valid after                                       | —                                                                                                                                                                                                                                                                                     | _                   | 15   | ns    | VDD > 2.7V         |  |  |  |

|                    | TscL2DoV              | SCKx Edge                                                          | —                                                                                                                                                                                                                                                                                     | —                   | 20   | ns    | VDD < 2.7V         |  |  |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10                                                                                                                                                                                                                                                                                    |                     | _    | ns    | —                  |  |  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                       | 10                                                                                                                                                                                                                                                                                    | _                   | _    | ns    | —                  |  |  |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                                                                                                   |                     | _    | ns    | —                  |  |  |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>             | 5                                                                                                                                                                                                                                                                                     | —                   | 25   | ns    | _                  |  |  |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20                                                                                                                                                                                                                                                                             | —                   |      | ns    | —                  |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

| AC CHA        | RACTERIS | STICS           |                        | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industri $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-tem |      |       |                                            |  |  |

|---------------|----------|-----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|--|

| Param.<br>No. | Symbol   | Charact         | eristics               | Min.                                                                                                                                                                                            | Max. | Units | Conditions                                 |  |  |

| IS10          | TLO:SCL  | Clock Low Time  | 100 kHz mode           | 4.7                                                                                                                                                                                             | —    | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |

|               |          |                 | 400 kHz mode           | 1.3                                                                                                                                                                                             | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                             | _    | μS    | _                                          |  |  |

| IS11          | THI:SCL  | Clock High Time | 100 kHz mode           | 4.0                                                                                                                                                                                             | _    | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |

|               |          |                 | 400 kHz mode           | 0.6                                                                                                                                                                                             | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                             | _    | μS    |                                            |  |  |

| IS20          | TF:SCL   | SDAx and SCLx   | 100 kHz mode           | —                                                                                                                                                                                               | 300  | ns    | CB is specified to be from                 |  |  |

|               |          | Fall Time       | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                     | 300  | ns    | 10 to 400 pF                               |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | _                                                                                                                                                                                               | 100  | ns    |                                            |  |  |

| IS21 TR:SCL   | TR:SCL   | SDAx and SCLx   | 100 kHz mode           |                                                                                                                                                                                                 | 1000 | ns    | CB is specified to be from                 |  |  |

|               |          | Rise Time       | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                     | 300  | ns    | 10 to 400 pF                               |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | —                                                                                                                                                                                               | 300  | ns    |                                            |  |  |

| IS25          | TSU:DAT  | Data Input      | 100 kHz mode           | 250                                                                                                                                                                                             | —    | ns    | _                                          |  |  |

|               |          | Setup Time      | 400 kHz mode           | 100                                                                                                                                                                                             | —    | ns    |                                            |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 100                                                                                                                                                                                             | —    | ns    |                                            |  |  |

| IS26          | THD:DAT  | Data Input      | 100 kHz mode           | 0                                                                                                                                                                                               | —    | ns    |                                            |  |  |

|               |          | Hold Time       | 400 kHz mode           | 0                                                                                                                                                                                               | 0.9  | μs    |                                            |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 0                                                                                                                                                                                               | 0.3  | μS    |                                            |  |  |

| IS30          | TSU:STA  | Start Condition | 100 kHz mode           | 4700                                                                                                                                                                                            | —    | ns    | Only relevant for Repeated                 |  |  |

|               |          | Setup Time      | 400 kHz mode           | 600                                                                                                                                                                                             | —    | ns    | Start condition                            |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                             | —    | ns    |                                            |  |  |

| IS31          | THD:STA  | Start Condition | 100 kHz mode           | 4000                                                                                                                                                                                            | —    | ns    | After this period, the first               |  |  |

|               |          | Hold Time       | 400 kHz mode           | 600                                                                                                                                                                                             | —    | ns    | clock pulse is generated                   |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                             | —    | ns    |                                            |  |  |

| IS33          | Tsu:sto  | Stop Condition  | 100 kHz mode           | 4000                                                                                                                                                                                            |      | ns    |                                            |  |  |

|               |          | Setup Time      | 400 kHz mode           | 600                                                                                                                                                                                             |      | ns    | ]                                          |  |  |

|               |          |                 | 1 MHz mode<br>(Note 1) | 600                                                                                                                                                                                             |      | ns    |                                            |  |  |

# TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

### TABLE 30-34: ADC MODULE SPECIFICATIONS

|               |            |                                                      | Standard Operating Conditions (see Note 5): 2.5V to 3.6V (unless otherwise stated) |              |                                  |          |                                                                                                         |  |  |  |

|---------------|------------|------------------------------------------------------|------------------------------------------------------------------------------------|--------------|----------------------------------|----------|---------------------------------------------------------------------------------------------------------|--|--|--|

|               |            |                                                      |                                                                                    |              |                                  |          | ≤ +85°C for Industrial<br>≤ +105°C for V-temp                                                           |  |  |  |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                                                                               | Typical      | Max.                             | Units    | Conditions                                                                                              |  |  |  |

| Device        | Supply     |                                                      |                                                                                    |              |                                  |          |                                                                                                         |  |  |  |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                  | —            | Lesser of<br>VDD + 0.3 or<br>3.6 | V        | _                                                                                                       |  |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                                                                                | _            | AVdd                             | V        | (Note 1)                                                                                                |  |  |  |

| Referen       | ce Inputs  | ·                                                    |                                                                                    |              |                                  |          | ·                                                                                                       |  |  |  |