Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| roduct Status             | Active                                                                         |

| ore Processor             | MIPS32® M4K™                                                                   |

| ore Size                  | 32-Bit Single-Core                                                             |

| peed                      | 40MHz                                                                          |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| lumber of I/O             | 19                                                                             |

| rogram Memory Size        | 256KB (256K x 8)                                                               |

| ogram Memory Type         | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 16K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 9x10b                                                                      |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type              | Surface Mount                                                                  |

| ckage / Case              | 28-VQFN Exposed Pad                                                            |

| upplier Device Package    | 28-QFN (6x6)                                                                   |

| ırchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256b-i-ml |

## TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

44-PIN QFN (TOP VIEW)(1,2,3,5)

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

.4

| Pin # | Full Pin Name                                    |

|-------|--------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         |

| 2     | RPC6/PMA1/RC6                                    |

| 3     | RPC7/PMA0/RC7                                    |

| 4     | RPC8/PMA5/RC8                                    |

| 5     | RPC9/CTED7/PMA6/RC9                              |

| 6     | Vss                                              |

| 7     | VCAP                                             |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       |

| 9     | PGEC2/RPB11/D-/RB11                              |

| 10    | Vusb3v3                                          |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 12    | PGED4/TMS/PMA10/RA10                             |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 16    | AVss                                             |

| 17    | AVDD                                             |

| 18    | MCLR                                             |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 23   | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 24   | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 25   | AN6/RPC0/RC0                              |

| 26   | AN7/RPC1/RC1                              |

| 27   | AN8/RPC2/PMA2/RC2                         |

| 28   | VDD                                       |

| 29   | Vss                                       |

| 30   | OSC1/CLKI/RPA2/RA2                        |

| 31   | OSC2/CLKO/RPA3/RA3                        |

| 32   | TDO/RPA8/PMA8/RA8                         |

| 33   | SOSCI/RPB4/RB4                            |

| 34   | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 35   | TDI/RPA9/PMA9/RA9                         |

| 36   | AN12/RPC3/RC3                             |

| 37   | RPC4/PMA4/RC4                             |

| 38   | RPC5/PMA3/RC5                             |

| 39   | Vss                                       |

| 40   | VDD                                       |

| 41   | RPB5/USBID/RB5                            |

| 42   | VBUS                                      |

| 43   | RPB7/CTED3/PMD5/INT0/RB7                  |

| 44   | RPB8/SCL1/CTED10/PMD4/RB8                 |

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

- Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- 5: Shaded pins are 5V tolerant.

### TABLE 11: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

44-PIN TQFP (TOP VIEW)(1,2,3,5)

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

1

| Pin # | Full Pin Name                                  |

|-------|------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       |

| 2     | RPC6/PMA1/RC6                                  |

| 3     | RPC7/PMA0/RC7                                  |

| 4     | RPC8/PMA5/RC8                                  |

| 5     | RPC9/CTED7/PMA6/RC9                            |

| 6     | Vss                                            |

| 7     | VCAP                                           |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          |

| 10    | AN12/PMD0/RB12                                 |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 16    | AVss                                           |

| 17    | AVDD                                           |

| 18    | MCLR                                           |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

| Pin # | Full Pin Name                        |

|-------|--------------------------------------|

| 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 25    | AN6/RPC0/RC0                         |

| 26    | AN7/RPC1/RC1                         |

| 27    | AN8/RPC2/PMA2/RC2                    |

| 28    | VDD                                  |

| 29    | Vss                                  |

| 30    | OSC1/CLKI/RPA2/RA2                   |

| 31    | OSC2/CLKO/RPA3/RA3                   |

| 32    | TDO/RPA8/PMA8/RA8                    |

| 33    | SOSCI/RPB4/RB4                       |

| 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 35    | TDI/RPA9/PMA9/RA9                    |

| 36    | RPC3/RC3                             |

| 37    | RPC4/PMA4/RC4                        |

| 38    | RPC5/PMA3/RC5                        |

| 39    | Vss                                  |

| 40    | VDD                                  |

| 41    | PGED3/RPB5/PMD7/RB5                  |

| 42    | PGEC3/RPB6/PMD6/RB6                  |

| 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- 5: Shaded pins are 5V tolerant.

### 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- · Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- · Dual Internal Bus interfaces

- · Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- · Shifter and store aligner

### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

TABLE 3-1: MIPS32® M4K® PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

# 6.1 Reset Control Registers

# TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                       |                                 |           | Bits  |       |       |       |       |       |      |       |      |      |      |      |       | 8    |      |       |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|------------|

| Virtual Addrı<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Resets |

| F600                      | RCON                            | 31:16     | _     | _     |       | _     | _     | _     |      | _     | _    | _    |      |      |       |      | _    | _     | 0000       |

| F600                      | RCON                            | 15:0      |       | _     | _     | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | _    | WDTO | SLEEP | IDLE | BOR  | POR   | XXXX(2)    |

| F640                      | RSWRST                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _    | _    | _    | _    | _     | _    | _    | _     | 0000       |

| F010                      | KSWKSI                          | 15:0      | _     | _     | _     | _     | _     | _     | I    | _     | _    | _    |      | _    | _     | _    | _    | SWRST | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits 111 = Clock is multiplied by 24 110 = Clock is multiplied by 21 101 = Clock is multiplied by 20 100 = Clock is multiplied by 19 011 = Clock is multiplied by 18 010 = Clock is multiplied by 17 001 = Clock is multiplied by 16 000 = Clock is multiplied by 15 bit 15 Unimplemented: Read as '0' bit 14-12 COSC<2:0>: Current Oscillator Selection bits 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (OSCCON<26:24>) 110 = Internal Fast RC (FRC) Oscillator divided by 16 101 = Internal Low-Power RC (LPRC) Oscillator 100 = Secondary Oscillator (Sosc) 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL) 010 = Primary Oscillator (Posc) (XT, HS or EC) 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL) 000 = Internal Fast RC (FRC) Oscillator bit 11 Unimplemented: Read as '0' bit 10-8 NOSC<2:0>: New Oscillator Selection bits 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits 110 = Internal Fast RC Oscillator (FRC) divided by 16 101 = Internal Low-Power RC (LPRC) Oscillator 100 = Secondary Oscillator (Sosc) 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL) 010 = Primary Oscillator (XT, HS or EC) 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL) 000 = Internal Fast Internal RC Oscillator (FRC) On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>). bit 7 **CLKLOCK:** Clock Selection Lock Enable bit If clock switching and monitoring is disabled (FCKSM<1:0> = 1x): 1 = Clock and PLL selections are locked 0 = Clock and PLL selections are not locked and may be modified If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified. **ULOCK:** USB PLL Lock Status bit<sup>(1)</sup> bit 6 1 = The USB PLL module is in lock or USB PLL module start-up timer is satisfied 0 =The USB PLL module is out of lock or USB PLL module start-up timer is in progress or the USB PLL is disabled bit 5 **SLOCK: PLL Lock Status bit** 1 = The PLL module is in lock or PLL module start-up timer is satisfied 0 = The PLL module is out of lock, the PLL start-up timer is running, or the PLL is disabled bit 4 SLPEN: Sleep Mode Enable bit 1 = The device will enter Sleep mode when a WAIT instruction is executed 0 = The device will enter Idle mode when a WAIT instruction is executed Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

| <b>TABLE 9-3:</b> | DMA CHANNE | -I S 0-3 | REGISTER | MAP |

|-------------------|------------|----------|----------|-----|

|                   |            |          |          |     |

| ess                         |                                 | 0                       |        |       |       |       |             |       |           | Ві          | its     |          |        |                 |                  |          |          |        | "            |

|-----------------------------|---------------------------------|-------------------------|--------|-------|-------|-------|-------------|-------|-----------|-------------|---------|----------|--------|-----------------|------------------|----------|----------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range               | 31/15  | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9      | 24/8        | 23/7    | 22/6     | 21/5   | 20/4            | 19/3             | 18/2     | 17/1     | 16/0   | All Resets   |

| 3060                        | DCH0CON                         | 31:16                   | _      | _     | _     | 1     | ı           | 1     | _         | _           | _       | _        | _      | 1               | _                | _        | _        | _      | 0000         |

| 3060                        | DCHUCON                         | 15:0                    | CHBUSY | _     | _     | _     | _           | _     | _         | CHCHNS      | CHEN    | CHAED    | CHCHN  | CHAEN           | _                | CHEDET   | CHPR     | l<1:0> | 0000         |

| 3070                        | DCH0ECON                        | 31:16                   | _      | _     | _     | _     | _           | _     | _         | _           |         |          |        | CHAIR           |                  |          |          |        | 00FF         |

|                             |                                 | 15:0                    |        |       |       | CHSIR | Q<7:0>      |       | 1         |             | CFORCE  | CABORT   | PATEN  | SIRQEN          | AIRQEN           | _        | _        | _      | FF00         |

| 3080                        | DCH0INT                         | 31:16                   | _      |       | _     | _     | _           | _     | _         | _           | CHSDIE  | CHSHIE   | CHDDIE | CHDHIE          | CHBCIE           | CHCCIE   | CHTAIE   | CHERIE | 0000         |

|                             |                                 | 15:0                    | _      |       | _     | _     | _           | _     | _         | _           | CHSDIF  | CHSHIF   | CHDDIF | CHDHIF          | CHBCIF           | CHCCIF   | CHTAIF   | CHERIF | 0000         |

| 3090                        | DCH0SSA                         | 31:16<br>15:0           |        |       |       |       |             |       |           | CHSSA       | <31:0>  |          |        |                 |                  |          |          |        | 0000         |

|                             |                                 | 31:16                   |        |       |       |       |             |       |           |             |         |          |        |                 |                  |          |          |        | 0000         |

| 30A0                        | DCHODSA   31:16   CHDSA<31:0>   |                         |        |       |       |       |             | 0000  |           |             |         |          |        |                 |                  |          |          |        |              |

|                             |                                 | 31:16                   | _      | _     | _     | _     | _           | _     | _         | _           | _       | _        | _      | _               | _                | _        | _        | _      | 0000         |

| 30B0                        | DCH0SSIZ                        | DSSIZ 15:0 CHSSIZ<15:0> |        |       |       |       |             |       | 0000      |             |         |          |        |                 |                  |          |          |        |              |

|                             |                                 | 31:16                   | _      | _     | _     | _     | _           | _     | _         | _           | _       | _        | _      | _               | _                | _        | _        | _      | 0000         |

| 30C0                        | DCH0DSIZ                        | 15:0                    |        |       |       |       |             |       |           | CHDSIZ      | Z<15:0> |          |        |                 |                  |          |          |        | 0000         |

| 0000                        | DOLLOODED                       | 31:16                   | _      | _     | _     | _     | _           | _     | _         | _           | _       | _        | _      | _               | _                | _        | _        | _      | 0000         |

| 3000                        | DCH0SPTR                        | 15:0                    | •      |       |       |       |             |       | •         | CHSPTI      | R<15:0> | •        | •      |                 | •                |          | •        | •      | 0000         |

| 30E0                        | DCH0DPTR                        | 31:16                   | _      | _     | _     | _     | _           | _     | _         | _           | _       | _        | _      | _               | _                | _        | _        | _      | 0000         |

| 30E0                        | DCHUDFIK                        | 15:0                    |        |       |       |       |             |       |           | CHDPT       | R<15:0> |          |        |                 |                  |          |          |        | 0000         |

| 30F0                        | DCH0CSIZ                        | 31:16                   | _      |       | _     | _     | _           | _     | _         | _           | _       | _        | _      | _               | _                | _        | _        | _      | 0000         |

| 001 0                       | DOI 100012                      | 15:0                    |        |       |       |       |             |       |           | CHCSIZ      | Z<15:0> |          |        |                 |                  |          |          |        | 0000         |

| 3100                        | DCH0CPTR                        | 31:16                   | _      | _     | _     | _     | _           | _     | _         | _           | _       | _        | _      | _               | _                | _        | _        | _      | 0000         |

|                             |                                 | 15:0                    |        |       |       |       |             |       |           | CHCPT       | R<15:0> |          |        |                 |                  |          |          |        | 0000         |

| 3110                        | DCH0DAT                         | 31:16                   | _      |       | _     | _     | _           | _     | _         | _           | _       | _        | _      |                 |                  | _        | _        | _      | 0000         |

|                             |                                 | 15:0                    | _      |       | _     |       |             |       | _         | _           |         |          |        | CHPDA           |                  |          |          |        | 0000         |

| 3120                        | DCH1CON                         | 31:16                   | —<br>— |       | _     | _     | _           |       | _         | -           | - CLIEN |          | -      | - CLIATNI       | _                | - CHEDET |          | -      | 0000         |

|                             |                                 | 15:0                    | CHBUSY |       | _     | _     | _           | _     | _         | CHCHNS      | CHEN    | CHAED    | CHCHN  | CHAEN           | —<br>O 47:05     | CHEDET   | CHPR     | 1<1:0> | 0000         |

| 3130                        | DCH1ECON                        | 31:16<br>15:0           | _      |       | _     | CHSIR | —<br>O<7:0> | _     | _         | _           | CFORCE  | CABORT   | PATEN  | CHAIR<br>SIRQEN | Q<7:0><br>AIRQEN | _        |          |        | 00FF<br>FF00 |

|                             |                                 | 31:16                   | _      |       | _     | CHOIR | Q~1.U~      | _     |           | _           | CHSDIE  | CHSHIE   | CHDDIE | CHDHIE          | CHBCIE           | CHCCIE   | CHTAIE   | CHERIE | 0000         |

| 3140                        | DCH1INT                         | 15:0                    | _      |       |       |       |             |       |           |             | CHSDIF  | CHSHIF   | CHDDIF | CHDHIF          | CHBCIE           | CHCCIE   | CHTAIL   | CHERIF | 0000         |

|                             |                                 | 31:16                   |        |       |       |       |             |       |           |             |         | 01101111 | OHEEN  | OHBHI           | OFFICE           | 0110011  | 01117411 | OHERM  | 0000         |

| 3150                        | DCH1SSA                         | 15:0                    |        |       |       |       |             |       |           | CHSSA       | \<31:0> |          |        |                 |                  |          |          |        | 0000         |

| <u> </u>                    |                                 | 31:16                   |        |       |       |       |             |       |           |             |         |          |        |                 |                  |          |          |        | 0000         |

| 3160                        | DCH1DSA                         | 15:0                    |        |       |       |       |             |       |           | CHDSA       | \<31:0> |          |        |                 |                  |          |          |        | 0000         |

| Legen                       |                                 |                         |        |       |       |       | - (o) D     |       | - la ! la | nevadecimal |         |          |        |                 |                  |          |          |        | 12220        |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# DS60001168J-page 105

# **USB Control Registers**

# TABLE 10-1: USB REGISTER MAP

| ess                         |                                 |               |       |       |       |       |          |       |      |      | Bit                    | s             |                   |               |               |               |             |                    |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|----------|-------|------|------|------------------------|---------------|-------------------|---------------|---------------|---------------|-------------|--------------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11    | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6          | 21/5              | 20/4          | 19/3          | 18/2          | 17/1        | 16/0               | All Resets |

| 5040                        | U1OTGIR <sup>(2)</sup>          | 31:16<br>15:0 | _     | _     |       | _     | _        |       | _    | _    | —<br>IDIF              | —<br>T1MSECIF | -<br>LSTATEIF     | —<br>ACTVIF   | —<br>SESVDIF  | —<br>SESENDIF | _           | -<br>VBUSVDIF      | 0000       |

| 5050                        | U10TGIE                         | 31:16<br>15:0 | _     | _     | _     | _     | _        | _     | _    | _    | —<br>IDIE              | —<br>T1MSECIE | —<br>LSTATEIE     | —<br>ACTVIE   | —<br>SESVDIE  | —<br>SESENDIE | _           | —<br>VBUSVDIE      | 0000       |

| 5060                        | U1OTGSTAT <sup>(3)</sup>        | 31:16         | _     | _     | _     | _     |          |       | _    | _    | _                      |               | _                 | _             | _             | _             | _           | _                  | 0000       |

| 5070                        |                                 | 15:0<br>31:16 | _     | _     |       | _     |          | _     |      |      | ID<br>—                |               | LSTATE<br>—       |               | SESVD —       | SESEND —      | _           | VBUSVD —           | 0000       |

|                             |                                 | 15:0<br>31:16 |       |       |       |       | _        |       |      | _    | DPPULUP<br>—           | DMPULUP<br>—  | DPPULDWN<br>—     | DMPULDWN<br>— | VBUSON —      | OTGEN —       | VBUSCHG     | VBUSDIS —          | 0000       |

| 5080                        | U1PWRC                          | 15:0          | _     | _     | _     | _     | _        | _     | _    | _    | UACTPND <sup>(4)</sup> | _             | _                 | USLPGRD       | USBBUSY       | _             | USUSPEND    | USBPWR             | 0000       |

| 5200                        | U1IR <sup>(2)</sup>             | 31:16<br>15:0 |       | _     | _     | _     |          | _     | _    | _    | STALLIF                | —<br>ATTACHIF | RESUMEIF          | IDLEIF        | TRNIF         | SOFIF         | UERRIF      | URSTIF<br>DETACHIF | 0000       |

|                             |                                 | 31:16         | _     | _     | -     | _     | _        | _     | -    | _    | _                      | _             | _                 | _             | _             | _             | _           | _                  | 0000       |

| 5210                        | U1IE                            | 15:0          | _     | _     | -     | _     | -        | _     | -    | _    | STALLIE                | ATTACHIE      | RESUMEIE          | IDLEIE        | TRNIE         | SOFIE         | UERRIE      | URSTIE DETACHIE    | 0000       |

| 5220                        | U1EIR <sup>(2)</sup>            | 31:16         | _     | _     |       | _     | _        |       |      | _    | _                      | _             | _                 | _             | _             | _             | —<br>CRC5EF | _                  | 0000       |

| 5220                        |                                 | 15:0          | _     | _     |       | _     | _        | _     | -    | _    | BTSEF                  | BMXEF         | DMAEF             | BTOEF         | DFN8EF        | CRC16EF       | EOFEF       | PIDEF              | 0000       |

| 5230                        | U1EIE                           | 31:16         | _     |       | _     | _     |          |       |      |      |                        |               | _                 | _             | _             | _             | CRC5EE      | _                  | 0000       |

|                             |                                 | 15:0          | _     | _     |       | _     | _        | _     |      | _    | BTSEE                  | BMXEE         | DMAEE             | BTOEE         | DFN8EE        | CRC16EE       | EOFEE       | PIDEE              | 0000       |

| 5240                        | U1STAT <sup>(3)</sup>           | 31:16<br>15:0 | _     | _     | _     | _     |          | _     | _    | _    | _                      | —<br>ENDF     | T<3:0>            | _             | DIR           | PPBI          | _           | _                  | 0000       |

|                             |                                 | 31:16         | _     | _     | _     | _     |          | _     | _    | _    | _                      | _             | —<br>DICTRIC      | _             | _             | _             | _           | _                  | 0000       |

| 5250                        | U1CON                           | 15:0          | _     | _     | _     | _     | _        | _     | _    | _    | JSTATE                 | SE0           | PKTDIS<br>TOKBUSY | USBRST        | HOSTEN        | RESUME        | PPBRST      | USBEN<br>SOFEN     | 0000       |

| 5260                        | U1ADDR                          | 31:16<br>15:0 |       |       |       |       |          |       |      |      | —<br>LSPDEN            | _             | _                 |               | —<br>VADDR<6: | <u> </u>      | _           | _                  | 0000       |

| 5270                        | U1BDTP1                         | 31:16         | _     | _     |       | _     |          |       |      | _    | —                      | _             | _                 | _             | _             | _             | _           | _                  | 0000       |

| ,                           | ··                              | 15:0          | — D   | _     | _     | _     | <u> </u> |       | _    |      |                        |               | BD                | TPTRL<15:9    | •             |               |             | _                  | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined.

TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral Selection          |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> | 0100 = Reserved<br>0101 = OC1               |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | :                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                                |

| RPC8         | RPC8R    | RPC8R<3:0>  | <b></b> :                                   |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 = OC4                                  |

| RPB2         | RPB2R    | RPB2R<3:0>  | 0110 = OC5<br>0111 = REFCLKO                |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  | :                                           |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> | 0001 = U1RTS<br>0010 = U2TX                 |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 = OC3                                  |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  | <b></b> :                                   |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

## REGISTER 17-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 **ENHBUF**: Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- bit 15 **ON:** SPI Peripheral On bit<sup>(1)</sup>

- 1 = SPI Peripheral is enabled

- 0 = SPI Peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 DISSDO: Disable SDOx pin bit

- 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register

- 0 = SDOx pin is controlled by the module

- bit 11-10 MODE<32.16>: 32/16-Bit Communication Select bits

### When AUDEN = 1:

| MODE32 | MODE16 | Communication                                         |

|--------|--------|-------------------------------------------------------|

| 1      | 1      | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame |

| 1      | 0      | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame |

| 0      | 1      | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame |

| 0      | 0      | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame |

### When AUDEN = 0:

| MODE32 | MODE16 | Communication |

|--------|--------|---------------|

| 1      | x      | 32-bit        |

| 0      | 1      | 16-bit        |

| 0      | 0      | 8-bit         |

|        |        |               |

bit 9 SMP: SPI Data Input Sample Phase bit

### Master mode (MSTEN = 1):

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

### Slave mode (MSTEN = 0):

SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.

To write a '1' to this bit, the MSTEN value = 1 must first be written.

- bit 8 **CKE**: SPI Clock Edge Select bit<sup>(3)</sup>

- 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)

- 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)

- bit 7 SSEN: Slave Select Enable (Slave mode) bit

- $1 = \overline{SSx}$  pin used for Slave mode

- $0 = \overline{SSx}$  pin not used for Slave mode, pin controlled by port function.

- bit 6 **CKP:** Clock Polarity Select bit<sup>(4)</sup>

- 1 = Idle state for clock is a high level; active state is a low level

- 0 = Idle state for clock is a low level; active state is a high level

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

# REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits(1)

- 11 = Wait of 4 TPB

- 10 = Wait of 3 TPB

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

### For Read operations:

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- Note 1: Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 ΤΡΒCLK cycle for a write operation; WAITB = 1 ΤΡΒCLK cycle, WAITE = 0 ΤΡΒCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

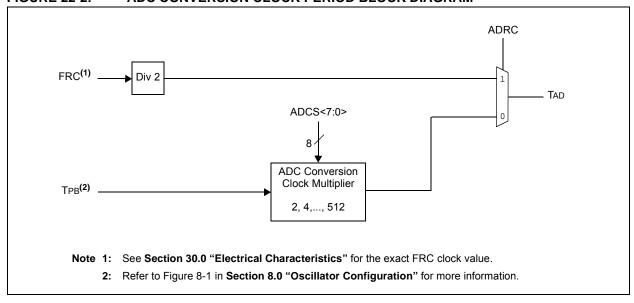

# FIGURE 22-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2     | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-----------------------|-------------------------|------------------|

| 24.24        | r-0               | r-1               | r-1               | R/P               | r-1                  | r-1                   | r-1                     | R/P              |

| 31:24        |                   | _                 | _                 | CP                | _                    | _                     |                         | BWP              |

| 22.46        | r-1               | r-1               | r-1               | r-1               | r-1                  | R/P                   | R/P                     | R/P              |

| 23:16        |                   | _                 | _                 | _                 | _                    | I                     | PWP<8:6> <sup>(3)</sup> |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                  | R/P                   | r-1                     | r-1              |

| 15:8         | PWP<5:0>          |                   |                   |                   |                      |                       | _                       |                  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P                  | R/P                   | R/P                     | R/P              |

| 7:0          | _                 | _                 |                   | ICESEL            | <1:0> <sup>(2)</sup> | JTAGEN <sup>(1)</sup> | DEBU                    | G<1:0>           |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-19 Reserved: Write '1'

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users

### Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

|               |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                 |                        |            |       |                                                   |

|---------------|--------|-----------------------------------------------------------------------|-----------------|------------------------|------------|-------|---------------------------------------------------|

| Param.<br>No. | Symbol | Characteristics                                                       | Min.            | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |

|               | VIL    | Input Low Voltage                                                     |                 |                        |            |       |                                                   |

| DI10          |        | I/O Pins with PMP                                                     | Vss             | _                      | 0.15 VDD   | V     |                                                   |

|               |        | I/O Pins                                                              | Vss             | _                      | 0.2 VDD    | V     |                                                   |

| DI18          |        | SDAx, SCLx                                                            | Vss             | _                      | 0.3 VDD    | V     | SMBus disabled (Note 4)                           |

| DI19          |        | SDAx, SCLx                                                            | Vss             | _                      | 0.8        | V     | SMBus enabled (Note 4)                            |

|               | VIH    | Input High Voltage                                                    |                 |                        |            |       |                                                   |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                               | 0.65 VDD        | _                      | VDD        | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant with PMP <sup>(5)</sup>                          | 0.25 VDD + 0.8V | _                      | 5.5        | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant(5)                                               | 0.65 VDD        | _                      | 5.5        | V     |                                                   |

| DI28          |        | SDAx, SCLx                                                            | 0.65 VDD        | _                      | 5.5        | V     | SMBus disabled (Note 4,6)                         |

| DI29          |        | SDAx, SCLx                                                            | 2.1             | _                      | 5.5        | V     | SMBus enabled, $2.3V \le VPIN \le 5.5$ (Note 4,6) |

| DI30          | ICNPU  | Change Notification Pull-up Current                                   | _               | _                      | -50        | μА    | VDD = 3.3V, VPIN = VSS (Note 3,6)                 |

| DI31          | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup>               | _               | _                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |

|               | liL    | Input Leakage Current (Note 3)                                        |                 |                        |            |       |                                                   |

| DI50          |        | I/O Ports                                                             | _               | _                      | <u>+</u> 1 | μΑ    | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance        |

| DI51          |        | Analog Input Pins                                                     | _               | _                      | <u>+</u> 1 | μΑ    | VSS ≤ VPIN ≤ VDD,<br>Pin at high-impedance        |

| DI55          |        | MCLR <sup>(2)</sup>                                                   | _               | _                      | <u>+</u> 1 | μΑ    | Vss ≤ Vpin ≤ Vdd                                  |

| DI56          |        | OSC1                                                                  | _               | _                      | <u>+</u> 1 | μA    | VSS ≤ VPIN ≤ VDD,<br>XT and HS modes              |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- **4:** This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- **6:** The Vih specifications are only in relation to externally applied inputs, and not with respect to the user-selectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum Vih of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

TABLE 30-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$  for V-temp

| Param.<br>No. | Symbol    | Characteristics <sup>(1)</sup>                            |                             | Min.                                      | Max. | Units | Condit                        | ions                  |

|---------------|-----------|-----------------------------------------------------------|-----------------------------|-------------------------------------------|------|-------|-------------------------------|-----------------------|

| TB10          | ТтхН      | TxCK<br>High Time                                         | Synchronous, with prescaler | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns         | _    | ns    | Must also meet parameter TB15 | value<br>(1, 2, 4, 8, |

| TB11          | TTXL      | TxCK<br>Low Time                                          | Synchronous, with prescaler | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns         | _    | ns    | Must also meet parameter TB15 | 16, 32, 64,<br>256)   |

| TB15          | TTXP      | TxCK<br>Input                                             | Synchronous, with prescaler | [(Greater of [(25 ns or 2 TPB)/N] + 30 ns | _    | ns    | VDD > 2.7V                    |                       |

|               |           | Period                                                    |                             | [(Greater of [(25 ns or 2 TPB)/N] + 50 ns | _    | ns    | VDD < 2.7V                    |                       |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                             | _                                         | 1    | Трв   |                               |                       |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

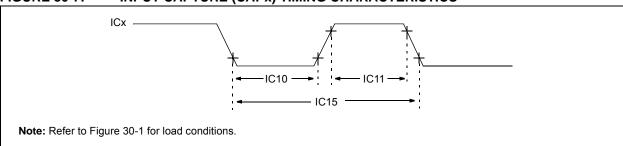

# FIGURE 30-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

### TABLE 30-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| IADEL                                                                                                                                                                                                                                                             | <del></del> |           |                           | DOLL TIMING KEQUIK                |      |       |                                         |                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|---------------------------|-----------------------------------|------|-------|-----------------------------------------|----------------------------------|

| AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |             |           |                           |                                   |      |       |                                         |                                  |

| Param.<br>No.                                                                                                                                                                                                                                                     | Symbol      | Charac    | cteristics <sup>(1)</sup> | Min.                              | Max. | Units | Cor                                     | nditions                         |

| IC10                                                                                                                                                                                                                                                              | TccL        | ICx Input | t Low Time                | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |

| IC11                                                                                                                                                                                                                                                              | TccH        | ICx Input | t High Time               | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns | _    | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |

| IC15                                                                                                                                                                                                                                                              | TccP        | ICx Input | t Period                  | [(25 ns or 2 TPB)/N]<br>+ 50 ns   | _    | ns    | _                                       |                                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

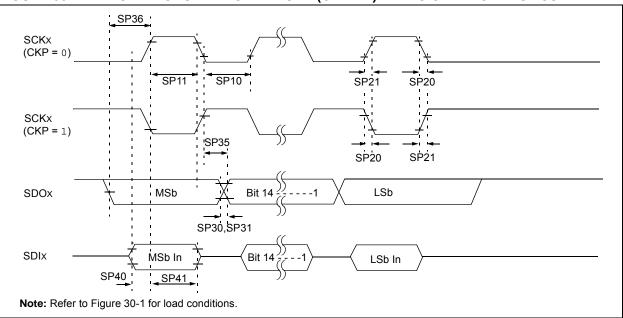

FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                      |                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industria $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                     |      |       |                    |

|--------------------|----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>            | Min.                                                                                                                                                                                                                                          | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                 | SCKx Output Low Time (Note 3)             | Tsck/2                                                                                                                                                                                                                                        | _                   | _    | ns    | _                  |

| SP11               | TscH                 | SCKx Output High Time (Note 3)            | Tsck/2                                                                                                                                                                                                                                        | _                   | _    | ns    | _                  |

| SP20               | TscF                 | SCKx Output Fall Time (Note 4)            | _                                                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO32 |

| SP21               | TscR                 | SCKx Output Rise Time (Note 4)            | _                                                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO31 |

| SP30               | TDOF                 | SDOx Data Output Fall Time (Note 4)       | _                                                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO32 |

| SP31               | TDOR                 | SDOx Data Output Rise Time (Note 4)       | _                                                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO31 |

| SP35               | TscH2DoV,            | SDOx Data Output Valid after              |                                                                                                                                                                                                                                               | _                   | 15   | ns    | VDD > 2.7V         |

|                    | TscL2DoV             | SCKx Edge                                 | _                                                                                                                                                                                                                                             | _                   | 20   | ns    | VDD < 2.7V         |

| SP36               | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to First SCKx Edge | 15                                                                                                                                                                                                                                            | _                   | _    | ns    | _                  |

| SP40               | TDIV2scH,            | Setup Time of SDIx Data Input to          | 15                                                                                                                                                                                                                                            | _                   | _    | ns    | VDD > 2.7V         |

|                    | TDIV2scL             | SCKx Edge                                 | 20                                                                                                                                                                                                                                            | _                   | _    | ns    | VDD < 2.7V         |

| SP41               | TscH2DIL,            | Hold Time of SDIx Data Input              | 15                                                                                                                                                                                                                                            | _                   | _    | ns    | VDD > 2.7V         |

|                    | TscL2DIL             | to SCKx Edge                              | 20                                                                                                                                                                                                                                            | _                   | _    | ns    | VDD < 2.7V         |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHA        | RACTERIS     | STICS                       |                        | (unless other | rwise st | <b>ated)</b><br>re -40° | ons: 2.3V to 3.6V<br>$C \le TA \le +85^{\circ}C$ for Industrial $C \le TA \le +105^{\circ}C$ for V-temp |

|---------------|--------------|-----------------------------|------------------------|---------------|----------|-------------------------|---------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol       | Charact                     | Min.                   | Max.          | Units    | Conditions              |                                                                                                         |

| IS34          | THD:STO      | Stop Condition<br>Hold Time | 100 kHz mode           | 4000          | _        | ns                      | _                                                                                                       |

|               |              |                             | 400 kHz mode           | 600           | _        | ns                      |                                                                                                         |

|               |              |                             | 1 MHz mode<br>(Note 1) | 250           |          | ns                      |                                                                                                         |

| IS40          | S40 TAA:SCL  | Output Valid from Clock     | 100 kHz mode           | 0             | 3500     | ns                      | _                                                                                                       |

|               |              |                             | 400 kHz mode           | 0             | 1000     | ns                      |                                                                                                         |

|               |              |                             | 1 MHz mode<br>(Note 1) | 0             | 350      | ns                      |                                                                                                         |

| IS45          | IS45 TBF:SDA | F:SDA Bus Free Time         | 100 kHz mode           | 4.7           | _        | μS                      | The amount of time the bus                                                                              |

|               |              |                             | 400 kHz mode           | 1.3           |          | μS                      | must be free before a new                                                                               |

|               |              |                             | 1 MHz mode<br>(Note 1) | 0.5           | _        | μS                      | transmission can start                                                                                  |

| IS50          | Св           | Bus Capacitive Lo           | ading                  | _             | 400      | pF                      | _                                                                                                       |

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

# 31.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 30.0** "**Electrical Characteristics**", with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 30.0** "**Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# **Absolute Maximum Ratings**

### (See Note 1)

| Ambient temperature under bias                                              | 40°C to +85°C            |

|-----------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                         | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                          | 0.3V to +4.0V            |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)    | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 2.3V (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3) | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to Vusb3v3                             | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                         | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                           | 300 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                    | 300 mA                   |

| Maximum output current sunk by any I/O pin                                  | 15 mA                    |

| Maximum output current sourced by any I/O pin                               | 15 mA                    |

| Maximum current sunk by all ports                                           | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                               | 200 mA                   |