#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 256КВ (256К х 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256b-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

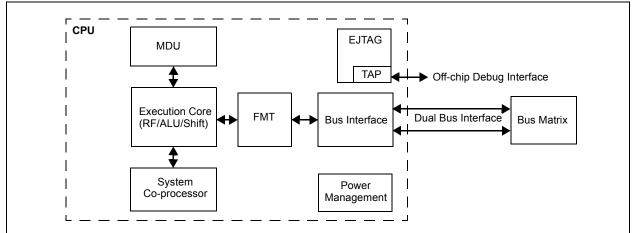

## 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

## 3.1 Features

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

## FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

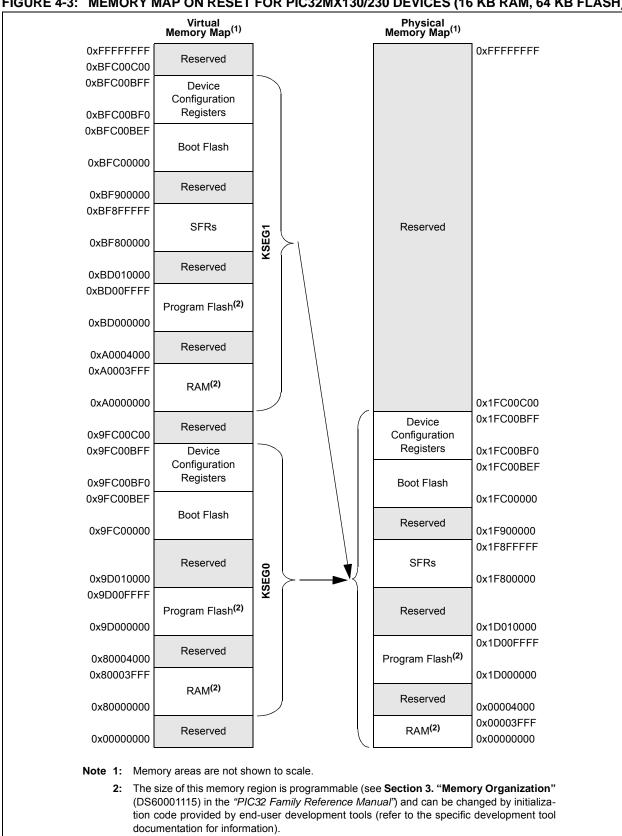

### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R R R R R R R     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |  |  |

### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00004000 = Device has 16 KB Flash 0x00008000 = Device has 32 KB Flash 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash

## REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |   |   |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |   |  |  |  |  |  |  |

|--------------|----------------------------------|---|---|-------|-------------------|------------------|------------------|---|--|--|--|--|--|--|

| 24.24        | R                                | R | R | R     | R                 | R                | R                | R |  |  |  |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>                 |   |   |       |                   |                  |                  |   |  |  |  |  |  |  |

| 00.40        | R                                | R | R | R     | R                 | R                | R                | R |  |  |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>                 |   |   |       |                   |                  |                  |   |  |  |  |  |  |  |

| 45.0         | R                                | R | R | R     | R                 | R                | R                | R |  |  |  |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>                  |   |   |       |                   |                  |                  |   |  |  |  |  |  |  |

| 7.0          | R                                | R | R | R     | R                 | R                | R                | R |  |  |  |  |  |  |

| 7:0          |                                  |   |   | BMXBO | OTSZ<7:0>         |                  |                  |   |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00000C00 = Device has 3 KB boot Flash

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

## REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

### Legend:

| 0                 |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

## REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| =0901141          |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                       |           |       |       |       |       |       |       |      | Bi   | its  |      |      |      |           |      |       |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|-----------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) |                       | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3      | 18/2 | 17/1  | 16/0 | All Resets |

| FB00                        | RPA0R                 | 31:16     |       | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    | —         | —    | —     | —    | 0000       |

|                             |                       | 15:0      | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    |           | RPA0 | <3:0> |      | 0000       |

| FB04                        | RPA1R                 | 31:16     | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    | —         | —    | —     | —    | 0000       |

| 1 001                       |                       | 15:0      | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    |           | RPA1 | <3:0> |      | 0000       |

| FB08                        | RPA2R                 | 31:16     | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    | —         | —    | —     | —    | 0000       |

| 1 000                       | i (i / t <u>2</u> i ( | 15:0      | —     | —     | -     | —     | —     | _     | —    | —    | _    | —    | —    | —    |           | RPA2 | <3:0> |      | 0000       |

| FB0C                        | RPA3R                 | 31:16     | _     | _     | —     | —     | _     | _     | _    | _    | _    | —    | _    | _    | _         | —    |       | —    | 0000       |

| T BOC                       |                       | 15:0      | _     |       | —     | _     | _     | _     | —    | _    | _    |      | —    | _    |           | RPA3 | <3:0> |      | 0000       |

| FB10                        | RPA4R                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _    | _         |      |       | —    | 0000       |

| T D IO                      |                       | 15:0      | —     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    |           | RPA4 | <3:0> |      | 0000       |

| FB20                        | RPA8R <sup>(1)</sup>  | 31:16     | —     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    | _         | —    | —     | —    | 0000       |

| 1 020                       | KFAOK'                | 15:0      | _     | —     | —     | —     | _     |       | —    | _    |      | —    | —    | —    |           | RPA8 | <3:0> |      | 0000       |

| FB24                        | RPA9R <sup>(1)</sup>  | 31:16     | —     | —     | —     | —     | -     |       | —    | -    |      | _    | —    | —    | -         | —    | _     | —    | 0000       |

| 1 D24                       | KFA9K /               | 15:0      | —     | —     | —     | —     | -     |       | —    | -    |      | —    | —    | —    | RPA9<3:0> |      |       |      | 0000       |

| FB2C                        | RPB0R                 | 31:16     | _     | _     | —     | —     | _     | -     | _    | _    | -    | —    | _    | —    | _         | _    | _     | —    | 0000       |

| 1 020                       | KF DUK                | 15:0      | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    |           | RPB0 | <3:0> |      | 0000       |

| FB30                        | RPB1R                 | 31:16     | —     | _     | —     | —     |       |       | —    |      |      | —    | —    | —    |           | _    | —     | —    | 0000       |

| FB30                        | REDIR                 | 15:0      | —     | _     | —     | —     |       |       | —    |      |      | —    | —    | —    |           | RPB1 | <3:0> |      | 0000       |

| FB34                        | RPB2R                 | 31:16     | _     | _     | _     | _     |       |       | _    |      |      | _    | _    | _    |           | _    | _     | —    | 0000       |

| FB34                        | RPBZR                 | 15:0      | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |           | RPB2 | <3:0> |      | 0000       |

| FB38                        | RPB3R                 | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —    | _         | _    | _     | _    | 0000       |

| FB30                        | RPBJR                 | 15:0      | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |           | RPB3 | <3:0> |      | 0000       |

| <b>FD2C</b>                 |                       | 31:16     | —     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    | —         | —    | —     | —    | 0000       |

| FB3C                        | RPB4R                 | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPB4 | <3:0> |      | 0000       |

| ED 40                       |                       | 31:16     |       |       | —     | —     | —     | -     | —    | —    | —    | —    | —    | —    | _         |      |       | —    | 0000       |

| FB40                        | RPB5R                 | 15:0      | _     |       | —     |       |       |       |      |      |      |      |      |      |           | RPB5 | <3:0> |      | 0000       |

| 5044                        |                       | 31:16     | _     | —     | _     | —     | —     | _     | _    | _    | _    | —    | _    | —    | _         | _    | _     | —    | 0000       |

| FB44                        | RPB6R <sup>(2)</sup>  | 15:0      | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    |           | RPB6 | <3:0> |      | 0000       |

| 50.40                       |                       | 31:16     | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    | _         | _    | _     | —    | 0000       |

| FB48                        | RPB7R                 | 15:0      | _     | —     | _     | —     | _     | _     | _    | _    | _    | —    | _    | —    |           | RPB7 | <3:0> |      | 0000       |

DS60001168J-page 138

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: This register is only available on PIC32MX1XX devices.

3: This register is only available on 36-pin and 44-pin devices. PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## 12.2 Timer1 Control Registers

## TABLE 12-1: TIMER1 REGISTER MAP

| ess                       |                                 | 0         |       |       |       |       |       |       |      | В    | its    |      |       |        |      |       |      |      | s          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | —     | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON    | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —     | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      |       |       |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000       |

| 0620                      | PR1                             | 31:16     | —     | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                             | 15:0      |       |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| REGIST    | ER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                         |  |  |  |  |  |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                             |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                         |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                               |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 16    | <b>ENHBUF:</b> Enhanced Buffer Enable bit <sup>(2)</sup><br>1 = Enhanced Buffer mode is enabled            |  |  |  |  |  |  |  |  |  |  |  |  |

|           | <ul><li>1 = Enhanced Buffer mode is enabled</li><li>0 = Enhanced Buffer mode is disabled</li></ul>         |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer mode is disabled                                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 15    | <b>DN:</b> SPI Peripheral On bit <sup>(1)</sup>                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = SPI Peripheral is enabled                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = SPI Peripheral is disabled                                                                             |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Discontinue module operation when the device enters Idle mode                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Continue module operation when the device enters Idle mode                                             |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDOx pin bit                                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                      |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = SDOx pin is controlled by the module                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                           |  |  |  |  |  |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 1 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 0 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                  |  |  |  |  |  |  |  |  |  |  |  |  |

|           |                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 	 1 	 10-51                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 5     | Master mode (MSTEN = 1):                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Input data sampled at end of data output time                                                          |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Input data sampled at middle of data output time                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

|           | Slave mode (MSTEN = 0):                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                       |  |  |  |  |  |  |  |  |  |  |  |  |

|           | To write a '1' to this bit, the MSTEN value = 1 must first be written.                                     |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                              |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit) |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit) |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |

|           | $1 = \overline{SSx}$ pin used for Slave mode                                                               |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = SSx pin not used for Slave mode, pin controlled by port function.                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| bit 6     | <b>CKP:</b> Clock Polarity Select bit <sup>(4)</sup>                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                      |  |  |  |  |  |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock is a low level; active state is a high level                                      |  |  |  |  |  |  |  |  |  |  |  |  |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in    |  |  |  |  |  |  |  |  |  |  |  |  |

|           | the SYSCLK cycle immediately following the instruction that clears the module's ON bit.                    |  |  |  |  |  |  |  |  |  |  |  |  |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                       |  |  |  |  |  |  |  |  |  |  |  |  |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI    |  |  |  |  |  |  |  |  |  |  |  |  |

|           | mode (FRMEN = 1).                                                                                          |  |  |  |  |  |  |  |  |  |  |  |  |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value |  |  |  |  |  |  |  |  |  |  |  |  |

|           | of CKP.                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |

|           |                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |

2

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

## 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

## Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

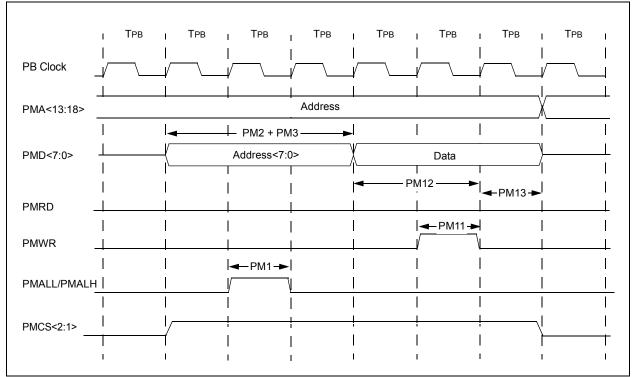

## REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 Трв

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 ТРВ

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | _                     | -                 | _                 | -                 | -                 | _                | _                |  |  |

| 23:16        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:10        | —                 | —                     |                   | _                 |                   | _                 | _                | _                |  |  |

|              | U-0               | R/W-0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   | CS1 <sup>(1)</sup>    |                   |                   |                   |                   |                  |                  |  |  |

|              | —                 | ADDR14 <sup>(2)</sup> | _                 |                   | _                 |                   | ADDR<10:8>       |                  |  |  |

| 7:0          | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | ADDR<7:0>         |                       |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 14 **CS1:** Chip Select 1 bit<sup>(1)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Destination Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

NOTES:

### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read

If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

| DC CHA        | RACTER | ISTICS                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |       |     |        |                                               |  |  |

|---------------|--------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------|-----------------------------------------------|--|--|

| Param.<br>No. | Symbol | Characteristics                      | Min. Typical <sup>(1)</sup> Max. Units Conditions                                                                                                                                                                                                                               |       |     |        |                                               |  |  |

|               |        | Program Flash Memory <sup>(3)</sup>  |                                                                                                                                                                                                                                                                                 |       |     |        |                                               |  |  |

| D130          | Eр     | Cell Endurance                       | 20,000                                                                                                                                                                                                                                                                          | —     | _   | E/W    | —                                             |  |  |

| D131          | Vpr    | VDD for Read                         | 2.3                                                                                                                                                                                                                                                                             | —     | 3.6 | V      | —                                             |  |  |

| D132          | VPEW   | VDD for Erase or Write               | 2.3                                                                                                                                                                                                                                                                             | —     | 3.6 | V      | —                                             |  |  |

| D134          | Tretd  | Characteristic Retention             | 20                                                                                                                                                                                                                                                                              | —     | _   | Year   | Provided no other specifications are violated |  |  |

| D135          | IDDP   | Supply Current during<br>Programming | _                                                                                                                                                                                                                                                                               | 10    | _   | mA     | —                                             |  |  |

|               | Tww    | Word Write Cycle Time                | —                                                                                                                                                                                                                                                                               | 411   | _   | es     | See Note 4                                    |  |  |

| D136          | Trw    | Row Write Cycle Time                 | —                                                                                                                                                                                                                                                                               | 6675  | _   | Cycles | See Note 2,4                                  |  |  |

| D137          | TPE    | Page Erase Cycle Time                | —                                                                                                                                                                                                                                                                               | 20011 | _   |        | See Note 4                                    |  |  |

|               | TCE    | Chip Erase Cycle Time                | —                                                                                                                                                                                                                                                                               | 80180 | _   | FRC    | See Note 4                                    |  |  |

### TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

| AC CHA        | AC CHARACTERISTICS |                                                                      |         | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 4): 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |                                                           |  |  |

|---------------|--------------------|----------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----------------------------------------------------------|--|--|

| Param.<br>No. | Symbol             | Characteristics                                                      | Units   | Conditions                                                                                                                                                                                                                                                                                         |         |      |                                                           |  |  |

| Clock P       | arameters          | S                                                                    | •       | •                                                                                                                                                                                                                                                                                                  |         |      |                                                           |  |  |

| AD50          | TAD                | ADC Clock Period <sup>(2)</sup>                                      | 65      | _                                                                                                                                                                                                                                                                                                  | —       | ns   | See Table 30-35                                           |  |  |

| Convers       | sion Rate          |                                                                      |         |                                                                                                                                                                                                                                                                                                    |         |      |                                                           |  |  |

| AD55          | TCONV              | Conversion Time                                                      | _       | 12 Tad                                                                                                                                                                                                                                                                                             | —       | _    | —                                                         |  |  |

| AD56          | FCNV               | Throughput Rate                                                      | —       | —                                                                                                                                                                                                                                                                                                  | 1000    | ksps | AVDD = 3.0V to 3.6V                                       |  |  |

|               |                    | (Sampling Speed)                                                     | —       | —                                                                                                                                                                                                                                                                                                  | 400     | ksps | AVDD = 2.5V to 3.6V                                       |  |  |

| AD57          | TSAMP              | Sample Time                                                          | 1 Tad   | —                                                                                                                                                                                                                                                                                                  | —       | —    | TSAMP must be $\geq$ 132 ns                               |  |  |

| Timing        | Paramete           | rs                                                                   |         |                                                                                                                                                                                                                                                                                                    |         |      |                                                           |  |  |

| AD60          | TPCS               | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               |         | 1.0 Tad                                                                                                                                                                                                                                                                                            |         | _    | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |  |  |

| AD61          | TPSS               | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 Tad | —                                                                                                                                                                                                                                                                                                  | 1.5 Tad | _    | _                                                         |  |  |

| AD62          | TCSS               | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | —       | 0.5 Tad                                                                                                                                                                                                                                                                                            | —       |      | _                                                         |  |  |

| AD63          | TDPU               | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _       | _                                                                                                                                                                                                                                                                                                  | 2       | μS   | _                                                         |  |  |

## TABLE 30-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| AC CHARACTERISTICS |         |                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |

|--------------------|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                            | Тур.  | Max. | Units | Conditions |  |

| PM1                | Tlat    | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                                                 | 1 Трв | _    | _     | _          |  |

| PM2                | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                                                                                                                                                                                                                                               | 2 Трв | _    | _     | _          |  |

| PM3                | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                               | 1 Трв | _    | —     | _          |  |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                               | _     | _    | ns    | _          |  |

| PM5                | Trd     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                               | 1 Трв | _    | _     | —          |  |

| PM6                | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                              | —     | —    | ns    | _          |  |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | —                                                                                                                                                                                                                                                                               | 80    | —    | ns    |            |  |

### TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

## TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |          |  |                               |

|--------------------|--------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|--|-------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                                    | Min. Typical Max. Units Co                                                                                                                      |  |          |  |                               |

| MOS10              |        | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4                                                                                                                                         |  | 50<br>50 |  | EC (Note 2)<br>ECPLL (Note 1) |

Note 1: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

**2:** This parameter is characterized, but not tested in manufacturing.

## TABLE 31-6:SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS                   |      |                                    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |      |       |            |

|--------------------------------------|------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No. Symbol Characteristics |      |                                    | Min.                                                                                                                                            | Typical | Max. | Units | Conditions |

| MSP10                                | TscL | SCKx Output Low Time<br>(Note 1,2) | Тѕск/2                                                                                                                                          |         | —    | ns    | _          |

| MSP11                                | TscH | SCKx Output High Time (Note 1,2)   | Tscк/2                                                                                                                                          |         | —    | ns    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

## TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |       |            |

|--------------------|--------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>      | Min.                                                                                                                                            | Тур. | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2)  | Тѕск/2                                                                                                                                          | —    | _    | ns    | —          |

| MSP11              | TSCH   | SCKx Output High Time<br>(Note 1,2) | Тѕск/2                                                                                                                                          | —    | —    | ns    | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

## Revision J (April 2016)

This revision includes the following major changes as described in Table A-8, as well as minor updates to text and formatting, which were incorporated throughout the document.

## TABLE A-8: MAJOR SECTION UPDATES

| Section                                                                                                                                | Update Description                                                                                                                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| "32-bit Microcontrollers (up to<br>256 KB Flash and 64 KB<br>SRAM) with Audio and<br>Graphics Interfaces, USB, and<br>Advanced Analog" | The PIC32MX270FDB device and Note 4 were added to <b>TABLE 2: "PIC32MX2XX</b><br><b>28/36/44-pin USB Family Features"</b> .       |  |  |  |  |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | EXAMPLE 2-1: "Crystal Load Capacitor Calculation" was updated.                                                                    |  |  |  |  |

| 30.0 "Electrical<br>Characteristics"                                                                                                   | Parameter DO50a (Csosc) was removed from the Capacitive Loading Requirements on Output Pins AC Characteristics (see Table 30-16). |  |  |  |  |

| "Product Identification<br>System"                                                                                                     | The device mapping was updated to include type B for Software Targeting.                                                          |  |  |  |  |