#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256b-v-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

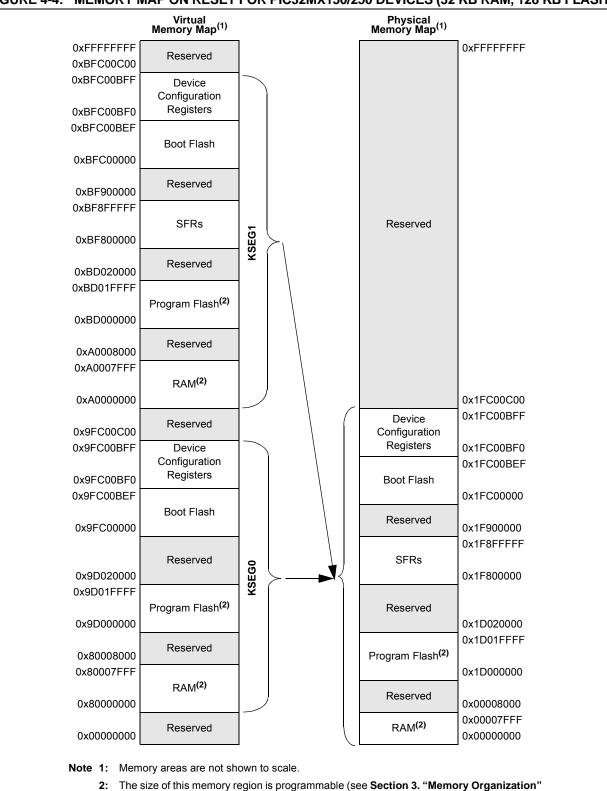

## FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

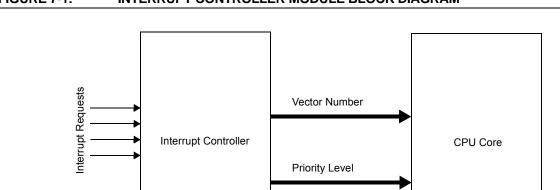

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

## FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | _                | —                |

| 00.40        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 7:0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | —                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

## REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-----------------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|--|--|

|              | U-0                         | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | _                           | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

|              | R/W-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                              |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0                       | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |  |

| 15:8         | ON                          | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |  |

|              | U-0                         | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                             |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |  |  |

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## 11.1 Parallel I/O (PIO) Ports

All port pins have 10 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

## 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Pin Diagrams"** section for the available pins and their functionality.

## 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

## 11.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX1XX/2XX 28/36/44-pin Family devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

An additional control register (CNCONx) is shown in Register 11-3.

## 11.2 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR, or INV register, the base register must be read.

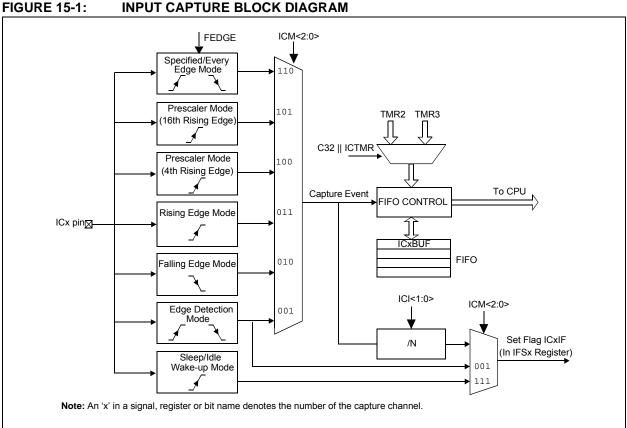

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

#### 15.1 **Input Capture Control Registers**

|                             | LE 15-1:              | IN            | PUT C | APTURE | E 1-INPU | JT CAPI | TURE 5 | REGIST | rer mai | 2      |        |      |      |       |       |          |          |

|-----------------------------|-----------------------|---------------|-------|--------|----------|---------|--------|--------|---------|--------|--------|------|------|-------|-------|----------|----------|

| ess                         |                       |               |       |        |          |         |        |        |         | Bi     | ts     |      |      |       |       |          |          |

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14  | 29/13    | 28/12   | 27/11  | 26/10  | 25/9    | 24/8   | 23/7   | 22/6 | 21/5 | 20/4  | 19/3  | 18/2     | 17/1     |

|                             | IC1CON <sup>(1)</sup> | 31:16         |       | _      | —        | —       | —      | —      | _       | —      | —      | —    |      | —     | —     | —        | —        |

| 2000 1010010                | 15:0                  | ON            | —     | SIDL   | —        | —       | —      | FEDGE  | C32     | ICTMR  | ICI<   | 1:0> | ICOV | ICBNE |       | ICM<2:0> |          |

| 2010                        | IC1BUF                | 31:16<br>15:0 |       |        |          |         |        |        |         | IC1BUF | <31:0> |      |      |       |       |          |          |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         |       | —      | —        | —       | —      | —      | —       | —      | _      | —    | _    | —     | _     | —        | —        |

| 2200                        | 1020011               | 15:0          | ON    | —      | SIDL     | —       |        | —      | FEDGE   | C32    | ICTMR  | ICI< | 1:0> | ICOV  | ICBNE |          | ICM<2:0> |

| 2210                        | IC2BUF                | 31:16<br>15:0 |       |        |          |         |        |        |         | IC2BUF | <31:0> |      |      |       |       |          |          |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         |       | _      | —        | _       | _      | _      | —       | _      | —      | -    | _    | —     | _     | _        | —        |

| 2400                        | 1030011               | 15:0          | ON    | —      | SIDL     | —       |        | —      | FEDGE   | C32    | ICTMR  | ICI< | 1:0> | ICOV  | ICBNE |          | ICM<2:0> |

| 2410                        | IC3BUF                | 31:16<br>15:0 |       |        |          |         |        |        |         | IC3BUF | <31:0> |      |      |       |       |          |          |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         | -     | _      | —        | _       | -      | _      | —       | —      | _      | _    | _    | —     | —     | _        | —        |

| 2000                        | 1040010               | 15:0          | ON    | —      | SIDL     | —       |        | —      | FEDGE   | C32    | ICTMR  | ICI< | 1:0> | ICOV  | ICBNE |          | ICM<2:0> |

| 2610                        | IC4BUF                | 31:16<br>15:0 |       |        |          |         |        |        |         | IC4BUF | <31:0> |      |      |       |       |          |          |

| 2800                        | IC5CON <sup>(1)</sup> | 31:16         | -     | _      | —        | _       | -      | _      | —       | —      | —      | _    | _    | —     | —     | _        | —        |

| 2000                        | 1030011               | 15:0          | ON    | —      | SIDL     | —       | —      | —      | FEDGE   | C32    | ICTMR  | ICI< | 1:0> | ICOV  | ICBNE |          | ICM<2:0> |

| 2810                        | IC5BUF                | 31:16<br>15:0 |       |        |          |         |        |        |         | IC5BUF | <31:0> |      |      |       |       |          |          |

#### Т

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

All Resets

0000

0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx

16/0

—

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | —                  |                   | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | —                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

## REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

- 111 = Reserved; do not use

- 110 = Reserved; do not use

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

- 1 = REFCLK is used by the Baud Rate Generator

- 0 = PBCLK is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

## 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

## REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 ADDEN: Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected **OERR:** Receive Buffer Overrun Error Status bit. bit 1 This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

NOTES:

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | —                | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | -                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ADRC              | _                 | —                 |                   |                   | SAMC<4:0>(1)      |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W              | R/W-0            |

| 7:0          |                   |                   |                   | ADCS<             | 7:0> <b>(2)</b>   |                   |                  |                  |

## Legend:

| =ogona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- **2:** This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

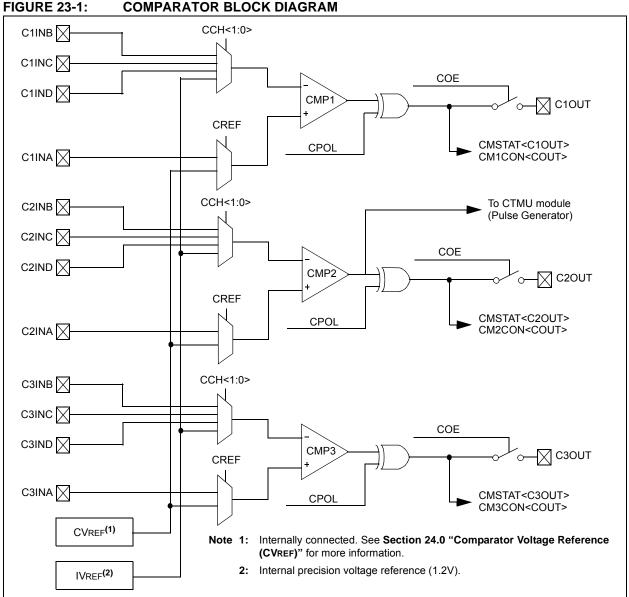

#### 23.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains three comparators that can be configured in a variety of ways.

Following are some of the key features of this module:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 23-1.

| AC CHARACTERISTICS   |               |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |             |      |                            |                                            |  |

|----------------------|---------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|----------------------------|--------------------------------------------|--|

| Param.<br>No. Symbol |               | Charact                             | Characteristics                                                                                                                                                                                                                                                                     |             | Max. | Units                      | Conditions                                 |  |

| IS10                 | TLO:SCL       | Clock Low Time                      | 100 kHz mode                                                                                                                                                                                                                                                                        | 4.7         | —    | μS                         | PBCLK must operate at a minimum of 800 kHz |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 1.3         | —    | μS                         | PBCLK must operate at a minimum of 3.2 MHz |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 0.5         | —    | μS                         | _                                          |  |

| IS11                 | THI:SCL       | Clock High Time                     | 100 kHz mode                                                                                                                                                                                                                                                                        | 4.0         | _    | μS                         | PBCLK must operate at a minimum of 800 kHz |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 0.6         | _    | μS                         | PBCLK must operate at a minimum of 3.2 MHz |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 0.5         | —    | μS                         |                                            |  |

| IS20                 | TF:SCL        | SDAx and SCLx<br>Fall Time          | 100 kHz mode                                                                                                                                                                                                                                                                        | —           | 300  | ns                         | CB is specified to be from                 |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 20 + 0.1 Св | 300  | ns                         | 10 to 400 pF                               |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | _           | 100  | ns                         |                                            |  |

| IS21 TR:SCL          | SDAx and SCLx | 100 kHz mode                        |                                                                                                                                                                                                                                                                                     | 1000        | ns   | CB is specified to be from |                                            |  |

|                      |               | Rise Time                           | 400 kHz mode                                                                                                                                                                                                                                                                        | 20 + 0.1 Св | 300  | ns                         | 10 to 400 pF                               |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | —           | 300  | ns                         |                                            |  |

| IS25                 | S25 TSU:DAT   | Data Input<br>Setup Time            | 100 kHz mode                                                                                                                                                                                                                                                                        | 250         |      | ns                         | _                                          |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 100         |      | ns                         |                                            |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 100         | —    | ns                         |                                            |  |

| IS26                 | THD:DAT       | Data Input                          | 100 kHz mode                                                                                                                                                                                                                                                                        | 0           |      | ns                         | —                                          |  |

|                      |               | Hold Time                           | 400 kHz mode                                                                                                                                                                                                                                                                        | 0           | 0.9  | μs                         |                                            |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 0           | 0.3  | μS                         |                                            |  |

| IS30                 | TSU:STA       | STA Start Condition<br>Setup Time   | 100 kHz mode                                                                                                                                                                                                                                                                        | 4700        |      | ns                         | Only relevant for Repeated                 |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 600         |      | ns                         | Start condition                            |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 250         | —    | ns                         |                                            |  |

| IS31 Thd:sta         | THD:STA       | STA Start Condition<br>Hold Time    | 100 kHz mode                                                                                                                                                                                                                                                                        | 4000        |      | ns                         | After this period, the first               |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 600         | —    | ns                         | clock pulse is generated                   |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 250         | —    | ns                         |                                            |  |

| IS33                 | Tsu:sto       | SU:STO Stop Condition<br>Setup Time | 100 kHz mode                                                                                                                                                                                                                                                                        | 4000        |      | ns                         |                                            |  |

|                      |               |                                     | 400 kHz mode                                                                                                                                                                                                                                                                        | 600         |      | ns                         | ]                                          |  |

|                      |               |                                     | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                              | 600         |      | ns                         |                                            |  |

## TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

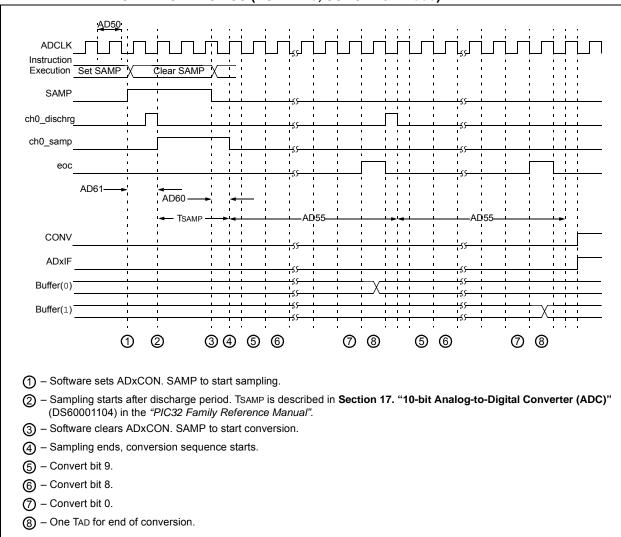

## FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

## TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS  |        |                                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                      |   |                                  |                                  |  |

|---------------------|--------|-------------------------------------------------------|------------------------------------------------------|----------------------|---|----------------------------------|----------------------------------|--|

| Param<br>No.        | Symbol | Characteristic                                        | Min.                                                 | Min. Typ. Max. Units |   | Conditions                       |                                  |  |

| CTMU CURRENT SOURCE |        |                                                       |                                                      |                      |   |                                  |                                  |  |

| CTMUI1              | Ιουτ1  | Base Range <sup>(1)</sup>                             | _                                                    | 0.55                 | _ | μA                               | CTMUCON<9:8> = 01                |  |

| CTMUI2              | Ιουτ2  | 10x Range <sup>(1)</sup>                              | _                                                    | 5.5                  | _ | μA                               | CTMUCON<9:8> = 10                |  |

| CTMUI3              | Ιουτ3  | 100x Range <sup>(1)</sup>                             | _                                                    | 55                   |   | μA                               | CTMUCON<9:8> = 11                |  |

| CTMUI4              | IOUT4  | 1000x Range <sup>(1)</sup>                            | _                                                    | 550                  |   | μA                               | CTMUCON<9:8> = 00                |  |

|                     |        | Temperature Diode Forward<br>Voltage <sup>(1,2)</sup> | —                                                    | 0.598                | _ | V                                | TA = +25°C,<br>CTMUCON<9:8> = 01 |  |

|                     | _      |                                                       | 0.658                                                | _                    | V | TA = +25°C,<br>CTMUCON<9:8> = 10 |                                  |  |

|                     |        |                                                       | —                                                    | 0.721                |   | V                                | TA = +25°C,<br>CTMUCON<9:8> = 11 |  |

| CTMUFV2             | VFVR   | Temperature Diode Rate of                             | —                                                    | -1.92                |   | mV/ºC                            | CTMUCON<9:8> = 01                |  |

|                     |        | Change <sup>(1,2)</sup>                               | _                                                    | -1.74                |   | mV/ºC                            | CTMUCON<9:8> = 10                |  |

|                     |        |                                                       | _                                                    | -1.56                |   | mV/ºC                            | CTMUCON<9:8> = 11                |  |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

**2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## 33.1 Package Marking Information (Continued)

## 44-Lead VTLA

## 44-Lead QFN

## 44-Lead TQFP

Example

## Example

## Example

## Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3) |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        |                                                                                                                                                                                          | can be found on the outer packaging for this package.                                                                                                                                                                                                                                                               |  |  |

| Note:  | If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                     |  |  |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

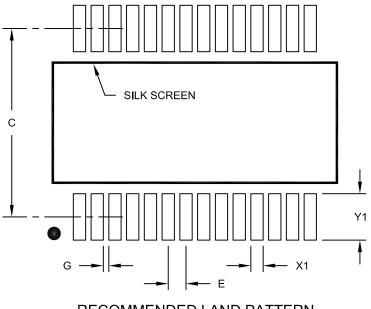

## 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |          |      |      |  |

|--------------------------|------------------|----------|------|------|--|

| Dimension                | Dimension Limits |          | NOM  | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1               |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1               |          |      | 1.75 |  |

| Distance Between Pads    | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

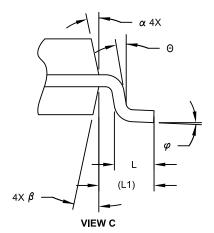

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |             |           |      |  |

|--------------------------|-------------|-------------|-----------|------|--|

| Dimension                | Limits      | MIN         | NOM       | MAX  |  |

| Number of Pins           | N           | 28          |           |      |  |

| Pitch                    | е           |             | 1.27 BSC  |      |  |

| Overall Height           | A           | -           | -         | 2.65 |  |

| Molded Package Thickness | A2          | 2.05        | -         | -    |  |

| Standoff §               | A1          | 0.10        | -         | 0.30 |  |

| Overall Width            | E           |             | 10.30 BSC |      |  |

| Molded Package Width     | E1          | 7.50 BSC    |           |      |  |

| Overall Length           | D           | 17.90 BSC   |           |      |  |

| Chamfer (Optional)       | h           | 0.25 - 0.75 |           |      |  |

| Foot Length              | L           | 0.40        | -         | 1.27 |  |

| Footprint                | L1          | 1.40 REF    |           |      |  |

| Lead Angle               | Θ           | 0°          | -         | -    |  |

| Foot Angle               | $\varphi$   | 0°          | -         | 8°   |  |

| Lead Thickness           | С           | 0.18        | -         | 0.33 |  |

| Lead Width               | b           | 0.31        | -         | 0.51 |  |

| Mold Draft Angle Top     | α           | 5° – 15     |           |      |  |

| Mold Draft Angle Bottom  | β           | 5°          | -         | 15°  |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2