#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256b-v-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 8: **PIN NAMES FOR 36-PIN USB DEVICES**

# 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016C

|       | PIC32MX220F032C<br>PIC32MX230F064C<br>PIC32MX250F128C |       |                                                  |

|-------|-------------------------------------------------------|-------|--------------------------------------------------|

|       |                                                       |       | 36                                               |

|       |                                                       |       | 1                                                |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name                                    |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2             | 19    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3               | 20    | RPC9/CTED7/RC9                                   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0                    | 21    | Vss                                              |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1                    | 22    | VCAP                                             |

| 5     | VDD                                                   | 23    | VDD                                              |

| 6     | Vss                                                   | 24    | PGED2/RPB10/D+/CTED11/RB10                       |

| 7     | OSC1/CLKI/RPA2/RA2                                    | 25    | PGEC2/RPB11/D-/RB11                              |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3                               | 26    | VUSB3V3                                          |

| 9     | SOSCI/RPB4/RB4                                        | 27    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                        | 28    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 11    | AN12/RPC3/RC3                                         | 29    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 12    | Vss                                                   | 30    | AVss                                             |

| 13    | Vdd                                                   | 31    | AVdd                                             |

| 14    | VDD                                                   | 32    | MCLR                                             |

| 15    | TMS/RPB5/USBID/RB5                                    | 33    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 16    | VBUS                                                  | 34    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7                          | 35    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 18    | TCK/RP88/SCL1/CTED10/PM04/RB8                         | 36    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin 1: Select" for restrictions.

Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information. 2:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 3:

4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant. NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 10.0         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                    |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |

| 7:0          | —                 | —                 | _                 | —                 | _                 | —                 | —                | SWRST <sup>(1)</sup> |  |

# REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by hardware |                                    |                    |  |  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable Software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit is written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

- bit 18-16 **PLLMULT<2:0>:** Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 = Clock is multiplied by 17

- 001 = Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (OSCCON<26:24>)

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x):

Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = The USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 =The USB PLL module is out of lock or USB PLL module start-up timer is in progress or the USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = The PLL module is in lock or PLL module start-up timer is satisfied

- 0 = The PLL module is out of lock, the PLL start-up timer is running, or the PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = The device will enter Sleep mode when a WAIT instruction is executed

- 0 = The device will enter Idle mode when a WAIT instruction is executed

- **Note 1:** This bit is only available on PIC32MX2XX devices.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                       | —                 | —                 |                   | _                | —                |  |

| 23:16        | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | _                       | —                 | —                 | _                 | —                | —                |  |

| 45.0         | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | —                 | _                       | —                 | _                 | _                 | _                | —                |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | —                 | _                 | TUN<5:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|-------------------|-------------------|-------------------|--------------------------------------------|-------------------|------------------|------------------|--|--|--|

|              | U-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                                      | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                           |                   |                   | R                 | )<2017/2017/2017/2017/2017/2017/2017/2017/ | 1,3)              |                  |                  |  |  |  |

|              | R/W-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-0                                      | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                   |                   |                   |                                            |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                       | U-0               | R/W-0             | R/W-0             | R/W-0                                      | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |

| 15:8         | ON                          | _                 | SIDL              | OE                | RSLP <sup>(2)</sup>                        | _                 | DIVSWEN          | ACTIVE           |  |  |  |

|              | U-0                         | U-0               | U-0               | U-0               | R/W-0                                      | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                             |                   |                   |                   |                                            | ROSEL             | .<3:0>(1)        |                  |  |  |  |

### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | CHDSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

NOTES:

#### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 51.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23.10        | -                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         |                   | _                 | _                 |                   | _                 | _                 | _                     | —                                                |

|              | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       |                                               |

- 1 = STALL interrupt is enabled

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 = ATTACH interrupt is enabled 0 = ATTACH interrupt is disabled

- bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

#### DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

NOTES:

### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 16.1 Output Compare Control Registers

# TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |                   |       |             |       |       |       |       |      | В     | its     |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|-------------------|-------|-------------|-------|-------|-------|-------|------|-------|---------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15 | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16             | —     | —           | —     | —     | —     | —     | —    | _     | —       | —    | —    | —     | —      | _    | —        | _    | 0000         |

| 0000                        | 001001                          | 15:0              | ON    | —           | SIDL  | —     | —     | —     |      | —     | —       | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0     |       | OC1R<31:0>  |       |       |       |       |      |       |         |      |      | xxxx  |        |      |          |      |              |

| 3020                        | OC1RS                           | 31:16<br>15:0     |       | OC1RS<31:0> |       |       |       |       |      |       |         |      |      | xxxx  |        |      |          |      |              |

| 0000                        | 00000                           | 31:16             | —     | _           | _     | _     | _     | _     |      | _     | —       | —    | _    | —     | —      | —    | —        | —    | 0000         |

| 3200                        | OC2CON                          | 15:0              | ON    | _           | SIDL  | _     | _     | _     | _    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3210                        | OC2R                            | 31:16             |       |             |       |       |       |       |      | OC2R  | ~21.0>  |      |      |       |        |      |          |      | xxxx         |

| 3210                        | UCZR                            | 15:0              |       |             |       |       |       |       |      | UCZR  | <31.0>  |      |      |       |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 31:16             |       |             |       |       |       |       |      | OC2RS | 2-31-05 |      |      |       |        |      |          |      | XXXX         |

| 3220                        | 00283                           | 15:0              |       |             |       |       |       |       |      | UCZRO | 5<31.02 |      |      |       |        |      |          |      | XXXX         |

| 3400                        | OC3CON                          | 31:16             | _     | _           | _     | _     | _     | _     | _    | _     | _       | _    | _    | _     | —      |      | —        |      | 0000         |

| 3400                        | 003001                          | 15:0              | ON    | _           | SIDL  | _     | _     | _     | _    | _     | -       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0     |       |             |       |       |       |       |      | OC3R  | <31:0>  |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16             |       |             |       |       |       |       |      | OC3R8 | 221.05  |      |      |       |        |      |          |      | XXXX         |

| 3420                        | 00383                           | 15:0              |       |             |       |       |       |       |      | UCSRC | 5-51.0- |      |      |       |        |      |          |      | XXXX         |

| 3600                        | OC4CON                          | 31:16             | —     | _           | _     | _     | _     | _     | _    | _     | —       | —    | _    | —     | —      |      | —        | _    | 0000         |

| 3000                        | 004001                          | 15:0              | ON    | _           | SIDL  | _     | _     | _     | _    | _     | -       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16             |       |             |       |       |       |       |      | OC4R  | <31.0>  |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0041                            | 15:0              |       |             |       |       |       |       |      | 0041  | ST.02   |      |      |       |        |      |          |      | xxxx         |

| 3620                        | OC4RS                           | 31:16             |       |             |       |       |       |       |      | OC4RS | 231.05  |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00410                           | 15:0              |       |             |       |       |       |       |      | 00400 | 5-51.02 |      |      |       |        |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16             | -     | _           | —     | _     | _     | _     | _    | _     | -       | _    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | 000001                          | 15:0              | ON    | —           | SIDL  | —     | —     | —     | —    | —     | —       | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16             |       |             |       |       |       |       |      | OC5R  | <31.0>  |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0000                            | 15:0              |       |             |       |       |       |       |      | OUJK  | -01.02  |      |      |       |        |      |          |      | xxxx         |

| 3820                        | OC5RS                           | 31:16             |       |             |       |       |       |       |      | OC5RS | <31·0>  |      |      |       |        |      |          |      | XXXX         |

| 3020                        | 00010                           | 15 <sup>.</sup> 0 |       |             |       |       |       |       |      | 00000 | -01.02  |      |      |       |        |      |          |      | xxxx         |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

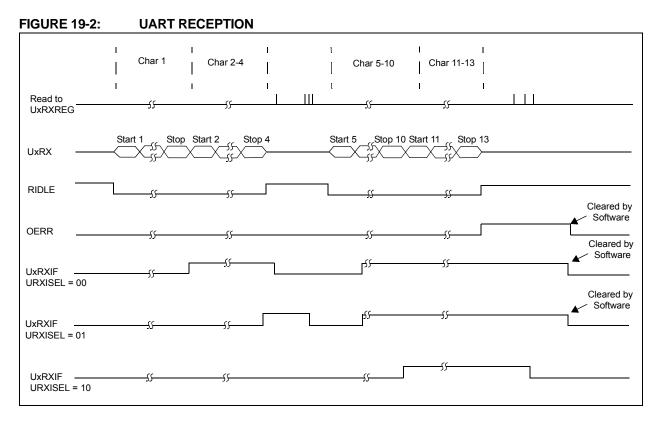

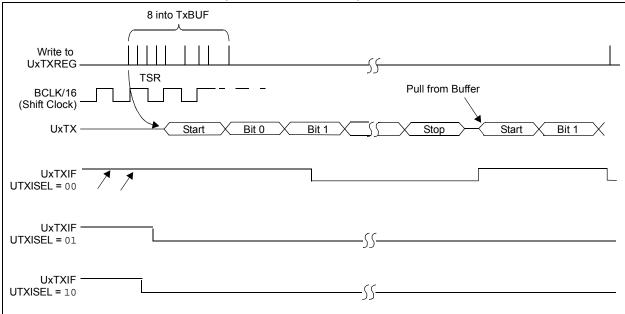

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | —                 | —                 | HR10              | <1:0>             |                   | HR01<3:0>         |                  |                  |  |  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          |                   | —                 | _                 |                   | _                 | -                 | —                | —                |  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

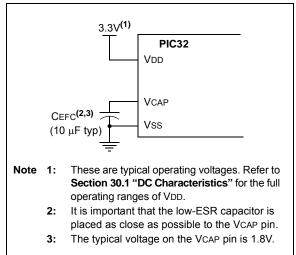

# 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

# 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

# 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

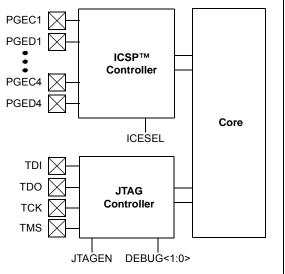

# 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

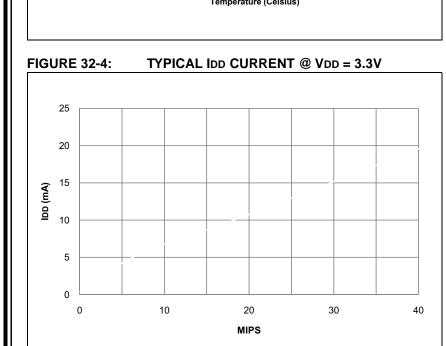

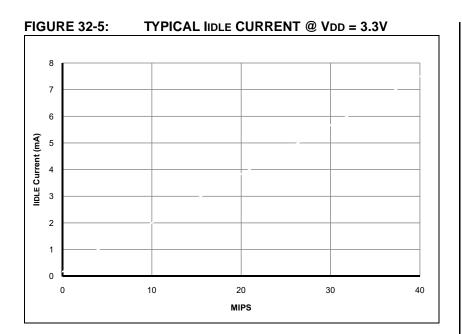

### TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACT                                                     | ERISTICS |       | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |  |  |  |

|----------------------------------------------------------------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parameter Typical <sup>(2)</sup> Max.                          |          | Units | Conditions                                                                                                                                          |  |  |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |          |       |                                                                                                                                                     |  |  |  |  |  |

| MDC34a                                                         | 8        | 13    | mA 50 MHz                                                                                                                                           |  |  |  |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- + CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| DC CHAR                           | ACTERIST               | ICS     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |                                                 |  |  |  |  |

|-----------------------------------|------------------------|---------|------------------------------------------------------|------------|-------------------------------------------------|--|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max.    | Units                                                | Conditions |                                                 |  |  |  |  |

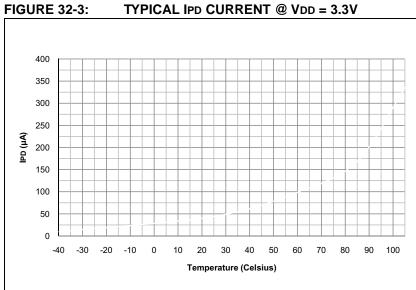

| Power-Down Current (IPD) (Note 1) |                        |         |                                                      |            |                                                 |  |  |  |  |

| MDC40k                            | 10                     | 25      | μA                                                   | -40°C      | Base Power-Down Current                         |  |  |  |  |

| MDC40n                            | 250                    | 500     | μA                                                   | +85°C      | Base Power-Down Current                         |  |  |  |  |

| Module D                          | ifferential (          | Current |                                                      |            |                                                 |  |  |  |  |

| MDC41e                            | 10                     | 55      | μA                                                   | 3.6V       | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |  |

| MDC42e                            | 23                     | 55      | μA                                                   | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |  |

| MDC43d                            | 1100                   | 1300    | μA                                                   | 3.6V       | ADC: Aladc (Notes 3,4)                          |  |  |  |  |

### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

• Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

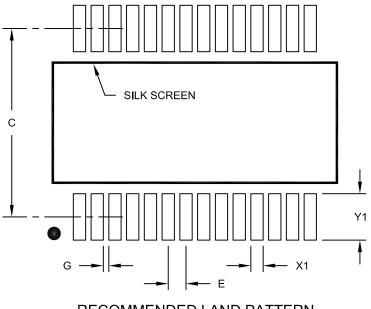

## 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |      |          |      |

|--------------------------|------------------|------|----------|------|

| Dimension                | Dimension Limits |      |          |      |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |

| Contact Pad Width (X28)  | X1               |      |          | 0.45 |

| Contact Pad Length (X28) | Y1               |      |          | 1.75 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A