#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256bt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | rals                               |                    |                     |     |     | <u> </u>                                 |      | ls)                          |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|-----|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l²C | PMP | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F064B | 28   | 64+3                               | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F064C | 36   | 64+3                               | 16               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Υ    | VTLA                            |

| PIC32MX130F064D | 44   | 64+3                               | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX150F128B | 28   | 128+3                              | 32               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX150F128C | 36   | 128+3                              | 32               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX150F128D | 44   | 128+3                              | 32               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F256B | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F256D | 44   | 256+3                              | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX170F256B | 28   | 256+3                              | 64               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX170F256D | 44   | 256+3                              | 64               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

#### TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

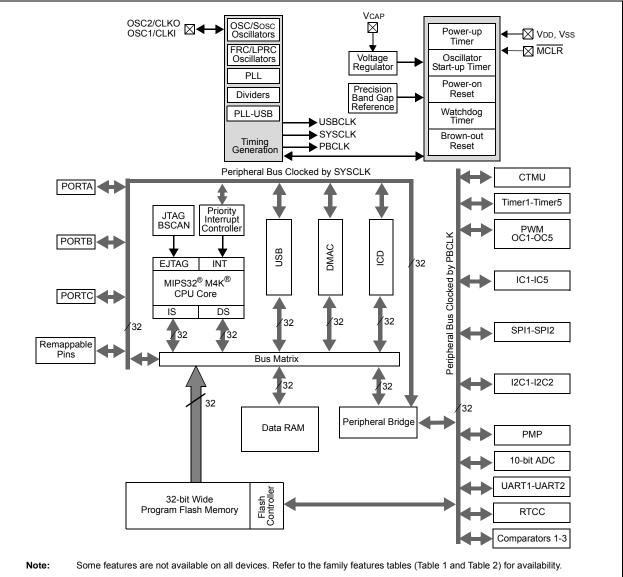

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

#### 5.1 Flash Controller Control Registers

#### TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |                  |       |       |        |         |       |      | Bit     | s       |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|------------------|-------|-------|--------|---------|-------|------|---------|---------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15            | 30/14 | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>  | 31:16     | —                |       |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

| F400                        | INVIVICOIN**           | 15:0      | WR               | WREN  | WRERR | LVDERR | LVDSTAT | _     |      | —       |         | _    | —    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |                  |       |       |        |         |       |      | NVMKEY  | <31·0>  |      |      |      |      |      |        |      | 0000       |

| 1410                        |                        | 15:0      |                  |       |       |        |         |       |      |         | ~51.02  |      |      |      |      |      |        |      | 0000       |

| F420                        | NVMADDR <sup>(1)</sup> | 31:16     |                  |       |       |        |         |       |      | NVMADD  | ₽<31·0> |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |                  |       |       |        |         |       |      | NVINADD | N~51.02 |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |                  |       |       |        |         |       |      | NVMDAT  | N~31·0> |      |      |      |      |      |        |      | 0000       |

| 1 430                       |                        | 15:0      |                  |       |       |        |         |       |      |         |         |      |      | 0000 |      |      |        |      |            |

| E440                        | NVMSRCADDR             | 31:16     |                  |       |       |        |         |       | N    |         |         |      |      |      |      |      |        |      | 0000       |

| 1 440                       | NVINGRCADDR            | 15:0      | NVMSRCADDR<31:0> |       |       |        |         |       |      |         |         |      |      |      |      |      |        |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 23:10        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | _                 | —                 |                      | —                     |                        | P<3:0>            |                  |                  |  |  |  |  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |  |  |  |  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS01<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-2 | IP00<2:0>: Interrupt Priority bits                                                                                    |

|         | 111 = Interrupt priority is 7                                                                                         |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | 010 = Interrupt priority is 2                                                                                         |

|         | 001 = Interrupt priority is 1                                                                                         |

|         | 000 = Interrupt is disabled                                                                                           |

| bit 1-0 | IS00<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

#### 8.1 Oscillator Control Regiters

| TAB                                                  | TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |           |               |       |                             |       |       |                                   |        |         |                      |          |               |      |                       |        |       |                     |           |

|------------------------------------------------------|--------------------------------------------|-----------|---------------|-------|-----------------------------|-------|-------|-----------------------------------|--------|---------|----------------------|----------|---------------|------|-----------------------|--------|-------|---------------------|-----------|

| ess                                                  |                                            | 0         |               |       |                             |       |       |                                   |        |         | Bits                 |          |               |      |                       |        |       |                     | ú         |

| Virtual Address<br>(BF80_#)                          | Register<br>Name <sup>(1)</sup>            | Bit Range | 31/15         | 30/14 | 29/13                       | 28/12 | 27/11 | 26/10                             | 25/9   | 24/8    | 23/7                 | 22/6     | 21/5          | 20/4 | 19/3                  | 18/2   | 17/1  | 16/0                | All Reset |

| E000                                                 | F000 OSCCON                                | 31:16     | —             | _     | PLLODIV<2:0><br>COSC<2:0> — |       |       | FRCDIV<2:0> —<br>NOSC<2:0> CLKLOO |        | —       | SOSCRDY              | PBDIVRDY | DY PBDIV<1:0> |      | PLLMULT<2:0>          |        | >     | x1xx <sup>(2)</sup> |           |

| FUUU                                                 | 030001                                     | 15:0      | —             |       |                             |       |       |                                   |        | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK    | SLPEN         | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx(2)             |           |

| F010                                                 | OSCTUN                                     | 31:16     | _             | _     |                             | _     | _     |                                   |        | _       | _                    | _        | _             | _    |                       | _      | —     | _                   | 0000      |

| 1010                                                 | 030101                                     | 15:0      | _             | _     |                             | _     | _     |                                   |        | _       | _                    | _        |               |      | TUN                   | l<5:0> |       |                     | 0000      |

| 5000                                                 |                                            | 31:16     | _             |       |                             |       |       |                                   |        |         | RODIV<1              | 4:0>     |               |      |                       |        |       |                     | 0000      |

| F020 REFOCON 15:0 ON - SIDL OE RSLP - DIVSWEN ACTIVE |                                            |           |               |       |                             |       |       | ROSE                              | _<3:0> |         | 0000                 |          |               |      |                       |        |       |                     |           |

| F000                                                 | DEEOTDIM                                   | 31:16     | 6 ROTRIM<8:0> |       |                             |       |       |                                   |        |         | _                    | 0000     |               |      |                       |        |       |                     |           |

| F030                                                 | REFOTRIM                                   | 15:0      | _             | _     |                             | _     | _     |                                   |        | -       | _                    | _        | _             | _    |                       | _      | —     | _                   | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | _                | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        |                   | _                 |                   | _                 | _                 |                   | _                |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CHCSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

## Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

1111111111111111 = 65,535 bytes transferred on an event

#### REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   | CHCPTR<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | —                 | —                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

#### REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

#### bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

#### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit<br>30/22/14/6 29/21/13/5 2 |        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|------------------------------------|--------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0                                | U-0    | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                   | —                                  |        |                   |                   | _                 | _                | —                |  |  |  |  |

| 23:16        | U-0               | U-0                                | U-0    | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | _                 | —                                  |        |                   |                   | _                 | _                | —                |  |  |  |  |

| 15:8         | U-0               | U-0                                | U-0    | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | _                 | —                                  |        |                   |                   | _                 | _                | —                |  |  |  |  |

| 7:0          | R-x               | R-x                                | R-x    | R-x               | R-x               | R-x               | U-0              | U-0              |  |  |  |  |

| 7.0          |                   | ENDP                               | T<3:0> |                   | DIR               | PPBI              |                  |                  |  |  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| Bit<br>Range | Bit<br>31/23/15/7 |       |       |        |          | Bit Bit<br>3/5 28/20/12/4 27/19/11/3 |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------|-------|--------|----------|--------------------------------------|-------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | U-0               | U-0   | U-0   | U-0    | U-0      | U-0                                  | U-0   | U-0               |                  |                  |  |  |  |  |

| 31:24        | _                 | —     | -     | —      | -        | —                                    | —     | —                 |                  |                  |  |  |  |  |

| 22:16        | U-0               | U-0   | U-0   | U-0    | U-0      | U-0                                  | U-0   | U-0               |                  |                  |  |  |  |  |

| 23:16        | -                 | _     |       | —      | -        |                                      |       | —                 |                  |                  |  |  |  |  |

| 15:8         | U-0               | U-0   | U-0   | U-0    | U-0      | U-0                                  | U-0   | U-0               |                  |                  |  |  |  |  |

| 15.0         | _                 | —     | _     | —      | -        | —                                    | —     | —                 |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0                                | R/W-0 | R/W-0             |                  |                  |  |  |  |  |

| 7:0          |                   |       |       | BDTPTR | H<23:16> |                                      |       |                   |                  |                  |  |  |  |  |

#### REGISTER 10-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

| REGIOT       |                   |       |       |        |          |       |       |                   |                  |                  |  |  |  |

|--------------|-------------------|-------|-------|--------|----------|-------|-------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 |       |       |        |          |       |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | U-0               | U-0   | U-0   | U-0    | U-0      | U-0   | U-0   | U-0               |                  |                  |  |  |  |

| 31.24        | —                 | —     |       |        | _        | _     | —     | —                 |                  |                  |  |  |  |

| 23:16        | U-0               | U-0   | U-0   | U-0    | U-0      | U-0   | U-0   | U-0               |                  |                  |  |  |  |

| 23.10        | _                 |       |       |        |          |       | _     | _                 |                  |                  |  |  |  |

| 15:8         | U-0               | U-0   | U-0   | U-0    | U-0      | U-0   | U-0   | U-0               |                  |                  |  |  |  |

| 15.0         | —                 | _     |       |        |          | -     | —     | —                 |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0             |                  |                  |  |  |  |

| 7:0          |                   |       |       | BDTPTR | U<31:24> |       |       |                   |                  |                  |  |  |  |

#### REGISTER 10-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRU<31:24>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |  |  |  |  |

|--------------|----------|-------------|---------------------------------------------|--|--|--|--|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |  |  |  |  |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |  |  |  |  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |  |  |  |  |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |  |  |  |  |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |  |  |  |  |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |  |  |  |  |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |  |  |  |  |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |  |  |  |  |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |  |  |  |  |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |  |  |  |  |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |  |  |  |  |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |  |  |  |  |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |  |  |  |  |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |  |  |  |  |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |  |  |  |  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |  |  |  |  |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |  |  |  |  |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |  |  |  |  |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |  |  |  |  |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |  |  |  |  |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |  |  |  |  |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |  |  |  |  |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |  |  |  |  |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |  |  |  |  |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |  |  |  |  |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |  |  |  |  |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |  |  |  |  |

### 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |  |  |  |  |  |  |  |

|-------|------------------------------------------------------|--|--|--|--|--|--|--|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |  |  |  |  |  |  |  |

|       | Family of devices. It is not intended to be          |  |  |  |  |  |  |  |

|       | a comprehensive reference source. To                 |  |  |  |  |  |  |  |

|       | complement the information in this data              |  |  |  |  |  |  |  |

|       | sheet, refer to Section 24. "Inter-                  |  |  |  |  |  |  |  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |  |  |  |  |  |  |  |

|       | which is available from the Documentation            |  |  |  |  |  |  |  |

|       | > Reference Manual section of the Micro-             |  |  |  |  |  |  |  |

|       | chip PIC32 web site                                  |  |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                           |  |  |  |  |  |  |  |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

NOTES:

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |        | Bit Bit 29/21/13/5 28/20/12 |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------------|--------|-----------------------------|-------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                              | U-0    | U-0                         | U-0   | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                                | —      |                             | _     | _                 | _                 | —                | _                |  |

| 00.40        | U-0                              | U-0    | U-0                         | U-0   | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                                | —      | _                           | _     | _                 |                   | —                | _                |  |

| 45.0         | R/W-0                            | R/W-0  | R/W-0                       | U-0   | U-0               | U-0               | U-0              | R-0              |  |

| 15:8         | ON <sup>(1)</sup>                | COE    | CPOL <sup>(2)</sup>         | _     | —                 | —                 | —                | COUT             |  |

| 7.0          | R/W-1                            | R/W-1  | U-0                         | R/W-0 | U-0               | U-0               | R/W-1            | R/W-1            |  |

| 7:0          | EVPOL                            | _<1:0> |                             | CREF  | _                 | _                 | CCH              | <1:0>            |  |

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

#### TABLE 26-2: PERIPHERAL MODULE DISABLE REGISTER MAP

| ess                         |                                 |           |       | Bits  |       |       |       |       |        |        |      |      | 6    |       |       |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|-------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets |

| 5040                        | PMD1                            | 31:16     | —     | —     | _     | —     | _     | _     | _      | —      | —    | —    | —    | —     | —     | —      | —      | —      | 0000       |

| F240                        | FIVIDI                          | 15:0      | -     |       |       | CVRMD | Ι     |       |        | CTMUMD | —    | -    |      | -     | —     |        | —      | AD1MD  | 0000       |

| 5250                        | PMD2                            | 31:16     | —     | —     |       | —     | _     | _     |        | —      | —    | —    | —    | —     | —     | —      | —      | —      | 0000       |

| F250                        | FIVIDZ                          | 15:0      | -     |       |       | —     | Ι     |       |        | —      | —    | -    |      | -     | —     | CMP3MD | CMP2MD | CMP1MD | 0000       |

| F260                        | PMD3                            | 31:16     | _     |       |       | _     | -     |       |        | _      | _    |      | _    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       |        | _      | _    |      | _    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000       |

| F270                        | PMD4                            | 31:16     | _     |       |       | _     | -     |       |        | _      | _    |      | _    | -     | _     | _      | —      | _      | 0000       |

| F270                        | F IVID4                         | 15:0      | _     |       |       | _     | -     |       |        | _      | _    |      | _    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000       |

| F280                        | PMD5                            | 31:16     | _     |       |       | _     | -     |       |        | USB1MD | _    |      | _    | -     | _     | _      | I2C1MD | I2C1MD | 0000       |

| F200                        | FIVIDS                          | 15:0      | _     |       |       | _     | -     |       | SPI2MD | SPI1MD | _    |      | _    | -     | _     | _      | U2MD   | U1MD   | 0000       |

| F200                        | PMD6                            | 31:16     | _     | —     |       | —     | _     | _     |        | _      | —    | _    | —    | _     | —     | —      | —      | PMPMD  | 0000       |

| F290                        | I WD0                           | 15:0      | —     | _     | _     | —     | _     | _     | -      | —      | —    | _    | _    | _     | —     | _      | REFOMD | RTCCMD | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

#### 27.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 27-6) provides device and revision information.

#### **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 31.0** "**50 MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

#### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

3: See the "Pin Diagrams" section for the 5V tolerant pins.

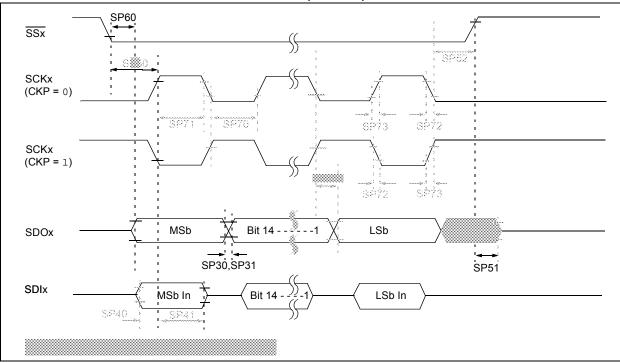

#### FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |        |                        |      |       |                    |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                                                                                                                                                                | Min.   | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)                                                                                                                                                                                  | Tsck/2 | _                      | _    | ns    | —                  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)                                                                                                                                                                                 | Tsck/2 | —                      | _    | ns    | —                  |

| SP72               | TscF                  | SCKx Input Fall Time                                                                                                                                                                                          | _      | 5                      | 10   | ns    | —                  |

| SP73               | TscR                  | SCKx Input Rise Time                                                                                                                                                                                          | —      | 5                      | 10   | ns    | —                  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)                                                                                                                                                                           | —      | —                      | _    | ns    | See parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)                                                                                                                                                                           | —      | —                      | _    | ns    | See parameter DO31 |

| SP35               | TscH2doV,             | SDOx Data Output Valid after                                                                                                                                                                                  | _      | —                      | 20   | ns    | VDD > 2.7V         |

|                    | TscL2doV              | SCL2DOV SCKx Edge                                                                                                                                                                                             | _      | —                      | 30   | ns    | VDD < 2.7V         |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                    | 10     | —                      | _    | ns    | —                  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                     | 10     | —                      |      | ns    | —                  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input                                                                                                                                     | 175    | —                      |      | ns    | _                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

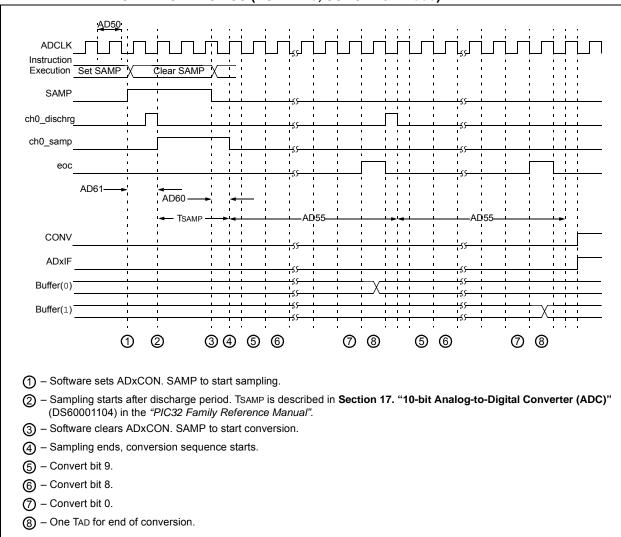

#### FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

| U1OTGSTAT (USB OTG Status)       | 110 |

|----------------------------------|-----|

| U1PWRC (USB Power Control)       | 112 |

| U1SOF (USB SOF Threshold)        | 123 |

| U1STAT (USB Status)              | 118 |

| U1TOK (USB Token)                | 122 |

| UxMODE (UARTx Mode)              | 183 |

| UxSTA (UARTx Status and Control) | 185 |

| WDTCON (Watchdog Timer Control)  | 155 |

| Resets                           |     |

| Revision History                 | 329 |

| RTCALRM (RTC ALARM Control)      | 203 |

### S

| Serial Peripheral Interface (SPI) | 165 |

|-----------------------------------|-----|

| Software Simulator (MPLAB SIM)    |     |

| Special Features                  | 239 |

#### Т

| Timer1 Module<br>Timer2/3, Timer4/5 Modules<br>Timing Diagrams |     |

|----------------------------------------------------------------|-----|

| 10-Bit Analog-to-Digital Conversion                            |     |

| (ASAM = 0, SSRC<2:0> = 000)                                    | 293 |

| 10-Bit Analog-to-Digital Conversion (ASAM = 1,                 |     |

| SSRC<2:0> = 111, SAMC<4:0> = 00001)                            | 294 |

| EJTAG                                                          | 300 |

| External Clock                                                 | 269 |

| I/O Characteristics                                            | 272 |

| I2Cx Bus Data (Master Mode)                                    | 283 |

| I2Cx Bus Data (Slave Mode)                                     | 286 |

| I2Cx Bus Start/Stop Bits (Master Mode)                         | 283 |

| I2Cx Bus Start/Stop Bits (Slave Mode)                          | 286 |

| Input Capture (CAPx)                                           | 276 |

| OCx/PWM                                                        |     |

| Output Compare (OCx)                                           | 277 |

| Parallel Master Port Read                                      | 296 |

| Parallel Master Port Write                                     | 297 |

|                                                                |     |

| Parallel Slave Port                      | . 295 |

|------------------------------------------|-------|

| SPIx Master Mode (CKE = 0)               | . 278 |

| SPIx Master Mode (CKE = 1)               | . 279 |

| SPIx Slave Mode (CKE = 0)                | . 280 |

| SPIx Slave Mode (CKE = 1)                | . 281 |

| Timer1, 2, 3, 4, 5 External Clock        | . 275 |

| UART Reception                           | . 187 |

| UART Transmission (8-bit or 9-bit Data)  | . 187 |

| Timing Requirements                      |       |

| CLKO and I/O                             | . 272 |

| Timing Specifications                    |       |

| I2Cx Bus Data Requirements (Master Mode) |       |

| I2Cx Bus Data Requirements (Slave Mode)  |       |

| Input Capture Requirements               |       |

| Output Compare Requirements              |       |

| Simple OCx/PWM Mode Requirements         |       |

| SPIx Master Mode (CKE = 0) Requirements  |       |

| SPIx Master Mode (CKE = 1) Requirements  |       |

| SPIx Slave Mode (CKE = 1) Requirements   |       |

| SPIx Slave Mode Requirements (CKE = 0)   | . 280 |

| Timing Specifications (50 MHz)           |       |

| SPIx Master Mode (CKE = 0) Requirements  |       |

| SPIx Master Mode (CKE = 1) Requirements  |       |

| SPIx Slave Mode (CKE = 1) Requirements   |       |

| SPIx Slave Mode Requirements (CKE = 0)   | . 305 |

| U                                        |       |

|                                          | 101   |

| UART                |     |

|---------------------|-----|

| USB On-The-Go (OTG) | 103 |

| V                   |     |

| VCAP nin            | 250 |

| VCAP pin                    |     |

|-----------------------------|-----|

| Voltage Regulator (On-Chip) | 250 |

|                             |     |

| W                           |     |

| M/M/M/ Addross              | 2/1 |

| WWW Address          | . 341 |

|----------------------|-------|

| WWW, On-Line Support | 16    |