Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256d-50i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams**

### TABLE 3: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

28-PIN SOIC, SPDIP, SSOP (TOP VIEW)(1,2,3)

1 28 1 28 1 28 SSOP SOIC SPDIP

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

| Pin # | Full Pin Name                         |

|-------|---------------------------------------|

| 1     | MCLR                                  |

| 2     | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0 |

| 3     | VREF-/CVREF-/AN1/RPA1/CTED2/RA1       |

| 4     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  |

| 5     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 |

| 6     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  |

| 7     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    |

| 8     | Vss                                   |

| 9     | OSC1/CLKI/RPA2/RA2                    |

| 10    | OSC2/CLKO/RPA3/PMA0/RA3               |

| 11    | SOSCI/RPB4/RB4                        |

| 12    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        |

| 13    | VDD                                   |

| 14    | PGED3/RPR5/PMD7/RR5                   |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | PGEC3/RPB6/PMD6/RB6                            |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 19   | Vss                                            |

| 20   | VCAP                                           |

| 21   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 22   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 23   | AN12/PMD0/RB12                                 |

| 24   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 25   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 27   | AVss                                           |

| 28   | AVDD                                           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

#### TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

**36-PIN VTLA (TOP VIEW)**(1,2,3,5)

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

1

|       | T                                    |

|-------|--------------------------------------|

| Pin # | Full Pin Name                        |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   |

| 5     | VDD                                  |

| 6     | Vss                                  |

| 7     | OSC1/CLKI/RPA2/RA2                   |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              |

| 9     | SOSCI/RPB4/RB4                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       |

| 11    | RPC3/RC3                             |

| 12    | Vss                                  |

| 13    | VDD                                  |

| 14    | VDD                                  |

| 15    | PGED3/RPB5/PMD7/RB5                  |

| 16    | PGEC3/RPB6/PMD6/RB6                  |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 20   | RPC9/CTED7/RC9                                 |

| 21   | Vss                                            |

| 22   | VCAP                                           |

| 23   | VDD                                            |

| 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 26   | AN12/PMD0/RB12                                 |

| 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 30   | AVss                                           |

| 31   | AVDD                                           |

| 32   | MCLR                                           |

| 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

- 5: Shaded pins are 5V tolerant.

### TABLE 12: PIN NAMES FOR 44-PIN USB DEVICES

44-PIN TQFP (TOP VIEW)(1,2,3,5)

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

1

| Pin # | Full Pin Name                                    |

|-------|--------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         |

| 2     | RPC6/PMA1/RC6                                    |

| 3     | RPC7/PMA0/RC7                                    |

| 4     | RPC8/PMA5/RC8                                    |

| 5     | RPC9/CTED7/PMA6/RC9                              |

| 6     | Vss                                              |

| 7     | VCAP                                             |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       |

| 9     | PGEC2/RPB11/D-/RB11                              |

| 10    | VUSB3V3                                          |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 16    | AVss                                             |

| 17    | AVDD                                             |

| 18    | MCLR                                             |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| Pin # | Full Pin Name                             |

|-------|-------------------------------------------|

| 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 25    | AN6/RPC0/RC0                              |

| 26    | AN7/RPC1/RC1                              |

| 27    | AN8/RPC2/PMA2/RC2                         |

| 28    | VDD                                       |

| 29    | Vss                                       |

| 30    | OSC1/CLKI/RPA2/RA2                        |

| 31    | OSC2/CLKO/RPA3/RA3                        |

| 32    | TDO/RPA8/PMA8/RA8                         |

| 33    | SOSCI/RPB4/RB4                            |

| 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 35    | TDI/RPA9/PMA9/RA9                         |

| 36    | AN12/RPC3/RC3                             |

| 37    | RPC4/PMA4/RC4                             |

| 38    | RPC5/PMA3/RC5                             |

| 39    | Vss                                       |

| 40    | Vod                                       |

| 41    | RPB5/USBID/RB5                            |

| 42    | VBUS                                      |

| 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

#### Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

- 5: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                     | Pin Nu | mber <sup>(1)</sup> |                                 |             |                |                                                |

|----------|---------------------|--------|---------------------|---------------------------------|-------------|----------------|------------------------------------------------|

| Pin Name | Pin Name 28-pin QFN |        | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                    |

| RC0      | _                   | _      | 3                   | 25                              | I/O         | ST             | PORTC is a bidirectional I/O port              |

| RC1      | _                   | _      | 4                   | 26                              | I/O         | ST             |                                                |

| RC2      |                     | _      |                     | 27                              | I/O         | ST             |                                                |

| RC3      | _                   | _      | 11                  | 36                              | I/O         | ST             |                                                |

| RC4      | _                   | _      | _                   | 37                              | I/O         | ST             |                                                |

| RC5      | _                   | _      | _                   | 38                              | I/O         | ST             |                                                |

| RC6      | _                   | _      | _                   | 2                               | I/O         | ST             |                                                |

| RC7      | _                   | _      | _                   | 3                               | I/O         | ST             |                                                |

| RC8      | _                   | _      | _                   | 4                               | I/O         | ST             |                                                |

| RC9      | _                   | _      | 20                  | 5                               | I/O         | ST             |                                                |

| T1CK     | 9                   | 12     | 10                  | 34                              | I           | ST             | Timer1 external clock input                    |

| T2CK     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | Timer2 external clock input                    |

| T3CK     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | Timer3 external clock input                    |

| T4CK     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | Timer4 external clock input                    |

| T5CK     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | Timer5 external clock input                    |

| U1CTS    | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | UART1 clear to send                            |

| U1RTS    | PPS                 | PPS    | PPS                 | PPS                             | 0           | _              | UART1 ready to send                            |

| U1RX     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | UART1 receive                                  |

| U1TX     | PPS                 | PPS    | PPS                 | PPS                             | 0           | _              | UART1 transmit                                 |

| U2CTS    | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | UART2 clear to send                            |

| U2RTS    | PPS                 | PPS    | PPS                 | PPS                             | 0           | _              | UART2 ready to send                            |

| U2RX     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | UART2 receive                                  |

| U2TX     | PPS                 | PPS    | PPS                 | PPS                             | 0           | _              | UART2 transmit                                 |

| SCK1     | 22                  | 25     | 28                  | 14                              | I/O         | ST             | Synchronous serial clock input/output for SPI1 |

| SDI1     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | SPI1 data in                                   |

| SDO1     | PPS                 | PPS    | PPS                 | PPS                             | 0           | _              | SPI1 data out                                  |

| SS1      | PPS                 | PPS    | PPS                 | PPS                             | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O  |

| SCK2     | 23                  | 26     | 29                  | 15                              | I/O         | ST             | Synchronous serial clock input/output for SPI2 |

| SDI2     | PPS                 | PPS    | PPS                 | PPS                             | I           | ST             | SPI2 data in                                   |

| SDO2     | PPS                 | PPS    | PPS                 | PPS                             | 0           | _              | SPI2 data out                                  |

| SS2      | PPS                 | PPS    | PPS                 | PPS                             | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O  |

| SCL1     | 14                  | 17     | 18                  | 44                              | I/O         | ST             | Synchronous serial clock input/output for I2C1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer Analog = Analog input

O = Output

PPS = Peripheral Pin Select

P = Power I = Input — = N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

- 2: Pin number for PIC32MX1XX devices only.

- 3: Pin number for PIC32MX2XX devices only.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin Number <sup>(1)</sup>              |                                        |                                        |                                 |             |                |                                                       |  |  |

|----------|----------------------------------------|----------------------------------------|----------------------------------------|---------------------------------|-------------|----------------|-------------------------------------------------------|--|--|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC      | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                           |  |  |

| SDA1     | 15                                     | 18                                     | 19                                     | 1                               | I/O         | ST             | Synchronous serial data input/output for I2C1         |  |  |

| SCL2     | 4                                      | 7                                      | 2                                      | 24                              | I/O         | ST             | Synchronous serial clock input/output for I2C2        |  |  |

| SDA2     | 3                                      | 6                                      | 1                                      | 23                              | I/O         | ST             | Synchronous serial data input/output for I2C2         |  |  |

| TMS      | 19 <sup>(2)</sup><br>11 <sup>(3)</sup> | 22 <sup>(2)</sup><br>14 <sup>(3)</sup> | 25 <sup>(2)</sup><br>15 <sup>(3)</sup> | 12                              | I           | ST             | JTAG Test mode select pin                             |  |  |

| TCK      | 14                                     | 17                                     | 18                                     | 13                              | I           | ST             | JTAG test clock input pin                             |  |  |

| TDI      | 13                                     | 16                                     | 17                                     | 35                              | 0           | _              | JTAG test data input pin                              |  |  |

| TDO      | 15                                     | 18                                     | 19                                     | 32                              | 0           | _              | JTAG test data output pin                             |  |  |

| RTCC     | 4                                      | 7                                      | 2                                      | 24                              | 0           | ST             | Real-Time Clock alarm output                          |  |  |

| CVREF-   | 28                                     | 3                                      | 34                                     | 20                              | I           | Analog         | Comparator Voltage Reference (low)                    |  |  |

| CVREF+   | 27                                     | 2                                      | 33                                     | 19                              | I           | Analog         | Comparator Voltage Reference (high)                   |  |  |

| CVREFOUT | 22                                     | 25                                     | 28                                     | 14                              | 0           | Analog         | Comparator Voltage Reference output Comparator Inputs |  |  |

| C1INA    | 4                                      | 7                                      | 2                                      | 24                              | I           | Analog         |                                                       |  |  |

| C1INB    | 3                                      | 6                                      | 1                                      | 23                              | I           | Analog         | †                                                     |  |  |

| C1INC    | 2                                      | 5                                      | 36                                     | 22                              | I           | Analog         | 1                                                     |  |  |

| C1IND    | 1                                      | 4                                      | 35                                     | 21                              | I           | Analog         | 1                                                     |  |  |

| C2INA    | 2                                      | 5                                      | 36                                     | 22                              | I           | Analog         |                                                       |  |  |

| C2INB    | 1                                      | 4                                      | 35                                     | 21                              | I           | Analog         |                                                       |  |  |

| C2INC    | 4                                      | 7                                      | 2                                      | 24                              | I           | Analog         |                                                       |  |  |

| C2IND    | 3                                      | 6                                      | 1                                      | 23                              | I           | Analog         |                                                       |  |  |

| C3INA    | 23                                     | 26                                     | 29                                     | 15                              | I           | Analog         |                                                       |  |  |

| C3INB    | 22                                     | 25                                     | 28                                     | 14                              | I           | Analog         |                                                       |  |  |

| C3INC    | 27                                     | 2                                      | 33                                     | 19                              | I           | Analog         |                                                       |  |  |

| C3IND    | 1                                      | 4                                      | 35                                     | 21                              | I           | Analog         |                                                       |  |  |

| C10UT    | PPS                                    | PPS                                    | PPS                                    | PPS                             | 0           | _              | Comparator Outputs                                    |  |  |

| C2OUT    | PPS                                    | PPS                                    | PPS                                    | PPS                             | 0           |                |                                                       |  |  |

| C3OUT    | PPS                                    | PPS                                    | PPS                                    | PPS                             | 0           |                |                                                       |  |  |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

\_\_ = N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

- 2: Pin number for PIC32MX1XX devices only.

- 3: Pin number for PIC32MX2XX devices only.

# 8.0 OSCILLATOR CONFIGURATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 6. "Oscillator Configuration"** (DS60001112), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- · Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

### REGISTER 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 4 **CHDHIF:** Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected (either the source or the destination address is invalid)

- 0 = No interrupt is pending

**FIGURE 10-1:** PIC32MX1XX/2XX 28/36/44-PIN FAMILY FAMILY USB INTERFACE DIAGRAM FRC Oscillator 8 MHz Typical TUN<5:0>(3) Primary Oscillator UFIN(4) (Posc) Div x PLL Div 2 UFRCEN<sup>(2)</sup> osc1 UPLLIDIV<sup>(5)</sup> UPLLEN<sup>(5)</sup> OSC2 **USB Module** USB SRP Charge Voltage Comparators Bus X SRP Discharge 48 MHz USB Clock(6) Full Speed Pull-up D+(1) Registers and Control Interface Host Pull-down SIE Transceiver ow Speed Pull-up D-(1) DMA System ŔAM Host Pull-down ID Pull-up ID<sup>(1)</sup> VBUSON<sup>(1)</sup> VUSB3V3 Transceiver Power 3.3V Pins can be used as digital input/output when USB is not enabled. Note 1: This bit field is contained in the OSCCON register. This bit field is contained in the OSCTRM register. 4: USB PLL UFIN requirements: 4 MHz. This bit field is contained in the DEVCFG2 register. A 48 MHz clock is required for proper USB operation.

#### REGISTER 10-16: U1SOF: USB SOF THRESHOLD REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | -                 | -                 | 1                 | -                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | -                 | -                 | -                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

Typical values of the threshold are:

01001010 **= 64-byte packet**

00101010 = 32-byte packet

00011010 = **16-byte packet**

00010010 = 8-byte packet

### REGISTER 10-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | -                 | -                 | -                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7.0          |                   |                   | В                 | DTPTRL<15:        | )>                |                   |                  | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: Buffer Descriptor Table Base Address bits

This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

| $\Box$ |

|--------|

| Ś      |

| 8      |

| 3000   |

| 0      |

| 0      |

| _      |

| _      |

| 0      |

| 89     |

| ے      |

|        |

| page   |

| ~      |

| ∺      |

| v      |

| _      |

| w      |

| 139    |

| _      |

|        |

|        |

| TABLE 11-7: | PERIPHERAL PIN SELECT OUTPUT REGISTER MAP | (CONTINUED) |

|-------------|-------------------------------------------|-------------|

|             |                                           |             |

| SS                          |                      |               |       |       |       |       |       |       |      | Ві   | its  |      |      |      |      |               |         |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|---------------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2          | 17/1    | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _             | _       | _    | 0000       |

| 1 540                       | THE DOTA             | 15:0          |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB8          | 3<3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16         |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    | _    | _             | _       | _    | 0000       |

| . 500                       | THE BOTT             | 15:0          |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    |      | RPB9          | >3:0>   |      | 0000       |

| FB54                        | RPB10R               | 31:16         |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    | _    | _             | _       |      | 0000       |

| . 50.                       |                      | 15:0          |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    |      | RPB10         | 0<3:0>  |      | 0000       |

| FB58                        | RPB11R               | 31:16         |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |               | _       | _    | 0000       |

|                             |                      | 15:0          |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPB1          | 1<3:0>  |      | 0000       |

| FB60                        | RPB13R               | 31:16         |       | _     | _     | _     | _     | _     | _    |      |      | _    | _    | _    | _    | _             |         |      | 0000       |

|                             |                      | 15:0          |       | _     | _     | _     | _     | _     | _    |      |      | _    | _    | _    |      | RPB1          |         |      | 0000       |

| FB64                        | RPB14R               | 31:16         |       | _     | _     |       |       | _     | _    |      |      | _    | _    | _    | _    |               |         |      | 0000       |

|                             |                      | 15:0          |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    |      | RPB1          | 4<3:0>  |      | 0000       |

| FB68                        | RPB15R               | 31:16         |       |       | _     |       |       |       | _    | _    |      |      |      |      | _    |               | -       | _    | 0000       |

|                             |                      | 15:0          |       |       | _     |       |       |       | _    | _    |      |      |      |      |      | RPB1          |         |      | 0000       |

| FB6C                        | RPC0R(3)             | 31:16         |       |       | _     |       | _     |       | _    | _    |      |      |      | _    | _    | RPC0          | -       | _    | 0000       |

|                             |                      | 15:0          |       |       | _     |       | _     |       | _    | _    |      |      |      | _    |      |               |         |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16         |       | _     | _     |       | _     |       |      |      |      | _    |      |      | _    |               | <3:0>   | _    | 0000       |

|                             |                      | 15:0<br>31:16 |       |       |       |       | _     |       |      |      |      | _    |      |      |      |               | \\ 3.0> | _    | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 15:0          |       |       |       |       | _     |       |      |      |      | _    |      |      | _    | —<br>BDC2     | 2<3:0>  |      | 0000       |

|                             |                      |               |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      |               |         |      | 0000       |

| FB78                        | RPC3R(3)             | 31:16<br>15:0 |       | _     | _     |       |       | _     | _    |      | _    |      | _    | _    | _    | —<br>PDC3     | S<3:0>  | _    | 0000       |

|                             |                      | 31:16         |       | _     | _     |       |       |       |      | _    |      |      |      | _    | _    | — KF03        | _       | _    | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 15:0          |       | _     |       |       |       |       |      |      | _    |      |      |      | _    | RPC4          |         |      | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       |      |      | _    |      |      | _    | _    | KF 04         |         | _    | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 15:0          |       |       |       |       |       |       | _    |      |      | _    |      | _    |      |               | 5<3:0>  |      | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       |      |      | _    |      |      | _    | _    | — KF03        | _       | _    | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 15:0          |       | _     | _     |       |       | _     |      |      | _    |      | _    | _    |      | RPC6          |         |      | 0000       |

|                             |                      | 31:16         |       | _     | _     |       |       | _     |      |      | _    |      | _    | _    | _    | — KF00        | _       | _    | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      |      | RPC7          |         |      | 0000       |

|                             | 15.0                 |               |       | _     | _     |       | _     | _     | _    |      | _    | _    | _    |      | RPU/ | <b>~</b> 3.0≥ |         | 0000 |            |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

This register is only available on PIG32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

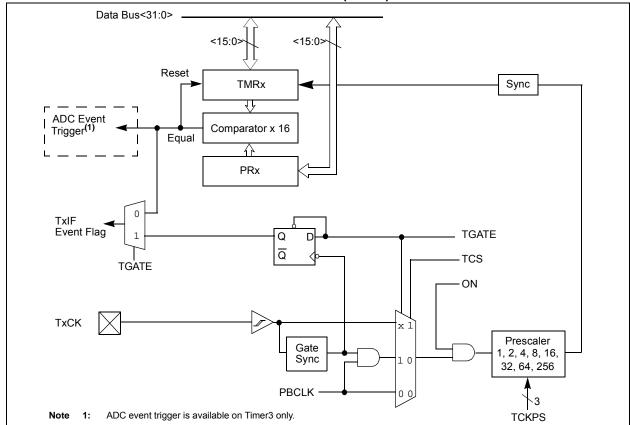

### 13.0 TIMER2/3, TIMER4/5

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "Timers" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- · Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

Note:

In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through Timer5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or Timer4 and 'y' represents Timer3 or Timer5.

### 13.1 Additional Supported Features

- · Selectable clock prescaler

- · Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

#### FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

#### TXCON: TYPE B TIMER CONTROL REGISTER REGISTER 13-1:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        | _                    | _                 | -                   | _                 | _                  | -                 | _                  | _                |

| 22:16        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        | _                    | _                 | _                   | _                 | _                  | -                 | _                  | _                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | _                  | _                 | _                  | _                |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

Legend:

W = Writable bit R = Readable bit U = Unimplemented bit, read as '0'

'1' = Bit is set n = Value at POR '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Read as '0'

bit 15 ON: Timer On bit(1,3)

> 1 = Module is enabled 0 = Module is disabled

bit 14 Unimplemented: Read as '0' bit 13

**SIDL:** Stop in Idle Mode bit<sup>(4)</sup>

1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

TCKPS<2:0>: Timer Input Clock Prescale Select bits(3) bit 6-4

111 = 1:256 prescale value

110 = 1:64 prescale value

101 = 1:32 prescale value

100 = 1:16 prescale value

011 = 1:8 prescale value

010 = 1:4 prescale value

001 = 1:2 prescale value

000 = 1:1 prescale value

- Note 1: When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- 3: While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

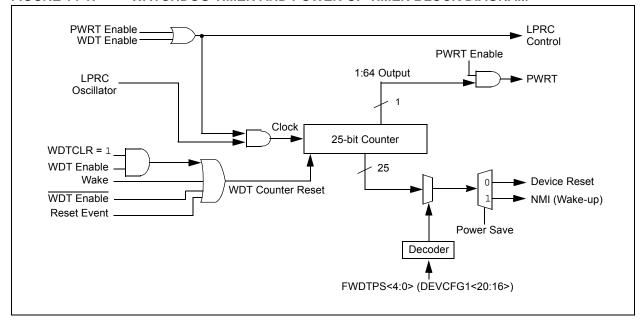

### 14.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 9. "Watchdog, Deadman, and Power-up Timers"** (DS60001114), which are available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | -                 | _                 | _                 | _                 | _                |                  |

| 00:40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

Legend:y = Values set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

1 = Enables the WDT if it is not enabled by the device configuration

0 = Disable the WDT if it was enabled in software

bit 14-7 Unimplemented: Read as '0'

bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

bit 1 WDTWINEN: Watchdog Timer Window Enable bit

1 = Enable windowed Watchdog Timer0 = Disable windowed Watchdog Timer

bit 0 WDTCLR: Watchdog Timer Reset bit

1 = Writing a '1' will clear the WDT

0 = Software cannot force this bit to a '0'

**Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 13.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extended

bit 14-13 Unimplemented: Read as '0'

bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit underrun generates error events

0 = Transmit underrun does not generate error events

bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error that stops SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit (1)

1 = Audio protocol enabled

0 = Audio protocol disabled

bit 6-5 Unimplemented: Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right-Justified mode

01 = Left-Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

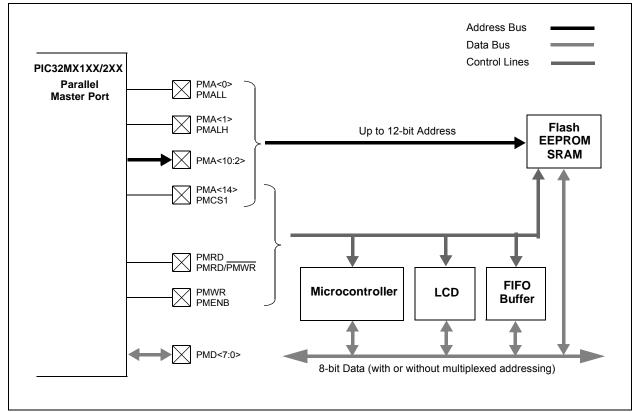

# 20.0 PARALLEL MASTER PORT (PMP)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 13. "Parallel Master Port (PMP)"** (DS60001128), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PMP is a parallel 8-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable.

Key features of the PMP module include:

- · Fully multiplexed address/data mode

- Demultiplexed or partially multiplexed address/ data mode

- up to 11 address lines with single Chip Select

- up to 12 address lines without Chip Select

- · One Chip Select line

- Programmable strobe options

- Individual read and write strobes or;

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- · Programmable polarity on control signals

- · Legacy parallel slave port support

- · Enhanced parallel slave support

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- · Selectable input voltage levels

Figure 20-1 illustrates the PMP module block diagram.

FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                             | (unless            | otherwi | se state | ed) conditions: 2.3V to 3.6V ed) $-40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp}$ |                          |  |  |

|--------------------|--------|-----------------------------|--------------------|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Param.             | Symbol | Characteristic              | Min.               | Тур.    | Max.     | Units                                                                                                                                                          | Conditions               |  |  |

| DO10               | VoL    | Output Low Voltage I/O Pins | _                  | _       | 0.4      | V                                                                                                                                                              | IOL ≤ 10 mA, VDD = 3.3V  |  |  |

|                    |        | Output High Voltage         | 1.5 <sup>(1)</sup> |         | _        |                                                                                                                                                                | IOH ≥ -14 mA, VDD = 3.3V |  |  |

| DO20               | Vон    | I/O Pins                    | 2.0 <sup>(1)</sup> |         | _        | V                                                                                                                                                              | IOH ≥ -12 mA, VDD = 3.3V |  |  |

| DO20               | VOH    |                             | 2.4                | _       | _        | V                                                                                                                                                              | IOH ≥ -10 mA, VDD = 3.3V |  |  |

|                    |        |                             | 3.0(1)             | _       | _        |                                                                                                                                                                | IOH ≥ -7 mA, VDD = 3.3V  |  |  |

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| TABLE 30-11. ELECTRICAL CHARACTERISTICS. BOX |        |                                                        |                                                                                                                                                                                                                                                |         |      |       |            |  |  |  |

|----------------------------------------------|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| DC CHARACTERISTICS                           |        |                                                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |            |  |  |  |

| Param.<br>No.                                | Symbol | Characteristics                                        | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions |  |  |  |

| BO10                                         | VBOR   | BOR Event on VDD transition high-to-low <sup>(2)</sup> | 2.0                                                                                                                                                                                                                                            | _       | 2.3  | V     | _          |  |  |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

### TABLE 30-39: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |       |   |   |   |  |  |

|--------------------|---------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|---|---|--|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                      | Min. Typ. Max. Units Condi                                                                                                                                                                                                                        |       |   |   |   |  |  |

| PM11               | Twr     | PMWR Pulse Width                                                    | _                                                                                                                                                                                                                                                 | 1 Трв | _ | _ | _ |  |  |

| PM12               | TDVSU   | Data Out Valid before PMWR or PMENB goes Inactive (data setup time) | _                                                                                                                                                                                                                                                 | 2 TPB | _ | _ | _ |  |  |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data Out Invalid (data hold time)          | _                                                                                                                                                                                                                                                 | 1 Трв |   | _ | _ |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

### **TABLE 30-40: OTG ELECTRICAL SPECIFICATIONS**

| IABLE         | ABLE 30-40: OTG ELECTRICAL SPECIFICATIONS |                                   |      |                                                                                                                                                                                                                                               |      |       |                                                                                   |  |  |  |  |

|---------------|-------------------------------------------|-----------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------|--|--|--|--|

| AC CHA        | AC CHARACTERISTICS                        |                                   |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industria $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |      |       |                                                                                   |  |  |  |  |

| Param.<br>No. | Symbol                                    | Characteristics <sup>(1)</sup>    | Min. | Тур.                                                                                                                                                                                                                                          | Max. | Units | Conditions                                                                        |  |  |  |  |

| USB313        | VUSB3V3                                   | USB Voltage                       | 3.0  | _                                                                                                                                                                                                                                             | 3.6  | V     | Voltage on Vusb3v3<br>must be in this range<br>for proper USB<br>operation        |  |  |  |  |

| USB315        | VILUSB                                    | Input Low Voltage for USB Buffer  | _    | _                                                                                                                                                                                                                                             | 0.8  | V     | _                                                                                 |  |  |  |  |

| USB316        | VIHUSB                                    | Input High Voltage for USB Buffer | 2.0  | _                                                                                                                                                                                                                                             | _    | V     | _                                                                                 |  |  |  |  |

| USB318        | VDIFS                                     | Differential Input Sensitivity    | _    |                                                                                                                                                                                                                                               | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |  |  |  |

| USB319        | VCM                                       | Differential Common Mode Range    | 0.8  | _                                                                                                                                                                                                                                             | 2.5  | V     | _                                                                                 |  |  |  |  |

| USB320        | Zout                                      | Driver Output Impedance           | 28.0 | _                                                                                                                                                                                                                                             | 44.0 | Ω     | _                                                                                 |  |  |  |  |

| USB321        | Vol                                       | Voltage Output Low                | 0.0  | _                                                                                                                                                                                                                                             | 0.3  | V     | 1.425 kΩ load connected to Vusb3v3                                                |  |  |  |  |

| USB322        | Vон                                       | Voltage Output High               | 2.8  | _                                                                                                                                                                                                                                             | 3.6  | V     | 1.425 kΩ load connected to ground                                                 |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

NOTES: