Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

|                            |                                                                                  |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256d-50i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

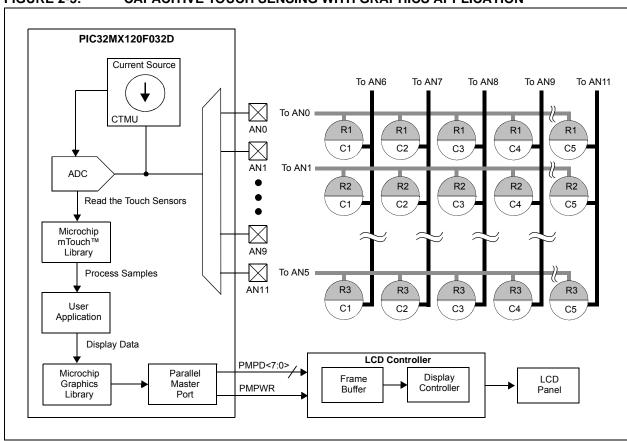

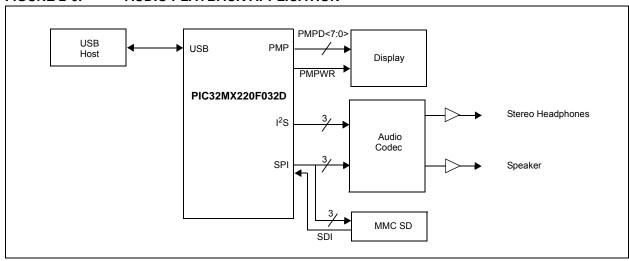

# 2.9 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-5: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

#### 4.2 Bus Matrix Control Registers

#### TABLE 4-2: BUS MATRIX REGISTER MAP

| ess                         |                         | ø.        |       |       |       |       |       |       |      |      |      | Bits         |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | _     |       | _     | _     | _     | _     |      | _    |      | _            | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | PINIYCOM, ,             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | BMXWSDRM     | _    | _         | _         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | -    | _            | _    | _         | _         | _         | _          | _        | 0000          |

| 2010                        | BIVINDREBA              | 15:0      |       |       |       |       |       |       |      |      | BM   | XDKPBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         | _         | _         | _          | _        | 0000          |

| 2020                        | DIVINDODDA              | 15:0      |       |       |       |       |       |       |      |      | BM   | XDUDBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         | _         | _         | _          | _        | 0000          |

|                             |                         | 15:0      |       |       |       |       |       |       |      |      | BM   | XDUPBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |       |       |       |       |       |      |      | BM   | XDRMSZ<31:0  | >    |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |       | ı     |       | ı     |       |      | ı    |      |              | ı    |           | 1         |           |            |          | XXXX          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         |           | BMXPUPB/  | \<19:16>   |          | 0000          |

|                             |                         | 15:0      |       |       |       |       |       |       |      |      | BM   | XPUPBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |       |       |       |       |       |       |      |      | BM   | XPFMSZ<31:0  | >    |           |           |           |            |          | XXXX          |

|                             |                         | 15:0      |       |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |       |       |       |       |       |       |      |      | BMX  | (BOOTSZ<31:0 | )>   |           |           |           |            |          | 0000          |

|                             | , , , ,                 | 15:0      |       |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

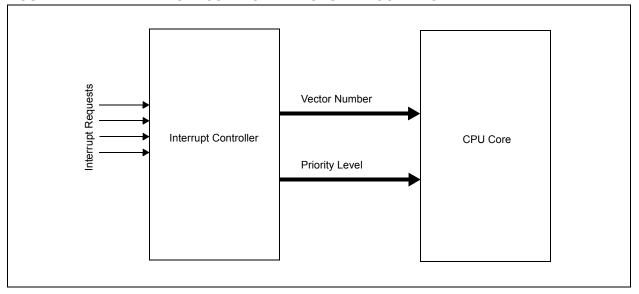

#### 7.0 INTERRUPT CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupt Controller"** (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- · Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- · Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- · User-configurable interrupt vector spacing

**Note:** The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

Note: This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit

definitions.

#### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 31. "Direct Memory Access (DMA) Controller"** (DS60001117), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

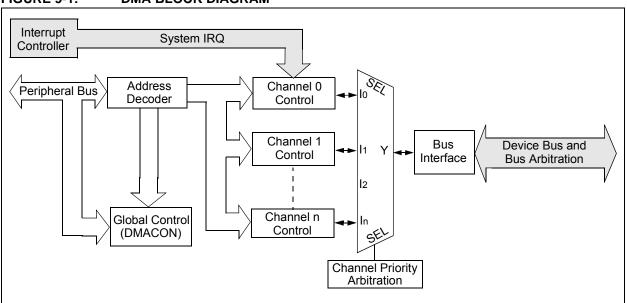

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- · Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- · Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- · Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt)

DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- · DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

#### REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     |                   |                   |                   | CHSSA<            | 23:16>            |                   |                  |                  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      |                   |                   |                   | CHSSA<            | <15:8>            |                   |                  |                  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

**Note:** This must be the physical address of the source.

#### REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | CHDSA<            | 23:16>            |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSA-            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits

Channel destination start address.

**Note:** This must be the physical address of the destination.

TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | ı     | _     | _     | _     | _     | _     | _    | _    | ı     | _        | _     | _        | _      | _      | _         | -        | 0000       |

| 3200                        | OTFRIVIL' 7                     | 15:0      | 1     | _     | _     |       | -     | _     |      | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _        | _      | _      | _         | _        | 0000       |

| 3290                        | O II KWII V                     | 15:0      | -     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _        | _      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _        | _      | _      | _         | _        | 0000       |

| 32A0                        | OTTOR                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    |       | PID      | <3:0> |          |        | EP     | <3:0>     | •        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | 1     | _     | _     | _     | -     | _     | _    | _    | 1     | _        | _     | _        | _      | _      | -         | _        | 0000       |

| 52B0                        | 0150F                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       | •        |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | _        | _      | _      | _         | _        | 0000       |

| 5200                        | UIBDIP2                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTRI  | H<7:0> |        |           |          | 0000       |

| E2D0                        | LIADDED2                        | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | _        | _      | _      | _         | _        | 0000       |

| 52D0                        | U1BDTP3                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 5250                        | U1CNFG1                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | _        | _      | _      | _         | _        | 0000       |

| 52E0                        | UTCNEGT                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | UTEYE | UOEMON   |       | USBSIDL  | _      | _      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | ı     | _     | _     | _     | _     | _     | _    | _    | I     | _        | _     | _        | _      | _      | -         | _        | 0000       |

| 5300                        | UTEPU                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | _        | _      | _      | _         | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _        | _      | _      | _         | _        | 0000       |

| 5520                        | UTEFZ                           | 15:0      | ı     | _     | _     | _     | _     | _     | _    | _    | ı     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _        | _      | _      | -         | _        | 0000       |

| 3330                        | OTEFS                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _        | _      | _      | -         | _        | 0000       |

| 3340                        | OTEF4                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | 1     | _     | _     |       | -     | _     |      | _    | ı     | _        | _     | _        | _      | _      | I         |          | 0000       |

| 5550                        | UIEFS                           | 15:0      | ı     | _     | _     | _     | _     | _     | _    | _    | ı     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | 1     | _     | _     | _     | _     | _     | _    | _    | ı     | _        | _     |          | _      | _      |           | _        | 0000       |

| 3300                        | UIEFU                           | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | 1     | _     |       | _     | _     |       | _    | _    |       | _        |       |          | _      | _      |           | _        | 0000       |

| 3370                        | UIEFI                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | 1     | _     |       |       |       |       |      | _    |       | _        |       |          | _      | _      |           | _        | 0000       |

| 3360                        | UIEFO                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    |       | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> This register does not have associated SET and INV registers.

<sup>3:</sup> This register does not have associated CLR, SET and INV registers.

<sup>4:</sup> Reset value for this bit is undefined.

TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| sss                         |                      |               |       |       |       |       |       |       |      | Ві   | ts   |      |      |      |      |           |          |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1     | 16/0 | All Resets |

| FB00                        | RPA0R                | 31:16<br>15:0 | _     |       | _     |       |       |       | _    |      |      | _    | _    | _    | -    | —<br>RPA0 | -        | _    | 0000       |

|                             |                      | 31:16         |       |       |       |       |       |       |      |      |      |      |      | _    | _    | _         | _        | _    | 0000       |

| FB04                        | RPA1R                | 15:0          | _     | _     | _     |       | _     |       |      | _    |      | _    | _    | _    |      | RPA1      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     |       | _     |       | _     |       | _    | _    |      | _    | _    | _    |      | _         | _        | _    | 0000       |

| FB08                        | RPA2R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA2      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| FB0C                        | RPA3R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA3      | <3:0>    |      | 0000       |

| ED40                        | RPA4R                | 31:16         | _     | 1     | _     | -     | _     | -     | _    | _    | 1    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| FB10                        | RPA4R                | 15:0          | _     |       | _     | _     | _     |       | _    | _    |      | _    | _    | _    |      | RPA4      | <3:0>    |      | 0000       |

| FB20                        | RPA8R <sup>(1)</sup> | 31:16         | _     | 1     | _     | -     | _     | -     | _    | _    | 1    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| 1 020                       | IN AOIN.             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA8      | <3:0>    |      | 0000       |

| FB24                        | RPA9R <sup>(1)</sup> | 31:16         | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | _    | -    | _         | _        | _    | 0000       |

|                             |                      | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA9      | <3:0>    |      | 0000       |

| FB2C                        | RPB0R                | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |           |          | _    | 0000       |

|                             |                      | 15:0          |       |       | _     |       |       |       |      |      |      |      |      |      |      | RPB0      |          |      | 0000       |

| FB30                        | RPB1R                | 31:16<br>15:0 |       |       | _     |       |       |       |      |      |      |      |      |      |      | RPB1      | -2:0>    | _    | 0000       |

|                             |                      | 31:16         |       |       | _     |       |       |       |      |      |      | _    | _    | _    | _    | — KFB1    | <u> </u> | _    | 0000       |

| FB34                        | RPB2R                | 15:0          | _     |       | _     |       |       |       |      |      |      | _    | _    |      |      | RPB2      |          | _    | 0000       |

|                             |                      | 31:16         | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _    | —         | _        | l _  | 0000       |

| FB38                        | RPB3R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB3      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _         | _        | _    | 0000       |

| FB3C                        | RPB4R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB4      | <3:0>    |      | 0000       |

| ED 40                       | DDDCD                | 31:16         | _     | 1     | _     | -     | _     | -     | _    | _    | 1    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| FB40                        | RPB5R                | 15:0          | _     |       | _     |       | _     | -     | _    | _    |      | _    | _    | _    |      | RPB5      | <3:0>    |      | 0000       |

| FB44                        | RPB6R <sup>(2)</sup> | 31:16         | -     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _         | _        | _    | 0000       |

| 1 044                       | INF DOIN, 7          | 15:0          | _     | 1     | _     | 1     | -     | 1     | -    | -    | 1    | _    | _    | _    |      | RPB6      | <3:0>    |      | 0000       |

| FB48                        | RPB7R                | 31:16         | _     |       | _     |       | _     |       | _    | _    |      | _    |      |      | _    | _         | _        | _    | 0000       |

| . 2 .0                      | 2                    | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | RPB7      | <3:0>    |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register is only available on 44-pin devices. Note 1:

This register is only available on PIC32MX1XX devices. 2:

This register is only available on 36-pin and 44-pin devices.

#### REGISTER 11-3: CNCONx: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A, B, C)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notice (CN) Control ON bit

1 = CN is enabled0 = CN is disabled

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

**SIDL:** Stop in Idle Control bit 1 = Idle mode halts CN operation

0 = Idle does not affect CN operation

bit 12-0 Unimplemented: Read as '0'

#### REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 Unimplemented: Read as '0'

bit 1 **TCS**: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

#### 14.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 9. "Watchdog, Deadman, and Power-up Timers"** (DS60001114), which are available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

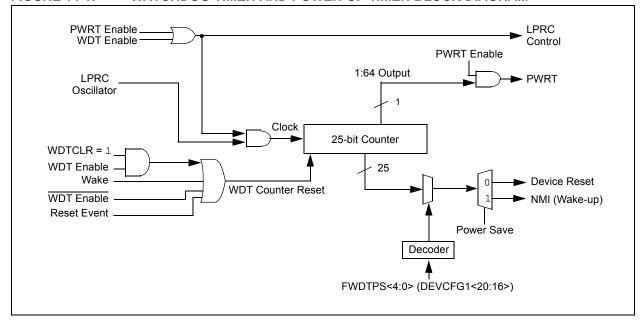

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

### 17.1 SPI Control Registers

#### TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| ess                         |                                 | •         |               |         |        |              |              |              |          | Bit    | ts      |          |        |        |             |          |        |         | "          |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|--------------|--------------|----------|--------|---------|----------|--------|--------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9     | 24/8   | 23/7    | 22/6     | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2: | )>     | MCLKSEL | _        | _      | _      | _           | _        | SPIFE  | ENHBUF  | 0000       |

| 3000                        | 31 11001                        | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP      | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | L<1:0>  | 0000       |

| E010                        | SPI1STAT                        | 31:16     | _             | _       | _      |              | RXE          | BUFELM<4:    | 0>       |        | _       | -        | -      |        | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 3610                        | OI HOIAI                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _        | SPITUR | SRMT    | SPIROV   | SPIRBE | -      | SPITBE      | _        | SPITBF | SPIRBF  | 8000       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |        |              |              |              |          | DATA<  | 31.0>   |          |        |        |             |          |        |         | 0000       |

| 3620                        | OI IIDOI                        | 15:0      |               |         |        |              |              |              |          | DAIA   | 01.0    |          |        |        |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     |               | _       | _      | _            | _            | _            | _        | _      | _       | _        | _      | _      | _           | _        | _      | _       | 0000       |

| 3630                        | OI TIBICO                       | 15:0      |               | _       | _      |              |              |              |          |        | E       | RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | _             | _       | _      | _            | _            | _            | _        | _      | _       | -        | _      | -      | _           | _        | _      | _       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _        | _      | _      | AUD<br>MONO | _        | AUDMO  | D<1:0>  | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2: | )>     | MCLKSEL | _        | _      | _      | _           | _        | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | SPIZCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP      | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | L<1:0>  | 0000       |

| EA40                        | SPI2STAT                        | 31:16     | _             | _       | _      |              | RXE          | BUFELM<4:    | 0>       |        | _       | ı        | ı      |        | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5A10                        | SFIZSTAT                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _        | SPITUR | SRMT    | SPIROV   | SPIRBE | -      | SPITBE      | _        | SPITBF | SPIRBF  | 8000       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |              |              |          | DATA<  | 31.05   |          |        |        |             |          |        |         | 0000       |

| 5A20                        | SFIZDOI                         | 15:0      |               |         |        |              |              |              |          | DAIA   | 31.0    |          |        |        |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | _             | _       | _      | _            | _            | _            | _        | _      | _       | -        | _      | _      | _           | _        | _      | -       | 0000       |

| 5A30                        | OI IZDING                       | 15:0      |               | _       | _      |              |              |              |          |        | E       | RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | _             | _       | _      | _            | _            | _            | _        | _      | _       | _        | _      | -      | _           | _        | _      | -       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   |          | 1      |        | AUD<br>MONO |          | AUDMO  | )D<1:0> | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### 19.1 UART Control Registers

#### TABLE 19-1: UART1 AND UART2 REGISTER MAP

| ess                         |                       |           |        |        |        |       |        |       |       | Bi          | ts          |         |       |             |        |      |        |       | ,,         |

|-----------------------------|-----------------------|-----------|--------|--------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|-------------|--------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4        | 19/3   | 18/2 | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | _     | _      | _     | _     | _           | _           | _       | _     | _           | _      | _    | _      | _     | 0000       |

| 0000                        | OTWODE                | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN:  | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE | L<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | _      | _      | _      | _     | _      | _     | _     | ADM_EN      |             |         |       | ADDR        |        |      |        |       | 0000       |

| 0010                        | O IOIA.               | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR | OERR   | URXDA | 0110       |

| 6020                        | U1TXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | -           | _      | _    | _      | _     | 0000       |

| 0020                        | UTTAINEG              | 15:0      | _      | _      | _      | _     | _      | _     | -     |             |             |         | Tra   | nsmit Regis | ster   |      |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | -           | _      | _    | _      | _     | 0000       |

| 0000                        | OTIVANLO              | 15:0      | _      | _      | _      | _     | _      | _     | -     |             |             |         | Re    | ceive Regis | ster   |      |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | -           | _      | _    | _      | _     | 0000       |

| 00+0                        | O IDICO.              | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |             |        |      |        |       | 0000       |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | -           | _      | _    | _      | _     | 0000       |

| 0200                        | 02MODE: 1             | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN:  | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE | L<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | _      | _      | _      | _     | _      | _     | -     | ADM_EN      |             |         |       | ADDR        | R<7:0> |      |        |       | 0000       |

| 0210                        | 02017                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR | OERR   | URXDA | 0110       |

| 6220                        | U2TXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | -           | _      | _    | _      | _     | 0000       |

| 0220                        | OZIANLO               | 15:0      | _      | _      | _      | _     | _      | _     | _     |             |             |         | Tra   | nsmit Regis | ster   |      |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | _      | _      | _      | _     | _      | _     | -     | _           | _           | _       | _     | -           | _      | _    | _      | _     | 0000       |

| 0230                        | UZIVANLU              | 15:0      | _      | _      | _      | _     | _      | _     | -     |             |             |         | Re    | ceive Regis | ster   |      |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | _      | -      | _      | -     | _      | _     | 1     | _           | _           | _       | -     | -           | _      | _    | _      | _     | 0000       |

| 0240                        | OZDNO,                | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |             |        |      |        |       | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| PIC32M | X1XX/2X | (X 28/3 | 6/44-PI | NFAM | ILY |  |

|--------|---------|---------|---------|------|-----|--|

| NOTES: |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|--------------------------|----------------------|--------------------|-------------------------|---------------------------|-------------------|------------------|------------------|

| 31:24        | U-0                      | U-0                  | U-0                | U-0                     | U-0                       | U-0               | U-0              | U-0              |

|              | _                        | _                    | _                  | _                       | 1                         | _                 | _                | _                |

| 23:16        | U-0                      | U-0                  | U-0                | U-0                     | U-0                       | U-0               | U-0              | U-0              |

|              | _                        | _                    | _                  | _                       |                           | _                 | _                | _                |

| 15:8         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |

|              | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |

| 7:0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |

|              | ARPT<7:0> <sup>(2)</sup> |                      |                    |                         |                           |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ALRMEN: Alarm Enable bit (1,2)

1 = Alarm is enabled

0 = Alarm is disabled

bit 14 **CHIME**: Chime Enable bit<sup>(2)</sup>

1 = Chime is enabled - ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

0 = Chime is disabled – ARPT<7:0> stops once it reaches 0x00

bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse.

When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

bit 12 **ALRMSYNC:** Alarm Sync bit<sup>(3)</sup>

1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits(2)

0000 = Every half-second

0001 = Every second

0010 = Every 10 seconds

0011 = Every minute

0100 = Every 10 minutes

0101 = Every hour

0110 = Once a day

0111 = Once a week

1000 = Once a month

1001 = Once a year (except when configured for February 29, once every four years)

1010 = Reserved; do not use

1011 = Reserved; do not use

11xx = Reserved; do not use

Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIMF = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is reset only on a Power-on Reset (POR).

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              |                   | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |

| 23:16        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              | _                 | MIN10<2:0>        |                   |                   | MIN01<3:0>        |                   |                  |                  |

| 15:8         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              | _                 | SEC10<2:0>        |                   |                   | SEC01<3:0>        |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

TABLE 30-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS                      |                        |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                                           |  |  |  |

|-----------------------------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| Parameter No.                           | Typical <sup>(3)</sup> | Max. | Units                                                                                                                                                                                                                                          | Conditions                                |  |  |  |

| Operating Current (IDD) (Notes 1, 2, 5) |                        |      |                                                                                                                                                                                                                                                |                                           |  |  |  |

| DC20                                    | 2                      | 3    | mA                                                                                                                                                                                                                                             | 4 MHz (Note 4)                            |  |  |  |

| DC21                                    | 7                      | 10.5 | mA                                                                                                                                                                                                                                             | 10 MHz                                    |  |  |  |

| DC22                                    | 10                     | 15   | mA                                                                                                                                                                                                                                             | 20 MHz (Note 4)                           |  |  |  |

| DC23                                    | 15                     | 23   | mA                                                                                                                                                                                                                                             | 30 MHz (Note 4)                           |  |  |  |

| DC24                                    | 20                     | 30   | mA                                                                                                                                                                                                                                             | 40 MHz                                    |  |  |  |

| DC25                                    | 100                    | 150  | μA                                                                                                                                                                                                                                             | +25°C, 3.3V LPRC (31 kHz) <b>(Note 4)</b> |  |  |  |

- **Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- $\bullet \ \ CPU \ executing \ while (1) \ \ statement \ from \ Flash$

- · RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

#### **TABLE 30-13: COMPARATOR SPECIFICATIONS**

| DC CHARACTERISTICS |        |                                                        | Standard Operating Conditions (see Note 4): 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |                                                                               |

|--------------------|--------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                        | Min.                                                                                                                                                                                                                                                        | Typical | Max. | Units | Comments                                                                      |

| D300               | VIOFF  | Input Offset Voltage                                   | _                                                                                                                                                                                                                                                           | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                     |

| D301               | VICM   | Input Common Mode Voltage                              | 0                                                                                                                                                                                                                                                           | _       | VDD  | V     | AVDD = VDD,<br>AVSS = VSS<br>(Note 2)                                         |

| D302               | CMRR   | Common Mode Rejection Ratio                            | 55                                                                                                                                                                                                                                                          | _       | _    | dB    | Max Vicm = (VDD - 1)V (Note 2)                                                |

| D303A              | TRESP  | Large Signal Response Time                             | _                                                                                                                                                                                                                                                           | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                          |

| D303B              | TSRESP | Small Signal Response Time                             | _                                                                                                                                                                                                                                                           | 1       | _    | μS    | This is defined as an input step of 50 mV with 15 mV of overdrive (Note 2)    |

| D304               | ON2ov  | Comparator Enabled to Output<br>Valid                  | _                                                                                                                                                                                                                                                           | _       | 10   | μЅ    | Comparator module is configured before setting the comparator ON bit (Note 2) |

| D305               | IVREF  | Internal Voltage Reference                             | 1.14                                                                                                                                                                                                                                                        | 1.2     | 1.26 | V     | _                                                                             |

| D312               | TSET   | Internal Comparator Voltage DRC Reference Setting time | _                                                                                                                                                                                                                                                           | _       | 10   | μs    | (Note 3)                                                                      |

- **Note 1:** Response time measured with one comparator input at (VDD 1.5)/2, while the other input transitions from Vss to VDD.

- **2:** These parameters are characterized but not tested.

- 3: Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

- **4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

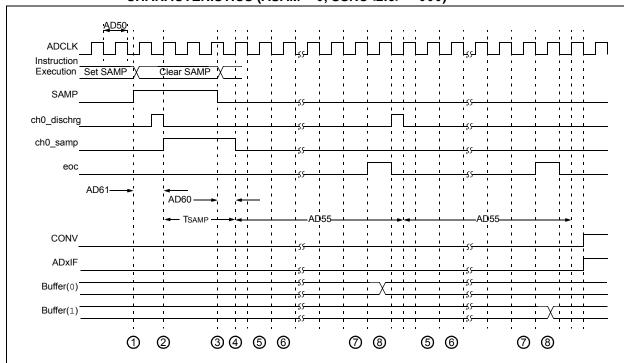

FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

- 1 Software sets ADxCON. SAMP to start sampling.

- 2 Sampling starts after discharge period. TSAMP is described in Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual".

- (3) Software clears ADxCON. SAMP to start conversion.

- 4 Sampling ends, conversion sequence starts.

- (5) Convert bit 9.

- 6 Convert bit 8.

- 7 Convert bit 0.

- (8) One TAD for end of conversion.

#### 33.1 Package Marking Information (Continued)

36-Lead VTLA

44-Lead VTLA

44-Lead QFN

44-Lead TQFP

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

By-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (a)

can be found on the outer packaging for this package.

**Note:** If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information.