Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256d-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

## 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|                 |                             | OUT I/O D<br>Pin Nui                        |                                       |                                 |             | Í                    |                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------|---------------------------------------|---------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------|

| Pin Name        | 28-pin<br>QFN               | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                        | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                                     |

| PMA0            | 7                           | 10                                          | 8                                     | 3                               | I/O         | TTL/ST               | Parallel Master Port Address bit 0 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA1            | 9                           | 12                                          | 10                                    | 2                               | I/O         | TTL/ST               | Parallel Master Port Address bit 1 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA2            |                             | _                                           |                                       | 27                              | 0           | —                    | Parallel Master Port address                                                                    |

| PMA3            |                             | _                                           | _                                     | 38                              | 0           | _                    | (Demultiplexed Master modes)                                                                    |

| PMA4            |                             | _                                           | _                                     | 37                              | 0           | _                    | 7                                                                                               |

| PMA5            |                             | _                                           | _                                     | 4                               | 0           | _                    |                                                                                                 |

| PMA6            |                             | _                                           | _                                     | 5                               | 0           | _                    | -                                                                                               |

| PMA7            |                             | _                                           | _                                     | 13                              | 0           | _                    | -                                                                                               |

| PMA8            |                             | _                                           | _                                     | 32                              | 0           | _                    | -                                                                                               |

| PMA9            |                             | _                                           | _                                     | 35                              | 0           | _                    | -                                                                                               |

| PMA10           |                             |                                             | _                                     | 12                              | 0           |                      | -                                                                                               |

| PMCS1           | 23                          | 26                                          | 29                                    | 15                              | 0           |                      | Parallel Master Port Chip Select 1 strob                                                        |

|                 | 20 <sup>(2)</sup>           | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup>                     | 10 <sup>(2)</sup>               | -           |                      | Parallel Master Port data (Demultiplexed                                                        |

| PMD0            | 1 <sup>(3)</sup>            | <br>4 <sup>(3)</sup>                        | 35 <sup>(3)</sup>                     | 21 <sup>(3)</sup>               | I/O         | TTL/ST               | Master mode) or address/data                                                                    |

|                 | 19(2)                       | 22(2)                                       | 25(2)                                 | <u>9</u> (2)                    |             |                      | (Multiplexed Master modes)                                                                      |

| PMD1            | 2(3)                        | 5 <sup>(3)</sup>                            | 36 <sup>(3)</sup>                     | 22 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

|                 | 18(2)                       | 21 <sup>(2)</sup>                           | 24 <sup>(2)</sup>                     | 8 <sup>(2)</sup>                |             |                      | -                                                                                               |

| PMD2            | <u></u>                     | 6 <sup>(3)</sup>                            | 1 <sup>(3)</sup>                      | 23(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD3            | 15                          | 18                                          | 19                                    | 1                               | I/O         | TTL/ST               | -                                                                                               |

| PMD4            | 10                          | 10                                          | 18                                    | 44                              | 1/O         | TTL/ST               | -                                                                                               |

| PMD5            | 13                          | 16                                          | 17                                    | 43                              | I/O         | TTL/ST               | -                                                                                               |

| PMD5<br>PMD6    | 13<br>12 <sup>(2)</sup>     | 15 <sup>(2)</sup>                           | 16 <sup>(2)</sup>                     | 43<br>42 <sup>(2)</sup>         | 1/0         | 111/31               | -                                                                                               |

| FIVIDO          | 28(3)                       | 3( <b>3</b> )                               | 34 <b>(3)</b>                         | 20(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD7            | <u>11(2)</u>                | 14(2)                                       | 15 <sup>(2)</sup>                     | 41 <sup>(2)</sup>               |             |                      | -                                                                                               |

| PINDI           | 27 <sup>(3)</sup>           | 2 <sup>(3)</sup>                            | 33( <b>3</b> )                        | 19 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

| PMRD            | 2/07                        | 24                                          | 27                                    | 19(1)                           | 0           |                      | Derellel Meeter Pert read stroke                                                                |

| PINIRD          | 21<br>22 <sup>(2)</sup>     | 24<br>25 <sup>(2)</sup>                     | 27<br>28 <sup>(2)</sup>               | 14 <sup>(2)</sup>               | 0           |                      | Parallel Master Port read strobe                                                                |

| PMWR            | <u></u><br>4 <sup>(3)</sup> | 25 <sup>(2)</sup><br>7 <sup>(3)</sup>       | 28 <sup>(-)</sup><br>2 <sup>(3)</sup> | 24 <sup>(3)</sup>               | 0           | —                    | Parallel Master Port write strobe                                                               |

| VBUS            | 12(3)                       | 15 <sup>(3)</sup>                           | 16 <sup>(3)</sup>                     | 42(3)                           |             | Analog               | USB bus power monitor                                                                           |

| VBUS<br>VUSB3V3 | 20 <sup>(3)</sup>           | 23(3)                                       | 26 <sup>(3)</sup>                     | 10 <sup>(3)</sup>               | P           | Analog               | USB internal transceiver supply. This pin                                                       |

| VUSBSVS         | 20.7                        | 23.7                                        | 20.7                                  | 10.7                            | Г           | _                    | must be connected to VDD.                                                                       |

| VBUSON          | 22 <sup>(3)</sup>           | 25 <sup>(3)</sup>                           | 28 <sup>(3)</sup>                     | 14 <sup>(3)</sup>               | 0           | _                    | USB Host and OTG bus power control output                                                       |

| D+              | 18 <sup>(3)</sup>           | 21 <sup>(3)</sup>                           | 24 <sup>(3)</sup>                     | 8 <sup>(3)</sup>                | I/O         | Analog               | USB D+                                                                                          |

| –<br>D-         | 19(3)                       | 22 <sup>(3)</sup>                           | 25 <sup>(3)</sup>                     | 9 <sup>(3)</sup>                | I/O         | Analog               | USB D-                                                                                          |

| Legend: C       | CMOS = CI<br>ST = Schm      | MOS compa<br>itt Trigger in<br>input buffer | atible input                          | or output                       |             | Analog =<br>O = Outp | Analog input P = Power                                                                          |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

## TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |

|---------------------------|-----------|-----------------|

| Peripheral                | Base      | Offset<br>Start |

| Watchdog Timer            |           | 0x0000          |

| RTCC                      |           | 0x0200          |

| Timer1-5                  |           | 0x0600          |

| Input Capture 1-5         |           | 0x2000          |

| Output Compare 1-5        |           | 0x3000          |

| IC1 and IC2               |           | 0x5000          |

| SPI1 and SPI2             |           | 0x5800          |

| UART1 and UART2           |           | 0x6000          |

| PMP                       |           | 0x7000          |

| ADC                       | 0xBF80    | 0x9000          |

| CVREF                     |           | 0x9800          |

| Comparator                |           | 0xA000          |

| CTMU                      |           | 0xA200          |

| Oscillator                |           | 0xF000          |

| Device and Revision ID    |           | 0xF220          |

| Peripheral Module Disable |           | 0xF240          |

| Flash Controller          |           | 0xF400          |

| Reset                     |           | 0xF600          |

| PPS                       |           | 0xFA04          |

| Interrupts                |           | 0x1000          |

| Bus Matrix                |           | 0x2000          |

| DMA                       | 0xBF88    | 0x3000          |

| USB                       |           | 0x5050          |

| PORTA-PORTC               |           | 0x6000          |

| Configuration             | 0xBFC0    | 0x0BF0          |

## 4.2 Bus Matrix Control Registers

## TABLE 4-2: BUS MATRIX REGISTER MAP

| ess (                       |                         | a         |                     |       |       |       |       |       |      |      |      | Bits         |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|---------------------|-------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15               | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | —                   | _     | _     | _     | -     | _     | _    | _    |      | —            | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | BINIXCON                | 15:0      |                     |       | _     | _     |       | -     |      | _    |      | BMXWSDRM     | _    | _         | -         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | —                   | _     | _     | _     | _     | _     | _    | _    |      | —            | _    | —         | _         | _         | _          | —        | 0000          |

| 2010                        | DIVIAUNEDA              | 15:0      | 15:0 BMXDKPBA<15:0> |       |       |       |       |       |      | 0000 |      |              |      |           |           |           |            |          |               |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _                   | _     | _     |       | _     | —     | _    | _    | _    | —            | _    | —         | _         | _         | _          | _        | 0000          |

|                             |                         | 15:0      | BMXDUDBA<15:0> 0000 |       |       |       |       |       |      |      | 0000 |              |      |           |           |           |            |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | —                   | —     | —     |       | —     | —     | —    | —    | —    | —            | —    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |                     |       |       |       |       |       |      |      | BN   | IXDUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |                     |       |       |       |       |       |      |      | BM   | XDRMSZ<31:0  | >    |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |                     |       |       | 1     |       |       |      | 1    |      |              |      | 1         |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —                   | —     | —     |       | —     | -     | —    | _    | —    | _            | —    | —         |           | BMXPUPBA  | <19:16>    |          | 0000          |

|                             |                         | 15:0      |                     |       |       |       |       |       |      |      | BN   | IXPUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |                     |       |       |       |       |       |      |      | BM   | IXPFMSZ<31:0 | >    |           |           |           |            |          | xxxx          |

| 2000                        | 2                       | 15:0      |                     |       |       |       |       |       |      |      | xxxx |              |      |           |           |           |            |          |               |

| 2070                        | BMXBOOTSZ               | 31:16     |                     |       |       |       |       |       |      |      | BM   | XBOOTSZ<31:0 | )>   |           |           |           |            |          | 0000          |

|                             | # (20010E               | 15:0      |                     |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          | 0C00          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | NVMDATA<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

## REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |

| Legend:           |                  |                                        |                    |  |  |

|-------------------|------------------|----------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |  |  |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

- bit 18-16 **PLLMULT<2:0>:** Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 = Clock is multiplied by 17

- 001 = Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (OSCCON<26:24>)

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x):

Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = The USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 =The USB PLL module is out of lock or USB PLL module start-up timer is in progress or the USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = The PLL module is in lock or PLL module start-up timer is satisfied

- 0 = The PLL module is out of lock, the PLL start-up timer is running, or the PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = The device will enter Sleep mode when a WAIT instruction is executed

- 0 = The device will enter Idle mode when a WAIT instruction is executed

- **Note 1:** This bit is only available on PIC32MX2XX devices.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |  |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

## REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

#### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | -                 | -                 | _                 | _                 | -                | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

## REGISTER 15-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

## Legend:

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit |                  |

|--------------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = unkn | own)             | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                    |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                                                           |

|           | <ul> <li>1 = Halt in Idle mode</li> <li>0 = Continue to operate in Idle mode</li> </ul>                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                                               |

|           | 1 = Capture rising edge first                                                                                                                                                            |

|           | 0 = Capture falling edge first                                                                                                                                                           |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                                                           |

|           | 1 = 32-bit timer resource capture                                                                                                                                                        |

|           | 0 = 16-bit timer resource capture                                                                                                                                                        |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                                                    |

|           | 0 = Timer3 is the counter source for capture                                                                                                                                             |

|           | 1 = Timer2 is the counter source for capture                                                                                                                                             |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                    |

|           | 01 = Interrupt on every second capture event                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                    |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                 |

|           | 1 = Input capture overflow has occurred                                                                                                                                                  |

|           | 0 = No input capture overflow has occurred                                                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                                             |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                        |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

|           | STOCEN Gyole infinediately following the instruction that deals the module's ON bit.                                                                                                     |

## 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | _                 | _                 | -                 | _                 | -                | —                |

| 45.0         | R-0               | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 20-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HSC = Set by Hardware; Cleared by Software |                                    |                    |  |  |  |

|-------------------|--------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24             |                   | YEAR1             | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |  |

| 00.40             | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16             |                   | —                 | _                 | MONTH10           | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0              | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8              |                   |                   | DAY10             | )<1:0>            | DAY01<3:0>        |                   |                  |                  |  |

| 7.0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0               | —                 | —                 | —                 | _                 | —                 | V                 | VDAY01<2:0       | >                |  |

|                   |                   |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                   |                   |                   |                   |                   |                   |                  |                  |  |

| R = Read          | able bit          |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |

| -n = Value at POR |                   |                   | '1' = Bit is se   | ļ ,               |                   |                   | x = Bit is un    | known            |  |

## REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 **YEAR01<3:0>:** Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9 bit 23-21 **Unimplemented:** Read as '0'

bit 20 **MONTH10:** Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            |                     | CREF              | _                 | _                 | CCH              | <1:0>            |

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

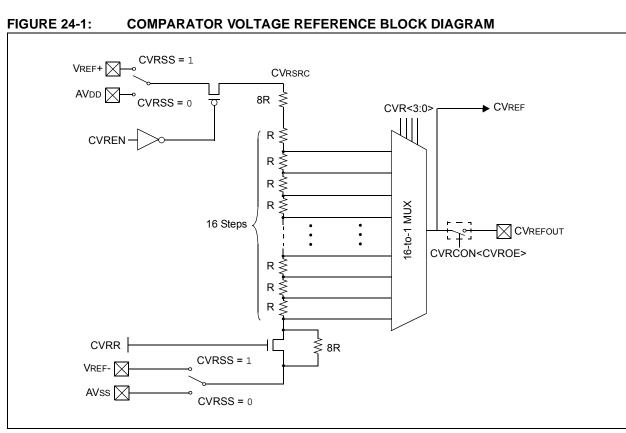

## 24.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- Output can be connected to a pin

A block diagram of the module is shown in Figure 24-1.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

## 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

## 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

| Bit<br>Range | Bit<br>31/23/15/7                                   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 31:24        | VER<3:0> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |

| 00.40        | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup>                         |                   |                   |                   |                      |                   |                  |                  |  |  |

| 45.0         | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 15:8         |                                                     |                   |                   | DEVID<            | 15:8> <sup>(1)</sup> |                   |                  |                  |  |  |

| 7.0          | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 7:0          |                                                     |                   |                   | DEVID             | <7:0>(1)             |                   |                  |                  |  |  |

## REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Legena.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

| DC CHA                                | RACTERIS               | TICS    | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                                      |                                        |  |  |  |  |  |  |  |

|---------------------------------------|------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units                                                                                                                                                                                                                                                                      | Conditions                                           |                                        |  |  |  |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |                                                                                                                                                                                                                                                                            |                                                      |                                        |  |  |  |  |  |  |  |

| DC40k                                 | 44                     | 70      | μA                                                                                                                                                                                                                                                                         | -40°C                                                |                                        |  |  |  |  |  |  |  |

| DC40I                                 | 44                     | 70      | μA                                                                                                                                                                                                                                                                         | +25°C                                                | Base Power-Down Current                |  |  |  |  |  |  |  |

| DC40n                                 | 168                    | 259     | μA                                                                                                                                                                                                                                                                         | +85°C                                                |                                        |  |  |  |  |  |  |  |

| DC40m                                 | 335                    | 536     | μA                                                                                                                                                                                                                                                                         | +105°C                                               |                                        |  |  |  |  |  |  |  |

| Module                                | Differential           | Current |                                                                                                                                                                                                                                                                            |                                                      |                                        |  |  |  |  |  |  |  |

| DC41e                                 | 5                      | 20      | μA                                                                                                                                                                                                                                                                         | 3.6V                                                 | Watchdog Timer Current: AIWDT (Note 3) |  |  |  |  |  |  |  |

| DC42e                                 | 23                     | 50      | μA                                                                                                                                                                                                                                                                         | 3.6V RTCC + Timer1 w/32 kHz Crystal: △IRTCC (Note 3) |                                        |  |  |  |  |  |  |  |

| DC43d                                 | 1000                   | 1100    | μA                                                                                                                                                                                                                                                                         | 3.6V ADC: ΔІАDC (Notes 3,4)                          |                                        |  |  |  |  |  |  |  |

## TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

| DC CHARACTERISTICS |        |                     | $ \begin{array}{ c c c c c } \hline Standard Operating Conditions: 2.3V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature & -40^\circ C \leq TA \leq +85^\circ C \text{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \text{ for V-temp} \\ \hline \end{array} $ |      |      |       |                                                             |

|--------------------|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------|

| Param.             | Symbol | Characteristic      | Min.                                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions                                                  |

| DO10               | Vol    | Output Low Voltage  | _                                                                                                                                                                                                                                                                                                       | _    | 0.4  | V     | $\text{IOL} \leq 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |

|                    |        | Output High Voltage | 1.5(1)                                                                                                                                                                                                                                                                                                  | _    | _    |       | IOH $\geq$ -14 mA, VDD = 3.3V                               |

| DO20               | Vон    | I/O Pins            | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                      | _    | _    | v     | IOH $\geq$ -12 mA, VDD = 3.3V                               |

| D020               | VOH    |                     | 2.4                                                                                                                                                                                                                                                                                                     | _    | _    | v     | IOH $\geq$ -10 mA, VDD = 3.3V                               |

|                    |        |                     | 3.0(1)                                                                                                                                                                                                                                                                                                  | —    | —    |       | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$         |

## TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

## TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |         |      |       |            |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                                                                                                                                       | Min. <sup>(1)</sup> | Typical | Max. | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low <sup>(2)</sup>                                                                                                                                                                                                                             | 2.0                 | —       | 2.3  | V     | _          |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

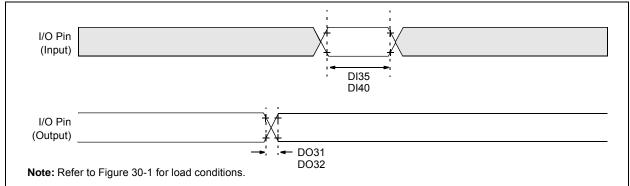

## FIGURE 30-3: I/O TIMING CHARACTERISTICS