Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                       |

| Core Processor            | MIPS32® M4K™                                                                   |

| Core Size                 | 32-Bit Single-Core                                                             |

| Speed                     | 40MHz                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| Number of I/O             | 33                                                                             |

| Program Memory Size       | 256KB (256K x 8)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 16K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 13x10b                                                                     |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| lounting Type             | Surface Mount                                                                  |

| ackage / Case             | 44-VFTLA Exposed Pad                                                           |

| upplier Device Package    | 44-VTLA (6x6)                                                                  |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256d-v-tl |

**TABLE 1-1:** PINOUT I/O DESCRIPTIONS (CONTINUED)

|           |                   | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                   |

|-----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-----------------------------------|

| Pin Name  | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                       |

| OC1       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 1           |

| OC2       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2           |

| OC3       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 3           |

| OC4       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4           |

| OC5       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5           |

| OCFA      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input      |

| OCFB      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input      |

| INT0      | 13                | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0              |

| INT1      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 1              |

| INT2      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 2              |

| INT3      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3              |

| INT4      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4              |

| RA0       | 27                | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1       | 28                | 3                                 | 34                  | 20                              | I/O         | ST             |                                   |

| RA2       | 6                 | 9                                 | 7                   | 30                              | I/O         | ST             |                                   |

| RA3       | 7                 | 10                                | 8                   | 31                              | I/O         | ST             |                                   |

| RA4       | 9                 | 12                                | 10                  | 34                              | I/O         | ST             |                                   |

| RA7       |                   | _                                 | _                   | 13                              | I/O         | ST             |                                   |

| RA8       | _                 | _                                 | _                   | 32                              | I/O         | ST             |                                   |

| RA9       |                   | _                                 | _                   | 35                              | I/O         | ST             |                                   |

| RA10      |                   | _                                 | _                   | 12                              | I/O         | ST             |                                   |

| RB0       | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1       | 2                 | 5                                 | 36                  | 22                              | I/O         | ST             |                                   |

| RB2       | 3                 | 6                                 | 1                   | 23                              | I/O         | ST             |                                   |

| RB3       | 4                 | 7                                 | 2                   | 24                              | I/O         | ST             |                                   |

| RB4       | 8                 | 11                                | 9                   | 33                              | I/O         | ST             | 7                                 |

| RB5       | 11                | 14                                | 15                  | 41                              | I/O         | ST             | 7                                 |

| RB6       | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               | I/O         | ST             |                                   |

| RB7       | 13                | 16                                | 17                  | 43                              | I/O         | ST             |                                   |

| RB8       | 14                | 17                                | 18                  | 44                              | I/O         | ST             | 7                                 |

| RB9       | 15                | 18                                | 19                  | 1                               | I/O         | ST             | 7                                 |

| RB10      | 18                | 21                                | 24                  | 8                               | I/O         | ST             | 7                                 |

| RB11      | 19                | 22                                | 25                  | 9                               | I/O         | ST             | 1                                 |

| RB12      | 20(2)             | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 7                                 |

| RB13      | 21                | 24                                | 27                  | 11                              | I/O         | ST             | 1                                 |

| RB14      | 22                | 25                                | 28                  | 14                              | I/O         | ST             | 7                                 |

| RB15      | 23                | 26                                | 29                  | 15                              | I/O         | ST             | 7                                 |

| Legend: ( |                   | MOS compa                         |                     |                                 |             | Analog =       | Analog input P = Power            |

Analog = Analog input ST = Schmitt Trigger input with CMOS levels

I = Input

TTL = TTL input buffer

O = Output PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

#### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | -                 | _                 |                   |                   | _                | _                |  |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits

This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

- bit 6 CRCAPP: CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 CRCTYP: CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| ▢             |

|---------------|

| DS60001       |

| O             |

| 0             |

| 0             |

| 0             |

| _             |

| $\rightarrow$ |

| 168J-         |

| ω             |

| <u>_</u>      |

| <u> </u>      |

| page          |

| Æ             |

| ×             |

| ťν            |

| _             |

| 135           |

| č             |

| ٠.            |

|               |

|               |

| TABLE 11-5: | PORTC REGISTER MA | 0 |

|-------------|-------------------|---|

| IADLE II-J. | PURIUREGISTER WA  | _ |

| ess                         |                                   |           |       |       |       |       |       |       |          |                       |                         | Bits                    |                         |                       |                      |                         |          |          | 10         |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-------------------------|-------------------------|-----------------------|----------------------|-------------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                    | 21/5                    | 20/4                  | 19/3                 | 18/2                    | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     | ı     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | I        | ı        | 0000       |

| 0200                        | ANSELC                            | 15:0      | -     | _     | _     | _     | _     | _     | _        | -                     | _                       | _                       | _                       | _                     | ANSC3 <sup>(4)</sup> | ANSC2 <sup>(3)</sup>    | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       | _                       | _                       |                       | _                    | _                       | _        | _        | 0000       |

| 0210                        | TRISC                             | 15:0      | I     | _     | _     | _     | _     |       | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup>   | TRISC5 <sup>(3)</sup>   | TRISC4 <sup>(3)</sup> | TRISC3               | TRISC2 <sup>(3)</sup>   | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       |                       |                      |                         |          |          | 0000       |

| 0220                        | PORTC                             | 15:0      | l     | _     | _     | _     | _     | _     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>      | RC5 <sup>(3)</sup>      | RC4 <sup>(3)</sup>    | RC3                  | RC2 <sup>(3)</sup>      | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0230                        | LKI                               | 15:0      | I     | _     | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>    | LATC5 <sup>(3)</sup>    | LATC4 <sup>(3)</sup>  | LATC3                | LATC2 <sup>(3)</sup>    | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0240                        | ODCC                              | 15:0      | _     | _     | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>    | ODCC5 <sup>(3)</sup>    | ODCC4 <sup>(3)</sup>  | ODCC3                | ODCC2 <sup>(3)</sup>    | ODCC1    | ODCC0    | 0000       |

| 6250                        | CNPUC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0250                        | CNPUC                             | 15:0      | I     | _     | _     | _     | _     | _     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup>   | CNPUC5 <sup>(3)</sup>   | CNPUC4 <sup>(3)</sup> | CNPUC3               | CNPUC2 <sup>(3)</sup>   | CNPUC1   | CNPUC0   | 0000       |

| 0000                        | CNIDDO                            | 31:16     | _     | _     | _     | _     | _     | _     | _        | _                     | _                       | _                       | _                       | _                     | _                    | _                       | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | _     | _     | _     | _     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup>   | CNPDC5 <sup>(3)</sup>   | CNPDC4 <sup>(3)</sup> | CNPDC3               | CNPDC2 <sup>(3)</sup>   | CNPDC1   | CNPDC0   | 0000       |

| 6070                        | CNICONIC                          | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 6200                        | CNENC                             | 31:16     | l     | _     | _     | _     | _     | _     | _        |                       | _                       | _                       | _                       |                       | _                    | _                       | _        |          | 0000       |

| 6280                        | CNENC                             | 15:0      | l     | _     | _     | _     | _     | _     | CNIEC9   | CNIEC8 <sup>(3)</sup> | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)               | CNIEC5 <sup>(3)</sup>   | CNIEC4 <sup>(3)</sup> | CNIEC3               | CNIEC2 <sup>(3)</sup>   | CNIEC1   | CNIEC0   | 0000       |

| 6200                        | CNICTATO                          | 31:16     | l     | _     | _     | _     | _     | _     | _        |                       | _                       |                         | _                       |                       | _                    | _                       | _        |          | 0000       |

| 0290                        | CNSTATC                           | 15:0      |       | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6 <sup>(3)</sup> | CNSTATC5 <sup>(3)</sup> | CNSTATC4(3)           | CNSTATC3             | CNSTATC2 <sup>(3)</sup> | CNSTATC1 | CNSTATCO | 0000       |

${f x}$  = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for

- PORTC is not available on 28-pin devices. 2:

- This bit is only available on 44-pin devices.

- This bit is only available on USB-enabled devices with 36 or 44 pins.

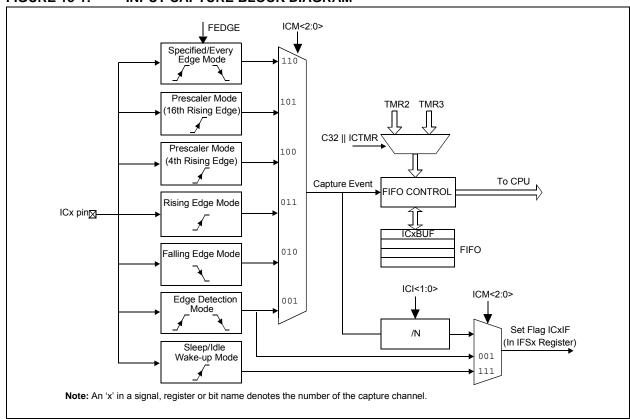

#### 15.0 INPUT CAPTURE

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- · Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

FIGURE 15-1: INPUT CAPTURE BLOCK DIAGRAM

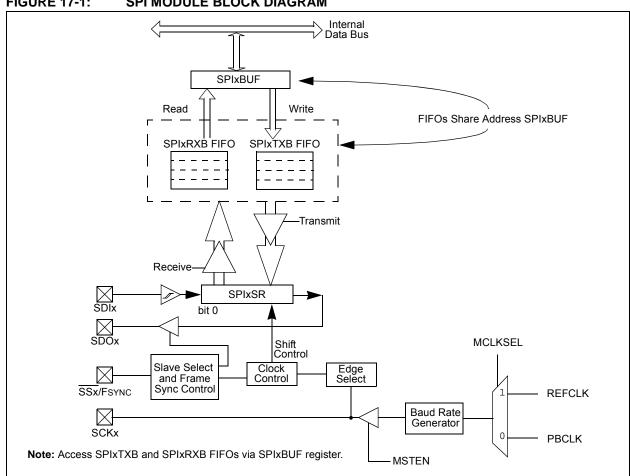

#### SERIAL PERIPHERAL 17.0 **INTERFACE (SPI)**

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial **Peripheral** Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola® SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- Master mode and Slave mode support

- · Four clock formats

- Enhanced Framed SPI protocol support

- · User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- · Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

**FIGURE 17-1:** SPI MODULE BLOCK DIAGRAM

## 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 24.** "InterIntegrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| PIC32IVIA | PIC32WIX1XX/2XX 28/36/44-PIN FAWILY |  |  |  |  |  |  |  |  |

|-----------|-------------------------------------|--|--|--|--|--|--|--|--|

| NOTES:    |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

|           |                                     |  |  |  |  |  |  |  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        |                   | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |

| 22.46        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        | _                 |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | _                 |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 24.24        | U-0                 | U-0                 |

| 31:24        |                   | _                 | _                 | _                 | _                 |                   | _                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | — FORM<2:0>       |                     |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           | _                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

1 = ADC module is operating

0 = ADC module is not operating

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-11 **Unimplemented:** Read as '0'

bit 10-8 FORM<2:0>: Data Output Format bits

111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

000 =Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

111 = Internal counter ends sampling and starts conversion (auto convert)

110 = Reserved

101 = Reserved

100 = Reserved

011 = CTMU ends sampling and starts conversion

010 = Timer 3 period match ends sampling and starts conversion

001 = Active transition on INTO pin ends sampling and starts conversion

000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

### 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- · Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

#### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------------|-------------------|---------------------|-------------------|-----------------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 31:24        |                            | VER<              | 3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup> |                   |                  |                  |  |  |  |

| 22.46        | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 23:16        | DEVID<23:16>(1)            |                   |                     |                   |                             |                   |                  |                  |  |  |  |

| 45.0         | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup> |                   |                     |                   |                             |                   |                  |                  |  |  |  |

| 7.0          | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |  |  |  |

| 7:0          |                            |                   |                     | DEVID<            | <7:0> <sup>(1)</sup>        |                   |                  |                  |  |  |  |

| L | .ea | е | r | ١d | ŀ |

|---|-----|---|---|----|---|

|   |     |   |   |    |   |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 **VER<3:0>:** Revision Identifier bits<sup>(1)</sup> bit 27-0 **DEVID<27:0>:** Device ID bits<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

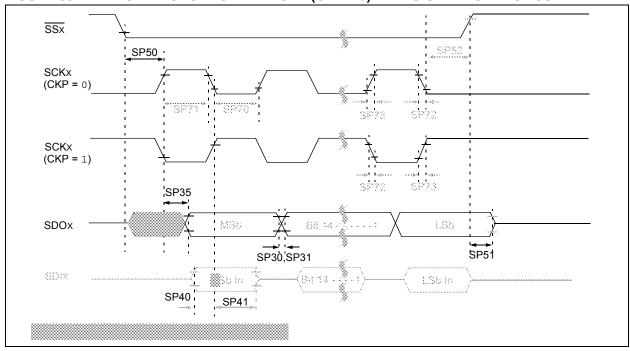

FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS             | TICS                                            | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                     |      |       |                    |  |

|---------------|-----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                  | Min.                                                                                                                                                                                                                                           | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                    | Tsck/2                                                                                                                                                                                                                                         | _                   |      | ns    | _                  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                   | Tsck/2                                                                                                                                                                                                                                         | _                   | _    | ns    | _                  |  |

| SP72          | TscF                  | SCKx Input Fall Time                            | _                                                                                                                                                                                                                                              | _                   | _    | ns    | See parameter DO32 |  |

| SP73          | TscR                  | SCKx Input Rise Time                            | _                                                                                                                                                                                                                                              | _                   |      | ns    | See parameter DO31 |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)             | _                                                                                                                                                                                                                                              | _                   |      | ns    | See parameter DO32 |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)             | _                                                                                                                                                                                                                                              | _                   |      | ns    | See parameter DO31 |  |

| SP35          | TscH2DoV,             | SDOx Data Output Valid after                    | _                                                                                                                                                                                                                                              | _                   | 15   | ns    | VDD > 2.7V         |  |

|               | TscL2doV              | SCKx Edge                                       | _                                                                                                                                                                                                                                              | _                   | 20   | ns    | VDD < 2.7V         |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge      | 10                                                                                                                                                                                                                                             | _                   | _    | ns    | _                  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge       | 10                                                                                                                                                                                                                                             | _                   | _    | ns    | _                  |  |

| SP50          | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx Input                   | 175                                                                                                                                                                                                                                            | _                   | _    | ns    | _                  |  |

| SP51          | TssH2DoZ              | SSx ↑ to SDOx Output<br>High-Impedance (Note 3) | 5                                                                                                                                                                                                                                              | _                   | 25   | ns    | _                  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                             | Tsck + 20                                                                                                                                                                                                                                      | _                   | _    | ns    | _                  |  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.

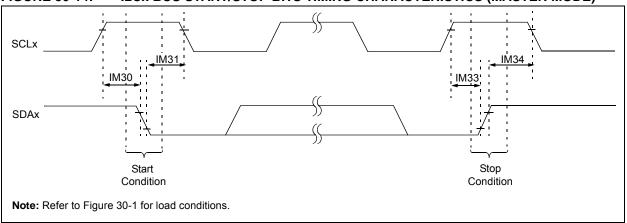

### FIGURE 30-14: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

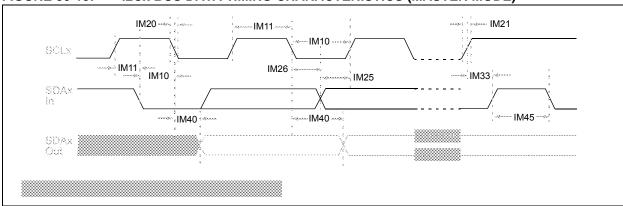

#### FIGURE 30-15: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

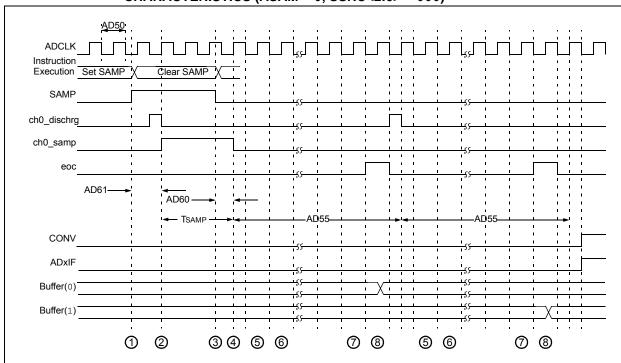

FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

- 1 Software sets ADxCON. SAMP to start sampling.

- ② Sampling starts after discharge period. TSAMP is described in Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual".

- (3) Software clears ADxCON. SAMP to start conversion.

- 4 Sampling ends, conversion sequence starts.

- (5) Convert bit 9.

- 6 Convert bit 8.

- 7 Convert bit 0.

- (8) One TAD for end of conversion.

TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS  |        |                                                    | Standard Operating Conditions (see Note 3):2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |       |      |       |                                  |

|---------------------|--------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----------------------------------|

| Param<br>No.        | Symbol | Characteristic                                     | Min.                                                                                                                                                                                                                                                           | Тур.  | Max. | Units | Conditions                       |

| CTMU CURRENT SOURCE |        |                                                    |                                                                                                                                                                                                                                                                |       |      |       |                                  |

| CTMUI1              | IOUT1  | Base Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                              | 0.55  | _    | μΑ    | CTMUCON<9:8> = 01                |

| CTMUI2              | Іоит2  | 10x Range <sup>(1)</sup>                           | _                                                                                                                                                                                                                                                              | 5.5   | _    | μΑ    | CTMUCON<9:8> = 10                |

| CTMUI3              | Іоит3  | 100x Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                              | 55    | _    | μA    | CTMUCON<9:8> = 11                |

| CTMUI4              | Iout4  | 1000x Range <sup>(1)</sup>                         | _                                                                                                                                                                                                                                                              | 550   | _    | μΑ    | CTMUCON<9:8> = 00                |

| CTMUFV1             | VF     | Temperature Diode Forward Voltage <sup>(1,2)</sup> | _                                                                                                                                                                                                                                                              | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |

|                     |        |                                                    | _                                                                                                                                                                                                                                                              | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |

|                     |        |                                                    | _                                                                                                                                                                                                                                                              | 0.721 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |

| CTMUFV2             | VFVR   | Temperature Diode Rate of Change <sup>(1,2)</sup>  |                                                                                                                                                                                                                                                                | -1.92 |      | mV/ºC | CTMUCON<9:8> = 01                |

|                     |        |                                                    | _                                                                                                                                                                                                                                                              | -1.74 |      | mV/ºC | CTMUCON<9:8> = 10                |

|                     |        |                                                    |                                                                                                                                                                                                                                                                | -1.56 | _    | mV/°C | CTMUCON<9:8> = 11                |

- **Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

- 2: Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

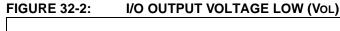

### 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

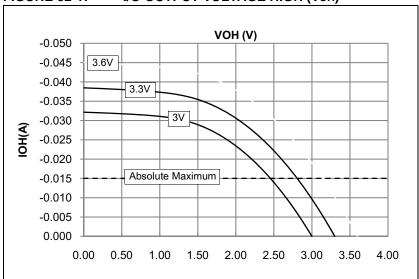

FIGURE 32-1: I/O OUTPUT VOLTAGE HIGH (VOH)

#### 33.0 PACKAGING INFORMATION

### 33.1 Package Marking Information

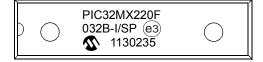

28-Lead SOIC

#### Example

28-Lead SPDIP

#### Example

28-Lead SSOP

#### Example

28-Lead QFN

#### Example

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note:** If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information.

NOTES: