Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256dt-50i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

|                 |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | rals                               |                    |                     |                  |     | _                                     |      | ls)                          |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|---------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l <sup>2</sup> C | PMP | DMA Channels (Programmable/Dedicated) | СТМО | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Y    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F064B | 28   | 64+3                               | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F064C | 36   | 64+3                               | 16               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX130F064D | 44   | 64+3                               | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 13                           | Y    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX150F128B | 28   | 128+3                              | 32               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX150F128C | 36   | 128+3                              | 32               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX150F128D | 44   | 128+3                              | 32               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Y    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F256B | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F256D | 44   | 256+3                              | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX170F256B | 28   | 256+3                              | 64               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX170F256D | 44   | 256+3                              | 64               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

Note 1: This device features 3 KB of boot Flash memory.

**3:** Four out of five external interrupts are remappable.

**<sup>2:</sup>** Four out of five timers are remappable.

**TABLE 1-1:** PINOUT I/O DESCRIPTIONS (CONTINUED)

|           |                   | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                   |

|-----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-----------------------------------|

| Pin Name  | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                       |

| OC1       | PPS               | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1           |

| OC2       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2           |

| OC3       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 3           |

| OC4       | PPS               | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 4           |

| OC5       | PPS               | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5           |

| OCFA      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input      |

| OCFB      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input      |

| INT0      | 13                | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0              |

| INT1      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 1              |

| INT2      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 2              |

| INT3      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3              |

| INT4      | PPS               | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4              |

| RA0       | 27                | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1       | 28                | 3                                 | 34                  | 20                              | I/O         | ST             |                                   |

| RA2       | 6                 | 9                                 | 7                   | 30                              | I/O         | ST             |                                   |

| RA3       | 7                 | 10                                | 8                   | 31                              | I/O         | ST             |                                   |

| RA4       | 9                 | 12                                | 10                  | 34                              | I/O         | ST             |                                   |

| RA7       | _                 | _                                 | _                   | 13                              | I/O         | ST             |                                   |

| RA8       | _                 | _                                 | _                   | 32                              | I/O         | ST             |                                   |

| RA9       | _                 | _                                 | _                   | 35                              | I/O         | ST             |                                   |

| RA10      | _                 | _                                 | _                   | 12                              | I/O         | ST             |                                   |

| RB0       | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1       | 2                 | 5                                 | 36                  | 22                              | I/O         | ST             |                                   |

| RB2       | 3                 | 6                                 | 1                   | 23                              | I/O         | ST             |                                   |

| RB3       | 4                 | 7                                 | 2                   | 24                              | I/O         | ST             |                                   |

| RB4       | 8                 | 11                                | 9                   | 33                              | I/O         | ST             |                                   |

| RB5       | 11                | 14                                | 15                  | 41                              | I/O         | ST             |                                   |

| RB6       | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               | I/O         | ST             |                                   |

| RB7       | 13                | 16                                | 17                  | 43                              | I/O         | ST             |                                   |

| RB8       | 14                | 17                                | 18                  | 44                              | I/O         | ST             | 7                                 |

| RB9       | 15                | 18                                | 19                  | 1                               | I/O         | ST             | 7                                 |

| RB10      | 18                | 21                                | 24                  | 8                               | I/O         | ST             | 7                                 |

| RB11      | 19                | 22                                | 25                  | 9                               | I/O         | ST             | 7                                 |

| RB12      | 20(2)             | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 7                                 |

| RB13      | 21                | 24                                | 27                  | 11                              | I/O         | ST             | 7                                 |

| RB14      | 22                | 25                                | 28                  | 14                              | I/O         | ST             | 7                                 |

| RB15      | 23                | 26                                | 29                  | 15                              | I/O         | ST             | 7                                 |

| Legend: ( |                   | MOS compa                         |                     |                                 |             | Analog =       | Analog input P = Power            |

Analog = Analog input ST = Schmitt Trigger input with CMOS levels

I = Input

TTL = TTL input buffer

O = Output PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

#### 4.0 MEMORY ORGANIZATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to **Section 3.** "**Memory Organization**" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

#### Key features include:

- · 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

# 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)

```

bit 9-8

IS01<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 7-5

Unimplemented: Read as '0'

bit 4-2

IP00<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 1-0

IS00<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

```

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

#### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                   | _                |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHSPTR            | <15:8>            |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | _                 |                   | CHSPTF            | R<7:0>            | _                 |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

:

•

0000000000000000 = Points to byte 1 of the source 000000000000000 = Points to byte 0 of the source

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   | CHDPTR<15:8>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

•

000000000000000 = Points to byte 1 of the destination 000000000000000 = Points to byte 0 of the destination

© 2011-2016 Microchip Technology Inc.

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

111111111111111 = 65,535 bytes transferred on an event

•

0000000000000001= 1 byte transferred on an event

000000000000000 = 65,536 bytes transferred on an event

#### REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHCPTR            | <15:8>            |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCPTR<15:0>: Channel Cell Progress Pointer bits

111111111111111 = 65,535 bytes have been transferred since the last event

•

000000000000000 = 1 byte has been transferred since the last event 000000000000000 = 0 bytes have been transferred since the last event

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

1 = Token packet rejected due to CRC5 error

0 = Token packet accepted **EOFEF:** EOF Error Flag bit<sup>(3,5)</sup>

1 = An EOF error condition was detected0 = No EOF error condition was detected

bit 0 PIDEF: PID Check Failure Flag bit

1 = PID check failed0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 24.24        | U-0                   | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                |

| 23:16        | U-0                   | U-0              |

| 23.10        |                   | _                 | _                 | _                 | _                 | -                 | _                     | _                |

| 15:8         | U-0                   | U-0              |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                     | _                |

|              | R/W-0                 | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup> | PIDEE            |

|              | DISEL             | DIVINEE           | DIVIALE           | DIOEE             | DINOEE            | ONO IDEE          | EOFEE <sup>(2)</sup>  | IIDEE            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

1 = BTSEF interrupt is enabled0 = BTSEF interrupt is disabled

bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

1 = BMXEF interrupt is enabled0 = BMXEF interrupt is disabled

bit 5 DMAEE: DMA Error Interrupt Enable bit

1 = DMAEF interrupt is enabled0 = DMAEF interrupt is disabled

bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

1 = BTOEF interrupt is enabled0 = BTOEF interrupt is disabled

bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

1 = DFN8EF interrupt is enabled0 = DFN8EF interrupt is disabled

bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

1 = CRC16EF interrupt is enabled0 = CRC16EF interrupt is disabled

bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit(1)

1 = CRC5EF interrupt is enabled 0 = CRC5EF interrupt is disabled

**EOFEE:** EOF Error Interrupt Enable bit<sup>(2)</sup>

1 = EOF interrupt is enabled0 = EOF interrupt is disabled

bit 0 PIDEE: PID Check Failure Interrupt Enable bit

1 = PIDEF interrupt is enabled0 = PIDEF interrupt is disabled

Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

#### REGISTER 10-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | 1                 | 1                 | 1                 | -                 | 1                 | 1                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 |                   | -                 | -                 | 1                 | -                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 |                   | _                 | _                 | -                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | BDTPTRI           | H<23:16>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRH<23:16>: Buffer Descriptor Table Base Address bits

This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### REGISTER 10-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | 1                 | _                 | -                 | -                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: Buffer Descriptor Table Base Address bits

This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### 11.3.5 OUTPUT MAPPING

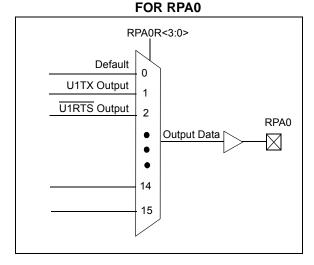

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [pin name]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT

# 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- · Control register lock sequence

- · Configuration bit select lock

#### 11.3.6.1 Control Register Lock Sequence

Under normal operation, writes to the RPnR and [pin name]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, IOLOCK (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6.** "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [pin name]R registers. The Configuration bit, IOL1WAY (DEVCFG3<29>), blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       | (00  |      | its  |      |      |      |      |       |          |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1     | 16/0 | All Resets |

| FA54                        | U1CTSR           | 31:16     | ı     | _     | _     | _     | _     | _     | _    | _    | 1    | _    | _    | _    |      | _     | _        | ı    | 0000       |

| FA54                        | UICISK           | 15:0      | -     | _     | _     |       | -     | _     | _    |      | -    | _    | _    | _    |      | U1CTS | R<3:0>   |      | 0000       |

| FA58                        | U2RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| FASO                        | UZKAK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2RX  | R<3:0>   |      | 0000       |

| FA5C                        | U2CTSR           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FASC                        | UZCISK           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS | R<3:0>   |      | 0000       |

| FA84                        | SDI1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FA04                        | SUIIK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI1F | R<3:0>   |      | 0000       |

| FA88                        | SS1R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FAOO                        | 33 IK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SS1R  | <3:0>    |      | 0000       |

| FA90                        | SDI2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FA90                        | SDIZK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI2F | R<3:0>   |      | 0000       |

| FA94                        | SS2R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FA94                        | 332K             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SS2R  | <3:0>    |      | 0000       |

| EVDo                        | REFCLKIR         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| I ADO                       | NLI OLNIK        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | REFCL | (IR<3:0> |      | 0000       |

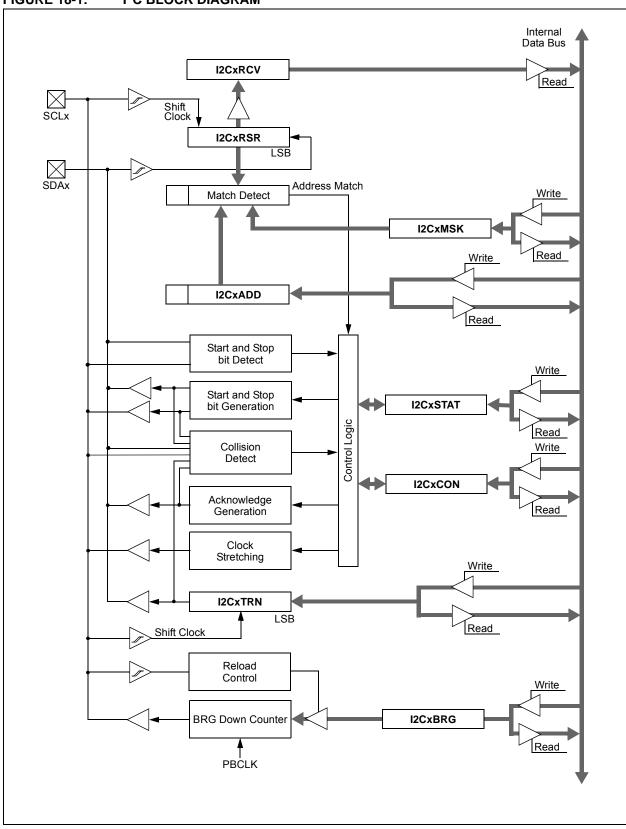

FIGURE 18-1: I<sup>2</sup>C BLOCK DIAGRAM

| PIC32M | X1XX/2X | (X 28/3 | 6/44-PI | NFAM | ILY |  |

|--------|---------|---------|---------|------|-----|--|

| NOTES: |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

|        |         |         |         |      |     |  |

#### REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 |                   |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 | _                 | _                 |                   |                   | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         | VCFG<2:0>         |                   |                   | OFFCAL            | _                 | CSCNA             | _                | _                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              | _                 |                   | SMP               | BUFM              | ALTS              |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

bit 12 OFFCAL: Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

bit 11 Unimplemented: Read as '0'

bit 10 CSCNA: Input Scan Select bit

1 = Scan inputs

0 = Do not scan inputs

bit 9-8 Unimplemented: Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

bit 6 Unimplemented: Read as '0'

bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

•

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

bit 1 BUFM: ADC Result Buffer Mode Select bit

1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

bit 0 ALTS: Alternate Input Sample Mode Select bit

1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

0 = Always use Sample A input multiplexer settings

| PIC32MX1XX/2XX 28/36/44-PIN FAMILY |  |                |                      |                             |                             |

|------------------------------------|--|----------------|----------------------|-----------------------------|-----------------------------|

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  |                |                      |                             |                             |

|                                    |  | 1XX/2XX 28/36/ | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMILY | 1XX/2XX 28/36/44-PIN FAMILY |

#### 30.1 DC Characteristics

TABLE 30-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range     | Max. Frequency                     |  |  |

|----------------|---------------------------|-----------------|------------------------------------|--|--|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)         | PIC32MX1XX/2XX 28/36/44-pin Family |  |  |

| DC5            | 2.3-3.6V                  | -40°C to +85°C  | 40 MHz                             |  |  |

| DC5b           | 2.3-3.6V                  | -40°C to +105°C | 40 MHz                             |  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                         | Symbol              | Min. | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------|---------------------|------|-------------|------|------|

| Industrial Temperature Devices                                                 |                     |      |             |      |      |

| Operating Junction Temperature Range                                           | TJ                  | -40  | _           | +125 | °C   |

| Operating Ambient Temperature Range                                            | TA                  | -40  | _           | +85  | °C   |

| V-temp Temperature Devices                                                     |                     |      |             |      |      |

| Operating Junction Temperature Range                                           | TJ                  | -40  | _           | +140 | °C   |

| Operating Ambient Temperature Range                                            | TA                  | -40  | _           | +105 | °C   |

| Power Dissipation: Internal Chip Power Dissipation: PINT = VDD x (IDD – S IOH) | PD                  |      | PINT + PI/C | )    | W    |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOн} x IOн) + S (VoL x IOL))    |                     |      |             |      |      |

| Maximum Allowed Power Dissipation                                              | PDMAX (TJ – TA)/θJA |      |             |      | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                          | Symbol | Typical | Max. | Unit | Notes |

|------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 28-pin SSOP  | θЈА    | 71      | _    | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θЈА    | 50      |      | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θЈА    | 42      |      | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN   | θЈА    | 35      | _    | °C/W | 1     |

| Package Thermal Resistance, 36-pin VTLA  | θЈА    | 31      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN   | θЈА    | 32      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP  | θЈА    | 45      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin VTLA  | θЈА    | 30      | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                             | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |   |     |       | ≤ Ta ≤ +85°C for Industrial |

|--------------------|--------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------|-----------------------------|

| Param.             | Symbol | Characteristic              | Min. Typ. Max.                                                                                                                                                                                                                                 |   |     | Units | Conditions                  |

| DO10               | VoL    | Output Low Voltage I/O Pins | _                                                                                                                                                                                                                                              | _ | 0.4 | ٧     | IOL ≤ 10 mA, VDD = 3.3V     |

|                    |        | Output High Voltage         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                             |   | _   |       | IOH ≥ -14 mA, VDD = 3.3V    |

| DO20               | Vон    | I/O Pins                    | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                             |   | _   | V     | IOH ≥ -12 mA, VDD = 3.3V    |

| DO20               | VOH    |                             | 2.4                                                                                                                                                                                                                                            | _ | _   | V     | IOH ≥ -10 mA, VDD = 3.3V    |

|                    |        |                             | 3.0(1)                                                                                                                                                                                                                                         | _ | _   |       | IOH ≥ -7 mA, VDD = 3.3V     |

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| TABLE 30-11. ELECTRICAL CHARACTERISTICS. BOX |        |                                                        |                                                                                                                                                                                                                                                |         |      |       |            |

|----------------------------------------------|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| DC CHARACTERISTICS                           |        |                                                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |            |

| Param.<br>No.                                | Symbol | Characteristics                                        | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions |

| BO10                                         | VBOR   | BOR Event on VDD transition high-to-low <sup>(2)</sup> | 2.0                                                                                                                                                                                                                                            | _       | 2.3  | V     | _          |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

#### TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| DC CHARACT                                                     | ERISTICS               |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |  |  |  |

|----------------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                                        |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |      |                                                                                                                                                                         |  |  |  |

| MDC34a                                                         | 8                      | 13   | mA 50 MHz                                                                                                                                                               |  |  |  |

- **Note 1:** The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHAR                           | RACTERIST              | ics     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial |                             |                                                 |  |  |  |

|-----------------------------------|------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max.    | Units                                                                                                                                                                     | Conditions                  |                                                 |  |  |  |

| Power-Down Current (IPD) (Note 1) |                        |         |                                                                                                                                                                           |                             |                                                 |  |  |  |

| MDC40k                            | 10                     | 25      | μА                                                                                                                                                                        | -40°C                       | Base Power-Down Current                         |  |  |  |

| MDC40n                            | 250                    | 500     | μА                                                                                                                                                                        | +85°C                       | Base Power-Down Current                         |  |  |  |

| Module D                          | ifferential (          | Current |                                                                                                                                                                           |                             |                                                 |  |  |  |

| MDC41e                            | 10                     | 55      | μА                                                                                                                                                                        | 3.6V                        | Watchdog Timer Current: ∆IWDT (Note 3)          |  |  |  |

| MDC42e                            | 23                     | 55      | μА                                                                                                                                                                        | 3.6V                        | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |

| MDC43d                            | 1100                   | 1300    | μА                                                                                                                                                                        | 3.6V ADC: ΔΙΑΦΟ (Notes 3,4) |                                                 |  |  |  |

- **Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The Δ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| o order or obtain inion                                                                                                 | nation, e.g., on pricing of delivery, refer to the factory of the fisted sales office.                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Memory Size Pin Count Software Targeting Tape and Reel Flag (if Speed (if applicable) Temperature Range Package | 32-bit RISC MCU with M4K® core,<br>32 KB program memory, 44-pin,                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                         | Flash Memory Family                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Architecture                                                                                                            | $MX = M4K^{\otimes} MCU \text{ core}$                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Product Groups                                                                                                          | 1XX = General purpose microcontroller family 2XX = General purpose microcontroller family                                                                                                                                                                                                                                                                                                                                                                    |

| Flash Memory Family                                                                                                     | F = Flash program memory                                                                                                                                                                                                                                                                                                                                                                                                                                     |