Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                 |

|--------------------------|---------------------------------------------------------------------------------|

| oduct Status             | Active                                                                          |

| ore Processor            | MIPS32® M4K™                                                                    |

| ore Size                 | 32-Bit Single-Core                                                              |

| peed                     | 40MHz                                                                           |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| eripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| umber of I/O             | 33                                                                              |

| ogram Memory Size        | 256KB (256K x 8)                                                                |

| ogram Memory Type        | FLASH                                                                           |

| EPROM Size               | -                                                                               |

| M Size                   | 16K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ta Converters            | A/D 13x10b                                                                      |

| scillator Type           | Internal                                                                        |

| erating Temperature      | -40°C ~ 105°C (TA)                                                              |

| ounting Type             | Surface Mount                                                                   |

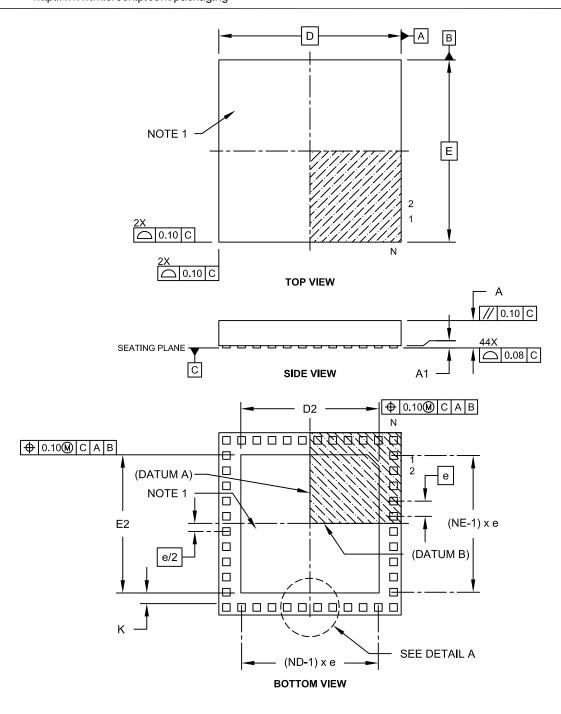

| ckage / Case             | 44-VQFN Exposed Pad                                                             |

| ipplier Device Package   | 44-QFN (8x8)                                                                    |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256dt-v-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R                 | R                                     | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 31:24        |                   | BMXDRMSZ<31:24>                       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 22.40        | R                 | R R R R R R                           |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 23:16        |                   | R   R   R   R   R   R   R   R   R   R |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R                 | R                                     | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 15:8         |                   |                                       |                   | BMXDRI            | MSZ<15:8>         |                   |                  |                  |  |  |  |  |  |

| 7.0          | R                 | R R R R R R                           |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7:0          |                   |                                       |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes:

0x00001000 = Device has 4 KB RAM

0x00002000 = Device has 8 KB RAM

0x00004000 = Device has 16 KB RAM

0x00008000 = Device has 32 KB RAM

0x00010000 = Device has 64 KB RAM

## REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | _                 |                   |                   | _                 | _                | _                |  |  |  |  |

| 00:40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            |                  |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 |                   | BMXPUPE           | 3A<19:16>        |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0 R-0 R-0 R-0   |                   |                  |                  |  |  |  |  |

| 7:0          |                   |                   | PBA<7:0>          |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 BMXPUPBA<10:0>: Read-Only bits

This value is always '0', which forces 2 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 31:24        |                   | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 22:16        | R                 | R R R R R         |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 15:8         |                   |                   |                   | BMXPFN            | MSZ<15:8>         |                   |                  |                  |  |  |  |  |  |

| 7.0          | R R R R R R       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes:

0x00004000 = Device has 16 KB Flash

0x00008000 = Device has 32 KB Flash

0x00010000 = Device has 64 KB Flash

0x00020000 = Device has 128 KB Flash

0x00040000 = Device has 256 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

|              |                   |                   |                   | ` `               |                   |                   |                  |                  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

| 04:04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |

| 31:24        |                   | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 22:40        | R                 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16        |                   | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | BMXBOC            | TSZ<15:8>         |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R                 | R R R R R R       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7:0          | :0 BMXBOOTSZ<7:0> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BMXBOOTSZ<31:0>: Boot Flash Memory (BFM) Size bits

Static value that indicates the size of the Boot PFM in bytes:

0x00000C00 = Device has 3 KB boot Flash

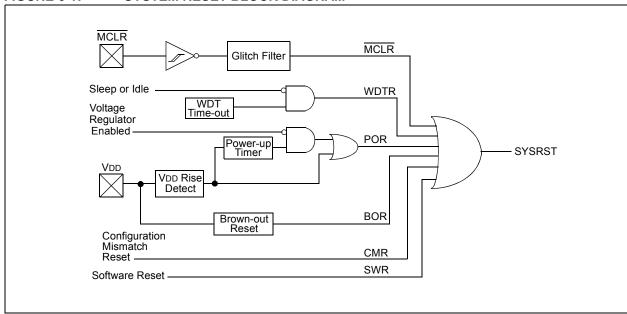

#### 6.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- · Brown-out Reset (BOR)

- · Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

## 8.0 OSCILLATOR CONFIGURATION

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 6. "Oscillator Configuration"** (DS60001112), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- · Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

© 2011-2016 Microchip Technology Inc.

TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bi    | ts       |       |              |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|--------------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4         | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 3200                        | OTTRIVIE                        | 15:0      |       | _     | _     | _     |       | _     |      | _    |       |          |       | FRML<        | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 0200                        | OTTTAMIT                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 02/10                       | OTTOR                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       | PID      | <3:0> |              |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     |       | _     | _     | _     |       | _     |      | _    | _     | _        |       | _            | _      | _      | _         | _        | 0000       |

| 3200                        | 01001                           | 15:0      |       | _     | _     | _     |       | _     |      | _    |       |          |       | CNT<7        | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     |       | _     | _     | _     |       | _     |      | _    | _     | _        |       | _            | _      | _      | _         | _        | 0000       |

| 3200                        | 0100112                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTRE      | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 02D0                        | 0100110                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTRU      | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| OZLO                        | 01014101                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | UTEYE | UOEMON   | _     | USBSIDL      | _      | _      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | ı     | _        | _     | <del>-</del> | _      | _      | ı         | _        | 0000       |

| 0000                        | OTELO                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | LSPD  | RETRYDIS | _     | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 3310                        | O I E I I                       | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 0020                        | 01212                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 0000                        | 01210                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | _        | _     | _            | _      | _      | _         | _        | 0000       |

| 00.0                        |                                 | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        | _     | _            | _      | _      | -         | _        | 0000       |

| 0000                        | 01210                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | -     | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        |       | _            | _      | _      |           | _        | 0000       |

| 3000                        | 0.2.0                           | 15:0      |       | _     | _     | _     | _     | _     |      | _    |       | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        |       | _            | _      | _      |           | _        | 0000       |

| 30.0                        | 0.2.7                           | 15:0      |       | _     | _     | _     |       | _     | _    |      |       | _        |       | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |       | _        | _     | _            | _      | _      | -         | _        | 0000       |

| 3000                        | 01210                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    |       | _        | _     | EPCONDIS     | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined.

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 31:24        | _                 | _                 | _                    | _                    | _                 | _                 | _                      | _                |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0 U-0 U-        |                   | U-0                    | U-0              |  |

| 23.10        |                   | -                 | -                    | -                    |                   | _                 | _                      | _                |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 15.6         |                   |                   | -                    |                      |                   | _                 | _                      | _                |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |

| 7:0          | BTSEE             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |

|              | BTSEF             | DIVIALI           | DIVIALI              | BIOLI                | DINOLI            | CINCTOLI          | EOFEF <sup>(3,5)</sup> | FIDEF            |  |

Legend: WC = Write '1' to clear HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit

1 = Packet rejected due to bit stuff error

0 = Packet accepted

bit 6 BMXEF: Bus Matrix Error Flag bit

1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

0 = No address error

bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup>

1 = USB DMA error condition detected

0 = No DMA error

bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

1 = Bus turnaround time-out has occurred

0 = No bus turnaround time-out

bit 3 **DFN8EF:** Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

bit 2 CRC16EF: CRC16 Failure Flag bit

1 = Data packet rejected due to CRC16 error

0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 11-3: CNCONx: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A, B, C)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 |                   | _                 |                  | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 | _                 | _                | -                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notice (CN) Control ON bit

1 = CN is enabled0 = CN is disabled

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Idle mode halts CN operation0 = Idle does not affect CN operation

bit 12-0 Unimplemented: Read as '0'

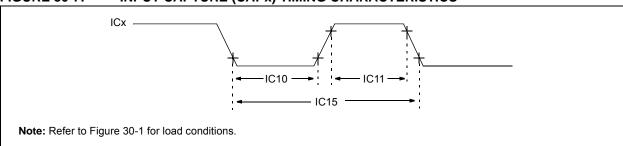

#### REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 22:40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit

-n = Bit Value at POR: ('0', '1', x = unknown) P = Programmable bit r = Reserved bit

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Input Capture Module Enable bit<sup>(1)</sup>

1 = Module is enabled

0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Halt in Idle mode

0 = Continue to operate in Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9 **FEDGE:** First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)

1 = Capture rising edge first0 = Capture falling edge firstC32: 32-bit Capture Select bit

bit 8 **C32:** 32-bit Capture Select bit 1 = 32-bit timer resource capture

0 = 16-bit timer resource capture

bit 7 ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')

0 = Timer3 is the counter source for capture1 = Timer2 is the counter source for capture

bit 6-5 ICI<1:0>: Interrupt Control bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow has occurred0 = No input capture overflow has occurred

bit 3 ICBNE: Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty; at least one more capture value can be read

0 = Input capture buffer is empty

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                    | _                 | _                 | _                |                  |

| 22.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                    | _                 | _                 | -                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

1 = Output Compare peripheral is enabled

0 = Output Compare peripheral is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-6 Unimplemented: Read as '0'

bit 5 OC32: 32-bit Compare Mode bit

1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

1 = PWM Fault condition has occurred (cleared in hardware only)

0 = No PWM Fault condition has occurred

bit 3 OCTSEL: Output Compare Timer Select bit

1 = Timer3 is the clock source for this Output Compare module

0 = Timer2 is the clock source for this Output Compare module

bit 2-0 OCM<2:0>: Output Compare Mode Select bits

111 = PWM mode on OCx; Fault pin enabled

110 = PWM mode on OCx; Fault pin disabled

101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

100 = Initialize OCx pin low; generate single output pulse on OCx pin

011 = Compare event toggles OCx pin

010 = Initialize OCx pin high; compare event forces OCx pin low

001 = Initialize OCx pin low; compare event forces OCx pin high

000 = Output compare peripheral is disabled but continues to draw current

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    |                   | _                 | _                 | _                        | _                 | _                | -                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 15.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extended

bit 14-13 Unimplemented: Read as '0'

bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit underrun generates error events

0 = Transmit underrun does not generate error events

bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error that stops SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit (1)

1 = Audio protocol enabled

0 = Audio protocol disabled

bit 6-5 Unimplemented: Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit (1,2)

11 = PCM/DSP mode

10 = Right-Justified mode

01 = Left-Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

#### REGISTER 17-3: SPIXSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

1 = Transmit buffer, SPIxTXB is empty

0 = Transmit buffer, SPIxTXB is not empty

Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

bit 2 Unimplemented: Read as '0'

bit 1 SPITBF: SPI Transmit Buffer Full Status bit

1 = Transmit not yet started, SPITXB is full

0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

#### Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

bit 0 SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

### 18.1 I2C Control Registers

#### TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |         |        |       |        |                              |       |        | Bi    | ts       |             |            |              |           |      |      |      |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|------------------------------|-------|--------|-------|----------|-------------|------------|--------------|-----------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11                        | 26/10 | 25/9   | 24/8  | 23/7     | 22/6        | 21/5       | 20/4         | 19/3      | 18/2 | 17/1 | 16/0 | All Resets |

| 5000                        | I2C1CON                         | 31:16         |         | _      | _     | _      | _                            | _     | _      | _     |          | _           |            | _            |           | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | ON      |        | SIDL  | SCLREL | STRICT                       | A10M  | DISSLW | SMEN  | GCEN     | STREN       | ACKDT      | ACKEN        | RCEN      | PEN  | RSEN | SEN  | 1000       |

| 5010                        | I2C1STAT                        | 31:16         |         |        |       | _      |                              | _     | -      | -     |          | -           |            | _            | _         | -    | _    |      | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT |       | _      |                              | BCL   | GCSTAT | ADD10 | IWCOL    | I2COV       | D_A        | Р            | S         | R_W  | RBF  | TBF  | 0000       |

| 5020                        | I2C1ADD                         | 31:16         | _       |        |       | _      |                              |       | _      | _     | _        | _           | <u> </u>   | <u> </u>     | _         | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | _       |        |       | _      |                              |       |        |       |          |             | Address    | Register     |           |      |      |      | 0000       |

| 5030                        | I2C1MSK                         | 31:16<br>15:0 |         | _      | _     | _      | _                            | _     | _      | _     | _        | _           |            | —<br>!-D!-t  | _         | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _                            | _     |        |       |          |             | Address Ma | ask Register |           |      |      |      | 0000       |

| 5040                        | I2C1BRG                         | 15:0          | _       |        | _     | _      | Baud Rate Generator Register |       |        |       |          |             |            | _            | 0000      |      |      |      |            |

|                             |                                 | 31:16         | _       | _      |       | _      |                              |       |        |       |          |             |            | _            | 0000      |      |      |      |            |

| 5050                        | I2C1TRN                         | 15:0          | _       |        |       |        |                              | _     |        |       |          | _           |            | Transmit     | Pogister. | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       |        |       | _      |                              |       | _      |       | _        | _           | _          |              | Register  | _    | _    | _    | 0000       |

| 5060                        | I2C1RCV                         | 15:0          | _       |        |       |        |                              |       |        |       | <u> </u> | _           |            | Receive      | Pegister  |      |      |      | 0000       |

|                             |                                 | 31:16         |         |        |       |        |                              |       |        |       |          | _           | _          | TRECEIVE     | —         | _    | _    | _    | 0000       |

| 5100                        | I2C2CON                         | 15:0          | ON      |        | SIDL  | SCLREL | STRICT                       | A10M  | DISSLW | SMEN  | GCEN     | STREN       | ACKDT      | ACKEN        | RCEN      | PEN  | RSEN | SEN  | 1000       |

|                             |                                 | 31:16         |         |        | —     |        | _                            | _     |        | _     | _        | —           | _          |              | _         | _    | _    | _    | 0000       |

| 5110                        | I2C2STAT                        |               | ACKSTAT | TRSTAT |       | _      |                              | BCL   | GCSTAT | ADD10 | IWCOL    | I2COV       | DΑ         | Р            | S         | R W  | RBF  | TBF  | 0000       |

|                             |                                 | 31:16         |         | _      | _     | _      | _                            |       | _      | _     | _        | _           |            | _            | _         |      | _    | _    | 0000       |

| 5120                        | I2C2ADD                         | 15:0          | _       |        |       | _      |                              | _     |        |       |          |             | Address    | Register     |           |      |      |      | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _                            | _     | _      | _     | _        | _           | _          | _            | _         | _    | _    | _    | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _       | _      | _     | _      |                              | _     |        |       |          |             | Address Ma | sk Register  |           |      |      |      | 0000       |

| 5440                        | 1000000                         | 31:16         | _       | 1      | _     | _      | -                            | _     | _      | _     | _        | _           | _          | _            | _         | _    | _    | _    | 0000       |

| 5140                        | I2C2BRG                         | 15:0          | _       |        | _     | _      |                              | •     | •      |       | Bau      | id Rate Ger | erator Reg | ister        |           |      |      |      | 0000       |

| 5150                        | I2C2TRN                         | 31:16         | _       |        |       | _      | ı                            | _     | _      | _     | _        | _           | _          | _            | _         | _    | _    | _    | 0000       |

| 5 150                       | 12021KN                         | 15:0          | _       |        |       | _      |                              |       |        | _     |          |             |            | Transmit     | Register  |      |      |      | 0000       |

| 5160                        | I2C2RCV                         | 31:16         | _       | _      | _     | _      | -                            |       |        |       |          |             | 0000       |              |           |      |      |      |            |

| 3 100                       | IZUZRUV                         | 15:0          | _       | _      | _     | _      | _                            | _     | _      |       |          |             |            | Receive      | Register  |      |      |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                   | _                  | _                 | _                   | _                 | _                | _                |

| 22.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                   | _                  | _                 | _                   | _                 | _                | _                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                   | SIDL               | ADRMU             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7:0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

|              | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> | _                 | WRSP             | RDSP             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

1 = PMP enabled

0 = PMP disabled, no off-chip access performed

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 8 bits are not used

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<10:8> and PMA<14>

00 = Address and data appear on separate pins

bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffer

bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port enabled

0 = PMWR/PMENB port disabled

bit 8 PTRDEN: Read/Write Strobe Port Enable bit

1 = PMRD/PMWR port enabled

0 = PMRD/PMWR port disabled

bit 7-6 CSF<1:0>: Chip Select Function bits(2)

11 = Reserved

10 = PMCS1 functions as Chip Select

01 = PMCS1 functions as PMA<14>

00 = PMCS1 functions as PMA<14>

bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

1 = Active-high (PMALL and PMALH)

0 = Active-low (PMALL and PMALH)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

These bits have no effect when their corresponding pins are used as address lines.

TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                     |                                    | Bits  |       |       |       |       |           |             |           |             | v    |      |      |      |      |      |           |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------|-------|-------|-------|-------|-------|-----------|-------------|-----------|-------------|------|------|------|------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register Reg | ō                                     | 31/15                              | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9      | 24/8        | 23/7      | 22/6        | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 9120                        | ADC1BUFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16                                 |                                    |       |       |       |       |       | ADC Res   | ult Word B  | (ADC1BUF  | B<31·0>)    |      |      |      |      |      |      | 0000      |

| 0120                        | 715015015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15:0                                  |                                    |       |       |       |       |       | 7.50 1.00 | ait Word B  | (7.001001 | D 1011.01 ) |      |      |      |      |      |      | 0000      |

| 0130                        | ADC1BUFC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16                                 |                                    |       |       |       |       |       | ADC Bos   | ult Word C  | (ADC1BLIE | C<31:0>)    |      |      |      |      |      |      | 0000      |

| 9130                        | ADCIBUFC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15:0                                  | ADC Result Word C (ADC1BUFC<31:0>) |       |       |       |       |       |           |             |           |             | 0000 |      |      |      |      |      |           |

| 0140                        | ADC1BUFD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16 ADC POSITIVE AD (ADCAPUED 1940) |                                    |       |       |       |       |       |           |             | 0000      |             |      |      |      |      |      |      |           |

| 9140                        | ADCIBULD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15:0                                  | ADC Result Word D (ADC1BUFD<31:0>) |       |       |       |       |       |           |             |           | 0000        |      |      |      |      |      |      |           |

| 0150                        | ADC1BUFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31:16                                 |                                    |       |       |       |       |       | ADC Pos   | ult Word E  | (ADC1BLIE | E_31:0\)    |      |      |      |      |      |      | 0000      |