Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

|                           |                                                                                 |

| roduct Status             | Obsolete                                                                        |

| ore Processor             | MIPS32® M4K™                                                                    |

| ore Size                  | 32-Bit Single-Core                                                              |

| peed                      | 40MHz                                                                           |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| eripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| umber of I/O              | 33                                                                              |

| rogram Memory Size        | 256KB (256K x 8)                                                                |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 16K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ata Converters            | A/D 13x10b                                                                      |

| scillator Type            | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

| ounting Type              | Surface Mount                                                                   |

| ackage / Case             | 44-VFTLA Exposed Pad                                                            |

| upplier Device Package    | 44-VTLA (6x6)                                                                   |

| ırchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f256dt-v-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 11: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

44-PIN TQFP (TOP VIEW)(1,2,3,5)

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

1

| Pin # | Full Pin Name                                  |

|-------|------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       |

| 2     | RPC6/PMA1/RC6                                  |

| 3     | RPC7/PMA0/RC7                                  |

| 4     | RPC8/PMA5/RC8                                  |

| 5     | RPC9/CTED7/PMA6/RC9                            |

| 6     | Vss                                            |

| 7     | VCAP                                           |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          |

| 10    | AN12/PMD0/RB12                                 |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 16    | AVss                                           |

| 17    | AVDD                                           |

| 18    | MCLR                                           |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

| Pin # | Full Pin Name                        |

|-------|--------------------------------------|

| 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 25    | AN6/RPC0/RC0                         |

| 26    | AN7/RPC1/RC1                         |

| 27    | AN8/RPC2/PMA2/RC2                    |

| 28    | VDD                                  |

| 29    | Vss                                  |

| 30    | OSC1/CLKI/RPA2/RA2                   |

| 31    | OSC2/CLKO/RPA3/RA3                   |

| 32    | TDO/RPA8/PMA8/RA8                    |

| 33    | SOSCI/RPB4/RB4                       |

| 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 35    | TDI/RPA9/PMA9/RA9                    |

| 36    | RPC3/RC3                             |

| 37    | RPC4/PMA4/RC4                        |

| 38    | RPC5/PMA3/RC5                        |

| 39    | Vss                                  |

| 40    | VDD                                  |

| 41    | PGED3/RPB5/PMD7/RB5                  |

| 42    | PGEC3/RPB6/PMD6/RB6                  |

| 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- 5: Shaded pins are 5V tolerant.

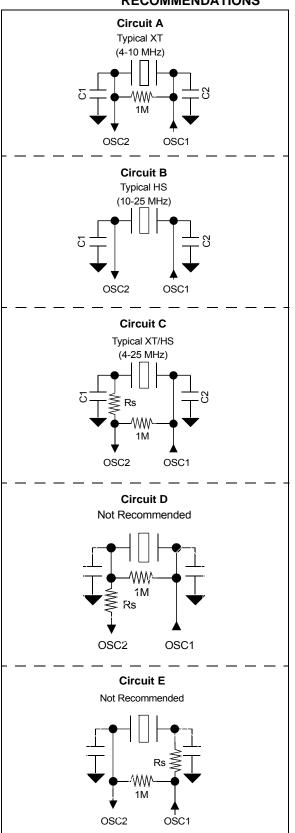

### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32 OSC2 Pin Capacitance = ~4-5 pF

- COUT = PIC32 OSC1 Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

```

Crystal manufacturer recommended: CI = C2 = 15 pF

Therefore:

CLOAD = \{([CIN + CI]^*[COUT + C2]) / [CIN + CI + C2 + COUT]\} + estimated oscillator PCB stray capacitance

= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 pF

= \{([20][20]) / [40]\} + 2.5

= 10 + 2.5 = 12.5 pF

Rounded to the nearest standard value or 12 pF in this example for Primary Oscillator crystals "C1" and "C2".

```

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator.

The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849 "Basic PICmicro® Oscillator Design"

# FIGURE 2-4: PRIMARY CRYSTAL OSCILLATOR CIRCUIT RECOMMENDATIONS

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 $^{\circledR}$  architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

## 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

Note 1: Registers used in exception processing.

2: Registers used during debug.

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.24        | U-0                | U-0                |

| 31:24        | _                 | _                 | -                 | _                 | _                 |                   | _                  | _                  |

| 22.46        | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                  | _                  |

| 45.0         | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

**Legend:** HS = Set by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-10 Unimplemented: Read as '0'

bit 9 **CMR:** Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 VREGS: Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is disabled and is off during Sleep mode

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 SWR: Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset as not executed

bit 5 Unimplemented: Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 IDLE: Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

**Note 1:** User software must clear this bit to view next detection.

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0 U-0           |                           | U-0              |  |  |  |  |

| 31.24        |                   |                   | I                       | _                 |                   | 1                 | _                         | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |  |  |

| 23.10        | _                 | _                 | _                       | _                 | _                 |                   | _                         | _                |  |  |  |  |

| 15.0         | U-0               | U-0               | U-0                     | U-0               | U-0               | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |

| 15:8         | _                 | _                 | _                       | _                 | _                 | 9                 | SRIPL<2:0> <sup>(1)</sup> |                  |  |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |

| 7:0          | _                 | _                 | VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                           |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-11 Unimplemented: Read as '0'

bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

111-000 = The priority level of the latest interrupt presented to the CPU

bit 7-6 **Unimplemented:** Read as '0' bit 5-0 **VEC<5:0>:** Interrupt Vector bits<sup>(1)</sup>

11111-00000 = The interrupt vector that is presented to the CPU

Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

|              | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15.6         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7.0          | IPTMR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits

Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

| TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUE) |

|-----------------------------------------------------|

|-----------------------------------------------------|

| sse                         |                                 |               |        |       |       |       | •     |       |      | Bi       | ts           |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|-------|-------|------|----------|--------------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7         | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | _      | _     | _     | _     | ı     | _     |      | _        | ı            | ı      | _      | _      | I      | ı      | _      | ı      | 0000       |

| 3200                        | DCH2CFTR                        | 15:0          |        |       |       |       |       |       |      | CHCPT    | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2200                        | DCH2DAT                         | 31:16         | _      | _     | _     | _     | ı     | _     | -    | _        | -            | ı      | _      | _      | ı      | ı      | _      | ı      | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _      |       | _     | -     | 1     | _     | -    | 1        |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _      |       |       |       |       |       |      |          |              |        |        |        |        | 0000   |        |        |            |

| 32AU                        | DCH3CON                         | 15:0          | CHBUSY |       |       |       |       |       |      |          |              |        |        |        |        |        | 0000   |        |            |

| 32B0                        | DCH3ECON                        | 31:16         | _      | _     | _     | _     | _     | _     | _    | _        |              |        |        |        | Q<7:0> |        |        |        | 00FF       |

| 3200                        | DOI IOLOON                      | 15:0          |        |       |       |       |       |       |      |          |              |        |        |        |        |        | FF00   |        |            |

| 32C0                        | DCH3INT                         | 31:16         | _      | _     | _     | _     | ı     | _     | _    | _        | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | DOTIONAL                        | 15:0          |        |       |       |       |       |       |      |          |              |        |        |        |        |        |        |        |            |

| 32D0                        | DCH3SSA                         | 31:16         |        |       |       |       |       |       |      |          |              |        |        |        |        |        | 0000   |        |            |

|                             |                                 | 15:0          |        | 0000  |       |       |       |       |      |          |              |        |        |        |        |        | +      |        |            |

| 32E0                        | DCH3DSA                         | 31:16<br>15:0 |        |       |       |       |       |       |      | CHDSA    | <31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         |        |       |       |       |       |       |      |          |              |        |        |        |        |        |        |        | 0000       |

| 32F0                        | DCH3SSIZ                        | 15:0          | _      | _     | _     | _     |       | _     |      | CHSSIZ   | ~<br>?<15:0> |        | _      |        |        |        | _      |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _     | _     | _    | —        |              | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3300                        | DCH3DSIZ                        | 15:0          |        |       |       |       |       |       |      | CHDSIZ   | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _     | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3310                        | DCH3SPTR                        | 15:0          |        |       |       |       |       |       |      | CHSPT    | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2000                        | DOLLODDED                       | 31:16         | _      | _     | _     | _     | _     | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3320                        | DCH3DPTR                        | 15:0          |        |       |       |       |       |       |      | CHDPTI   | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2220                        | DCH3CSIZ                        | 31:16         | _      | _     | _     | _     | _     | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3330                        | DCH3C3IZ                        | 15:0          |        |       |       |       |       |       |      | CHCSIZ   | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         |        | _     | _     | _     | _     | _     | _    |          | _            | _      | _      | _      | _      | _      | _      |        | 0000       |

| JJ-0                        | POLIDOL IK                      | 15:0          |        |       |       |       |       |       |      | CHCPTI   | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | _      | _     | _     | _     | -     | _     | _    | _        | 1            | -      | _      | _      | -      | -      | _      | -      | 0000       |

| 0000                        | DONODAI                         | 15:0          | — I    | _     | _     | _     |       | _     |      | <u> </u> |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | -                 | _                 | -                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15.6         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | _                |

| 7:0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

${\tt 1}$  = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

1 = Writes to Timer1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to the Timer1 register in progress

0 = Asynchronous write to Timer1 register is complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10-8 Unimplemented: Read as '0'

bit 7 TGATE: Timer Gated Time Accumulation Enable bit

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 **Unimplemented:** Read as '0'

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

**Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

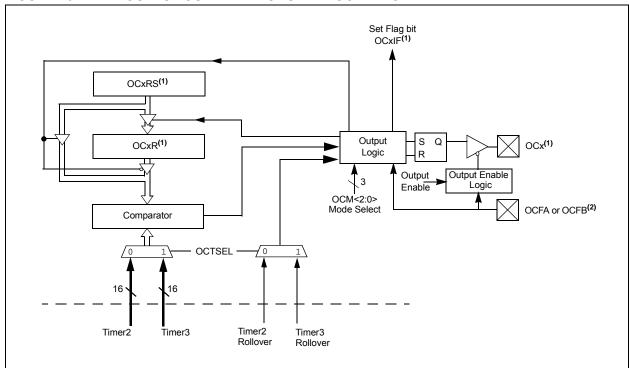

#### 16.0 OUTPUT COMPARE

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- · Single and continuous output pulse generation

- · Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

#### FIGURE 16-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

- **Note 1:** Where 'x' is shown, reference is made to the registers associated with the respective output compare channels, 1 through 5.

- 2: The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

### 16.1 Output Compare Control Registers

### TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |             |       |           |       |       |       |      | Bi    | ts     |      |           |            |        |      |           |      | 9          |

|-----------------------------|---------------------------------|---------------|-------------|-------|-----------|-------|-------|-------|------|-------|--------|------|-----------|------------|--------|------|-----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14 | 29/13     | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5      | 20/4       | 19/3   | 18/2 | 17/1      | 16/0 | All Resets |

|                             | OC1CON                          | 31:16<br>15:0 | ON          |       | —<br>SIDL | _     | _     |       | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL | _    | OCM<2:0>  | _    | 0000       |

| 3010                        | OC1R                            | 31:16<br>15:0 |             |       |           |       |       |       |      | OC1R- | <31:0> |      |           |            |        |      |           |      | xxxx       |

| 3020                        | OC1RS                           | 31:16<br>15:0 | OC1RS<31:0> |       |           |       |       |       |      |       |        |      |           |            |        |      |           | xxxx |            |

| 3200                        | OC2CON                          | 31:16<br>15:0 |             |       |           |       |       |       |      |       |        |      |           |            |        | 0000 |           |      |            |

| 3210                        | OC2R                            | 31:16<br>15:0 | OC2R<31:0>  |       |           |       |       |       |      |       |        |      |           |            |        | xxxx |           |      |            |

| 3220                        | OC2RS                           | 31:16<br>15:0 | OC2RS<31:0> |       |           |       |       |       |      |       |        |      |           |            |        | xxxx |           |      |            |

| 3400                        | OC3CON                          | 31:16<br>15:0 | ON          | _     | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL | _    | OCM<2:0>  | _    | 0000       |

| 3410                        | OC3R                            | 31:16<br>15:0 | O.V         |       | OIDE      |       |       |       |      | OC3R  |        |      | 0002      | 00.21      | 001022 |      | 00M 12.01 |      | xxxx       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |             |       |           |       |       |       |      | OC3RS | <31:0> |      |           |            |        |      |           |      | xxxx       |

| 3600                        | OC4CON                          | 31:16<br>15:0 | ON          | _     | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL | _    | OCM<2:0>  | _    | 0000       |

| 3610                        | OC4R                            | 31:16<br>15:0 | 0.1         |       | 0.52      |       |       |       |      | OC4R  | <31:0> |      | 0002      | 00.2.      | 00.022 |      | 20 2.0    |      | xxxx       |

| 3620                        | OC4RS                           | 31:16<br>15:0 |             |       |           |       |       |       |      | OC4RS | <31:0> |      |           |            |        |      |           |      | xxxx       |

| 3800                        | OC5CON                          | 31:16<br>15:0 | ON          | _     | —<br>SIDL | _     | _     | _     | _    | _     | _      | _    | —<br>OC32 | —<br>OCFLT | OCTSEL | _    | OCM<2:0>  | _    | 0000       |

| 3810                        | OC5R                            | 31:16<br>15:0 |             |       |           |       |       |       |      | OC5R  | <31:0> |      |           |            | ı      |      |           |      | xxxx       |

| 3820                        | OC5RS                           | 31:16<br>15:0 |             |       |           |       |       |       |      | OC5RS | <31:0> |      |           |            |        |      |           |      | xxxx       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### 20.1 PMP Control Registers

#### TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 |           |       |               |       |       |         |              |        | Bi     | ts      |        |           |       |        |      |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|-------|---------|--------------|--------|--------|---------|--------|-----------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11   | 26/10        | 25/9   | 24/8   | 23/7    | 22/6   | 21/5      | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000                        | PMCON                           | 31:16     | _     | _             | ı     | _     | _       | _            | _      | -      | ı       | _      | _         | _     | _      | _    | _     | _     | 0000       |

| 7000                        | FIVICOIN                        | 15:0      | ON    | _             | SIDL  | ADRMU | JX<1:0> | PMPTTL       | PTWREN | PTRDEN | CSF     | <1:0>  | ALP       |       | CS1P   | _    | WRSP  | RDSP  | 0000       |

| 7010                        | PMMODE                          | 31:16     | _     |               | ı     | _     | _       | _            | _      | ı      | I       | _      |           |       | 1      | _    | _     |       | 0000       |

| 7010                        | FIVIIVIODE                      | 15:0      | BUSY  | IRQM          | <1:0> | INCM  | l<1:0>  | _            | MODE   | <1:0>  | WAITE   | 3<1:0> |           | WAITN | Λ<3:0> |      | WAITE | <1:0> | 0000       |

|                             |                                 | 31:16     | _     |               | ı     |       |         |              |        |        |         |        | _         |       | 0000   |      |       |       |            |

| 7020                        | PMADDR                          | 15:0      | _     | CS1<br>ADDR14 | -     | _     | _       | — ADDR<10:0> |        |        |         |        |           |       |        |      |       | 0000  |            |

| 7030                        | PMDOUT                          | 31:16     |       |               |       | •     | •       | •            |        | DATAOU | T<31·0> |        |           |       |        |      |       |       | 0000       |

| 7000                        | 1 MDOO1                         | 15:0      |       |               |       |       |         |              |        | DAIAGO | 1 31.02 |        |           |       |        |      |       |       | 0000       |

| 7040                        | PMDIN                           | 31:16     |       |               |       |       |         |              |        | DATAIN | I<31·0> |        |           |       |        |      |       |       | 0000       |

|                             |                                 | 15:0      |       |               |       |       | •       | •            |        |        |         |        |           |       |        |      |       |       | 0000       |

| 7050                        | PMAEN                           | 31:16     | 6     |               |       |       |         |              |        |        |         |        | 0000      |       |        |      |       |       |            |

| 7000                        | FIVIALIN                        | 15:0      | _     | PTEN14        | -     | _     | _       |              |        |        |         | ı      | PTEN<10:0 | >     |        |      |       |       | 0000       |

| 7060                        | PMSTAT                          | 31:16     | _     | _             | -     | _     | _       | _            | _      | -      | I       | _      | -         | -     | -      | _    | _     | -     | 0000       |

| 7000                        | TIVISTAL                        | 15:0      | IBF   | IBOV          | -     |       | IB3F    | IB2F         | IB1F   | IB0F   | OBE     | OBUF   | _         | _     | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| PIC32M | PIC32MX1XX/2XX 28/36/44-PIN FAMILY |  |  |  |  |  |  |

|--------|------------------------------------|--|--|--|--|--|--|

| NOTES: |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |

| I I C J Z I WI X I Z | 20/30/ | 7-7-1 II <b>V</b> |  |  |

|----------------------|--------|-------------------|--|--|

| NOTES:               |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

#### REGISTER 27-5: CFGCON: CONFIGURATION CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                     | _                      | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | -                 | -                     | _                      | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | _                 | _                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-1             | U-0               | U-1              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            | _                 |                  | TDOEN            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

${\tt 1}$  = Peripheral Pin Select is locked. Writes to PPS registers is not allowed.

0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed.

bit 12 **PMDLOCK:** Peripheral Module Disable bit<sup>(1)</sup>

1 = Peripheral module is locked. Writes to PMD registers is not allowed.

0 = Peripheral module is not locked. Writes to PMD registers is allowed.

bit 11-4 Unimplemented: Read as '0'

bit 3 JTAGEN: JTAG Port Enable bit

1 = Enable the JTAG port

0 = Disable the JTAG port

bit 2-1 Unimplemented: Read as '1'

bit 0 TDOEN: TDO Enable for 2-Wire JTAG bit

1 = 2-wire JTAG protocol uses TDO

0 = 2-wire JTAG protocol does not use TDO

**Note 1:** To change this bit, the unlock sequence must be performed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------|-------------------|---------------------|-------------------|-----------------------------|-------------------|------------------|------------------|

| 04.04        | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |

| 31:24        |                            | VER<              | 3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup> |                   |                  |                  |

| 22.46        | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |

| 23:16        |                            |                   |                     | DEVID<2           | 23:16> <sup>(1)</sup>       |                   |                  |                  |

| 45.0         | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |

| 15:8         | DEVID<15:8> <sup>(1)</sup> |                   |                     |                   |                             |                   |                  |                  |

| 7.0          | R                          | R                 | R                   | R                 | R                           | R                 | R                | R                |

| 7:0          |                            |                   |                     | DEVID<            | <7:0> <sup>(1)</sup>        |                   |                  |                  |

| L | .ea | е | r | 1 | d |  |

|---|-----|---|---|---|---|--|

|   |     |   |   |   |   |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 **VER<3:0>:** Revision Identifier bits<sup>(1)</sup> bit 27-0 **DEVID<27:0>:** Device ID bits<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

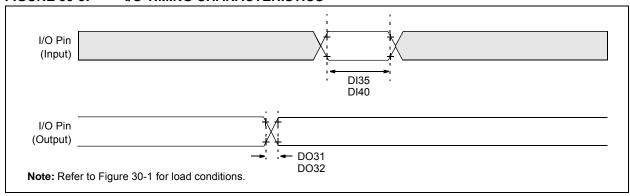

#### FIGURE 30-3: I/O TIMING CHARACTERISTICS

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS             |      |                              | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |                        |      |         |            |  |

|--------------------------------|------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|---------|------------|--|

| Param. No. Symbol Characterist |      |                              | stics <sup>(2)</sup>                                                                                                                                                                                                                           | Min. | Typical <sup>(1)</sup> | Max. | Units   | Conditions |  |

| DO31                           | TioR | Port Output Rise Time        |                                                                                                                                                                                                                                                | 1    | 5                      | 15   | ns      | VDD < 2.5V |  |

|                                |      |                              |                                                                                                                                                                                                                                                | 1    | 5                      | 10   | ns      | VDD > 2.5V |  |

| DO32                           | TioF | Port Output Fall Time        |                                                                                                                                                                                                                                                | 1    | 5                      | 15   | ns      | VDD < 2.5V |  |

|                                |      |                              |                                                                                                                                                                                                                                                | 1    | 5                      | 10   | ns      | VDD > 2.5V |  |

| DI35                           | TINP | INTx Pin High or Low Time    |                                                                                                                                                                                                                                                | 10   | _                      |      | ns      | _          |  |

| DI40                           | TRBP | CNx High or Low Time (input) |                                                                                                                                                                                                                                                | 2    | _                      | _    | Tsysclk | _          |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

**TABLE 30-35: 10-BIT CONVERSION RATE PARAMETERS**

| AC CHARA                          | S <sup>(2)</sup> | Standard Operating Conditions (see Note 3): 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |         |                                |                           |  |

|-----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------|---------------------------|--|

| ADC Speed                         | TAD Min.         | Sampling<br>Time Min.                                                                                                                                                                                                                                       | Rs Max. | VDD ADC Channels Configuration |                           |  |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns            | 132 ns                                                                                                                                                                                                                                                      | 500Ω    | 3.0V to<br>3.6V                | ANX CHX ADC               |  |

| Up to 400 ksps                    | 200 ns           | 200 ns                                                                                                                                                                                                                                                      | 5.0 kΩ  | 2.5V to<br>3.6V                | ANX SHA ADC  ANX OF VREF- |  |

- **Note 1:** External VREF- and VREF+ pins must be used for correct operation.

- 2: These parameters are characterized, but not tested in manufacturing.

- **3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| PIC32WIX1XX/2XX 28/36/44-PIN FAWILY |  |                |                      |                            |                             |  |

|-------------------------------------|--|----------------|----------------------|----------------------------|-----------------------------|--|

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  |                |                      |                            |                             |  |

|                                     |  | 1XX/2XX 28/36/ | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMIL | 1XX/2XX 28/36/44-PIN FAMILY |  |

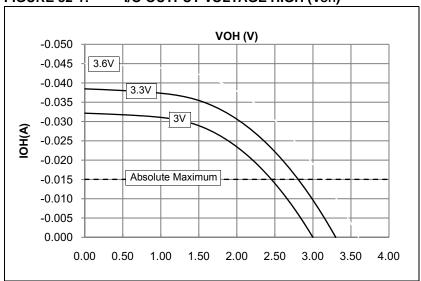

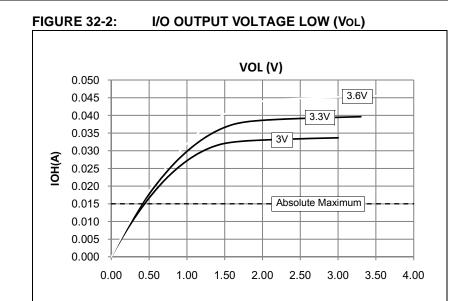

#### 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

FIGURE 32-1: I/O OUTPUT VOLTAGE HIGH (VOH)

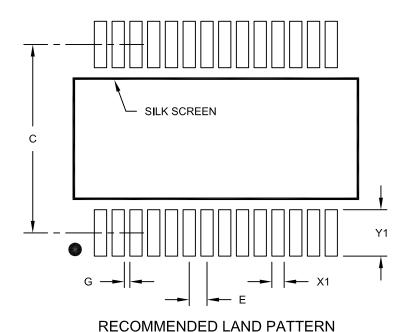

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units MILLIMETERS **Dimension Limits** MIN MOM MAX Contact Pitch 0.65 BSC Ε Contact Pad Spacing С 7.20 Contact Pad Width (X28) X1 0.45 <u>Y1</u> Contact Pad Length (X28) 1.75 G 0.20 Distance Between Pads

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

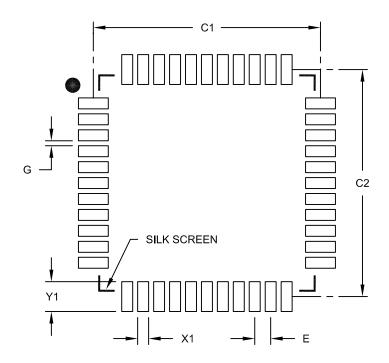

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |       |      |

|--------------------------|-------------|------|-------|------|

| Dimension                | MIN         | NOM  | MAX   |      |

| Contact Pitch            | 0.80 BSC    |      |       |      |

| Contact Pad Spacing      | C1          |      | 11.40 |      |

| Contact Pad Spacing      | C2          |      | 11.40 |      |

| Contact Pad Width (X44)  | X1          |      |       | 0.55 |

| Contact Pad Length (X44) | Y1          |      |       | 1.50 |

| Distance Between Pads    | G           | 0.25 |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B