Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

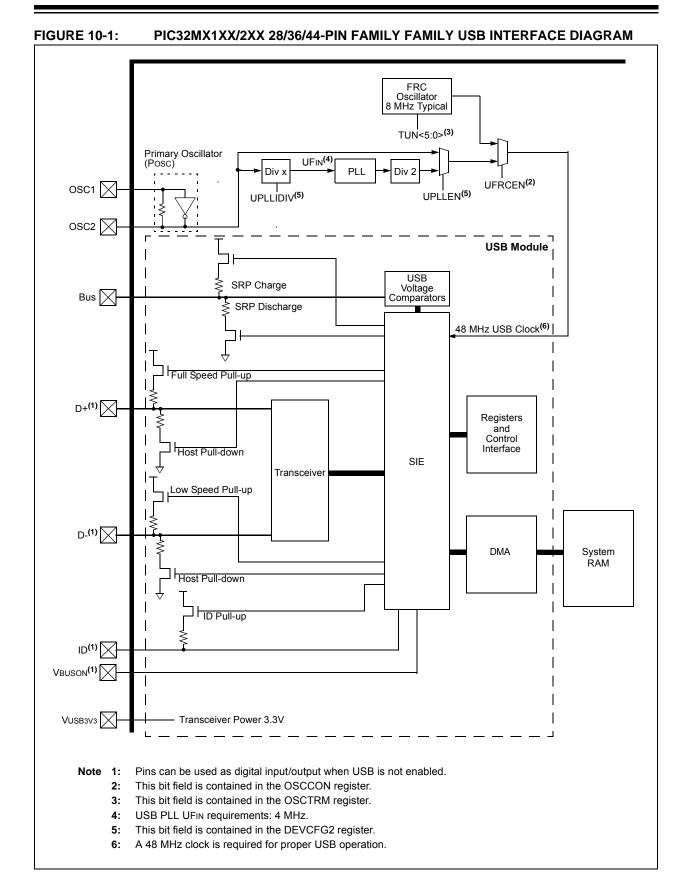

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 19                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128b-50i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

# 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

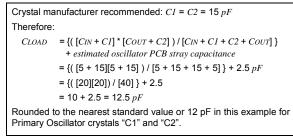

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

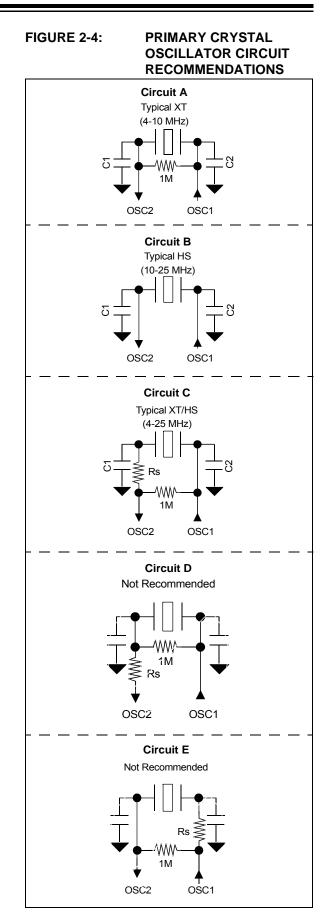

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

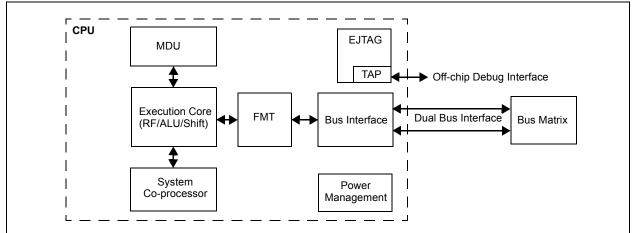

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

## 3.1 Features

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

### FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

## TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | ¢,        |       |       |       |             |             |             |                                                       | Bits   |               |               |              |             |             |       |        |        |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|-------------|-------------|-------------------------------------------------------|--------|---------------|---------------|--------------|-------------|-------------|-------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11       | 26/10       | 25/9                                                  | 24/8   | 23/7          | 22/6          | 21/5         | 20/4        | 19/3        | 18/2  | 17/1   | 16/0   | All<br>Resets |

| 1100                        | 1007                            | 31:16     | _     | —     | —     |             | SPI1IP<2:0> |             | SPI1IP<2:0> SPI1IS<1:0> — — USBIP<2:0> <sup>(2)</sup> |        | :)            | USBIS<1:0>(2) |              | 0000        |             |       |        |        |               |

| 1100                        | 0 IPC7 15:0                     |           | _     | -     | —     | (           | CMP3IP<2:0> |             | CMP3IS                                                | S<1:0> | _             | _             | _            | CI          | MP2IP<2:0>  | •     | CMP2I  | S<1:0> | 0000          |

| 1110                        | IPC8                            | 31:16     | _     | _     | —     |             | PMPIP<2:0>  |             | PMPIS                                                 | S<1:0> | _             | —             | _            | (           | CNIP<2:0>   |       | CNIS   | <1:0>  | 0000          |

| 1110                        | IPCo                            | 15:0      |       | —     | _     | I2C1IP<2:0> |             | I2C1IP<2:0> |                                                       | <1:0>  | —             | —             | _            | I           | J1IP<2:0>   |       | U1IS   | <1:0>  | 0000          |

| 1120                        | IPC9                            | 31:16     |       | —     | _     | (           | CTMUIP<2:0  | >           | CTMUIS<1:0>                                           |        | > I2C2IP<2:0> |               | > I2C2IS<1:0 |             | 6<1:0>      | 0000  |        |        |               |

| 1120                        | IFC9                            | 15:0      | -     | —     | _     |             | U2IP<2:0>   |             | U2IP<2:0>                                             |        | U2IS<1:0>     |               | 2IS<1:0> S   |             | SPI2IP<2:0> |       | SPI2IS | S<1:0> | 0000          |

| 1130                        | IPC10                           | 31:16     | —     | _     | —     | [           | DMA3IP<2:0> | >           | DMA3IS                                                | S<1:0> | _             | —             | _            | DMA2IP<2:0> |             | DMA2I | S<1:0> | 0000   |               |

| 1130                        | IFC IU                          | 15:0      | _     | _     | _     | [           | DMA1IP<2:0> | >           | DMA1IS                                                | S<1:0> | _             | _             | _            | DI          | VA0IP<2:0   | •     | DMA0I  | S<1:0> | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

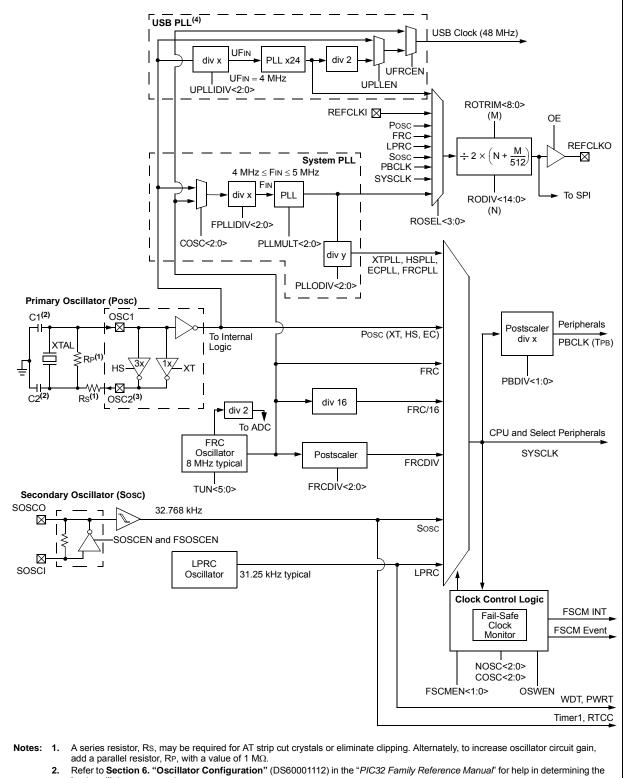

## FIGURE 8-1: OSCILLATOR DIAGRAM

Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determinin best oscillator components.

3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

4. The USB PLL is only available on PIC32MX2XX devices.

|              |                   |                                  | OULEAIO   |                   |          |                       |                  |                  |  |

|--------------|-------------------|----------------------------------|-----------|-------------------|----------|-----------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit<br>30/22/14/6 29/21/13/5 |           | Bit<br>28/20/12/4 |          |                       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0               | U-0                              | R/W-y     | R/W-y             | R/W-y    | R/W-0                 | R/W-0            | R/W-1            |  |

| 31:24        | —                 | —                                | Р         | LLODIV<2:0        | <b>`</b> | FRCDIV<2:0>           |                  |                  |  |

| 00.40        | U-0               | R-0                              | R-1       | R/W-y             | R/W-y    | R/W-y                 | R/W-y            | R/W-y            |  |

| 23:16        | —                 | SOSCRDY                          | PBDIVRDY  | PBDI              | /<1:0>   | Р                     | LLMULT<2:0>      | •                |  |

| 45.0         | U-0               | R-0                              | R-0       | R-0               | U-0      | R/W-y                 | R/W-y            | R/W-y            |  |

| 15:8         | —                 |                                  | COSC<2:0> |                   | —        |                       | NOSC<2:0>        |                  |  |

| 7:0          | R/W-0             | R-0                              | R-0       | R/W-0             | R/W-0    | R/W-0                 | R/W-y            | R/W-0            |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup>             | SLOCK     | SLPEN             | CF       | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | onfiguration bits on POR |                    |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi     | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-30 **Unimplemented:** Read as '0'

### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | _                | —                |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | 5:0> <b>(1)</b>   |                   |                  |                  |

### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|------------------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|--|--|--|--|

|              | U-0 R/W-0         |                              | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | _                 | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                         |                   |                  |                  |  |  |  |  |

|              | R/W-0             | R/W-0                        | R/W-0             | R/W-0             | R/W-0 R/W-0 R/W-0 R/W-0 |                   |                  |                  |  |  |  |  |

| 23:16        |                   | RODIV<7:0>(1,3)              |                   |                   |                         |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | U-0                          | R/W-0             | R/W-0             | R/W-0                   | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |

| 15:8         | ON                | _                            | SIDL              | OE                | RSLP <sup>(2)</sup>     | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |

|              | U-0               | U-0                          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                              |                   |                   |                         | ROSEL             | .<3:0>(1)        |                  |  |  |  |  |

### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          | (0         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | —         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | —     | _     | _     | —     | _     | _    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |       |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —     |       | _     |       |       | _    | _    | _     | —        | _     | —        | —      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | OIBDIF3                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTRI  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        | UTCNI UT                        | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | _     | —     | _     | —    | _    | —     | —        | _     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     |       | —     | —     | —     | —    |      |       | —        | _     | _        | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | —     | _     | —     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | -     | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | _                 | —                 | —                 | _                 | —                 | _                                             | _                |

| 22:16        | U-0                                           | U-0              |

| 23:16        |                   | _                 | —                 | —                 |                   |                   | _                                             |                  |

| 15:0         | U-0                                           | U-0              |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

| •                                                                |

|------------------------------------------------------------------|

| BTSEE: Bit Stuff Error Interrupt Enable bit                      |

| 1 = BTSEF interrupt is enabled                                   |

| 0 = BTSEF interrupt is disabled                                  |

| BMXEE: Bus Matrix Error Interrupt Enable bit                     |

| 1 = BMXEF interrupt is enabled                                   |

| 0 = BMXEF interrupt is disabled                                  |

| DMAEE: DMA Error Interrupt Enable bit                            |

| 1 = DMAEF interrupt is enabled                                   |

| 0 = DMAEF interrupt is disabled                                  |

| <b>BTOEE:</b> Bus Turnaround Time-out Error Interrupt Enable bit |

| 1 = BTOEF interrupt is enabled                                   |

| 0 = BTOEF interrupt is disabled                                  |

| DFN8EE: Data Field Size Error Interrupt Enable bit               |

| 1 = DFN8EF interrupt is enabled                                  |

|                                                                  |

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup> bit 1

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

### TABLE 11-4: PORTB REGISTER MAP

| ess                         |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

|                             |                  | 31:16     | _             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            |              | —            | _            | —            | —            | 0000       |

| 0100                        | ANGLED           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | —             | —             | —            | —            | _            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | -             | _             | _             | 1                            | _             | —             | —            | —            | -            | —                           | -            | -            | —            | -            | _            | _            | 0000       |

| 0110                        | IIKIOD           | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | _             |                              | _             | _             | _            | _            |              | _                           | -            |              |              |              |              |              | 0000       |

| 0120                        | FORTB            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0150                        | LAID             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| C1 4 0                      | 0000             | 31:16     |               | _             | —             | —                            | _             | _             | _            | —            | _            | _                           |              | —            | _            | —            | _            | —            | 0000       |

| 6140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        |                  | 31:16     | -             | —             | —             | -                            | _             | _             | _            | —            | -            | _                           | _            | _            | _            | -            | _            | —            | 0000       |

| 6150                        | CNPUB            | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                        | CNPDB            | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0100                        | CNPDB            | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                        | CNCONB           | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0170                        | CINCOINE         | 15:0      | ON            | _             | SIDL          |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| C400                        |                  | 31:16     |               | —             | —             | -                            | —             | —             | —            | _            |              | —                           | Ι            | -            | —            | -            | —            | _            | 0000       |

| 6180                        | CNENB            | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6(2)                   | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | —             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            | _            | —            | _            | _            | —            | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | _                | _                |  |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 23.10        | —                 | —                 | _                 | —                 | _                 |                   | -                | _                |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 10.0         | 15:8 USERID<15:8> |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

### REGISTER 27-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUSON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDI1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Reserved: Write '1'

- bit 15-0 USERID<15:0>: User ID bits

This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG.

## 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

|               |         |                                                         | Standard Opera<br>stated)                                                                                                                                                                  | ting Condit            | ions: 2.3V | to 3.6V | (unless otherwise                                 |  |  |

|---------------|---------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|---------|---------------------------------------------------|--|--|

|               | ARACTER |                                                         | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |         |                                                   |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                                                                                                                                                                                       | Typical <sup>(1)</sup> | Max.       | Units   | Conditions                                        |  |  |

|               | VIL     | Input Low Voltage                                       |                                                                                                                                                                                            |                        |            |         |                                                   |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                                                                                                                                                                                        | —                      | 0.15 Vdd   | V       |                                                   |  |  |

|               |         | I/O Pins                                                | Vss                                                                                                                                                                                        | —                      | 0.2 Vdd    | V       |                                                   |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss                                                                                                                                                                                        | _                      | 0.3 Vdd    | V       | SMBus disabled<br>(Note 4)                        |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss                                                                                                                                                                                        | —                      | 0.8        | V       | SMBus enabled<br>(Note 4)                         |  |  |

|               | VIH     | Input High Voltage                                      |                                                                                                                                                                                            |                        |            |         |                                                   |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                   | —                      | Vdd        | V       | (Note 4,6)                                        |  |  |

|               |         | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                            | —                      | 5.5        | V       | (Note 4,6)                                        |  |  |

|               |         | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                                                                                                                                                   | —                      | 5.5        | V       |                                                   |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD                                                                                                                                                                                   | _                      | 5.5        | V       | SMBus disabled<br>(Note 4,6)                      |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1                                                                                                                                                                                        | _                      | 5.5        | V       | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |

| DI30          | ICNPU   | Change Notification<br>Pull-up Current                  | _                                                                                                                                                                                          | —                      | -50        | μA      | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _                                                                                                                                                                                          | —                      | -50        | μA      | VDD = 3.3V, VPIN = VDD                            |  |  |

|               | lı∟     | Input Leakage Current<br>(Note 3)                       |                                                                                                                                                                                            |                        |            |         |                                                   |  |  |

| DI50          |         | I/O Ports                                               | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA      | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |

| DI51          |         | Analog Input Pins                                       | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA      | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | —                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA      | $Vss \leq V PIN \leq V DD$                        |  |  |

| DI56          |         | OSC1                                                    | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA      | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |  |

### TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

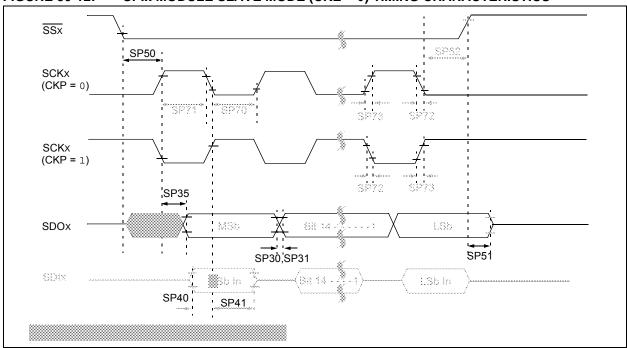

### FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

### TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                    | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |      |       |                    |  |

|--------------------|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                          | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)                                       | TSCK/2                                                                                                                                                                                                        | —                   | _    | ns    | —                  |  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)                                      | TSCK/2                                                                                                                                                                                                        | —                   |      | ns    | —                  |  |

| SP72               | TscF                  | SCKx Input Fall Time                                               | —                                                                                                                                                                                                             | _                   |      | ns    | See parameter DO32 |  |

| SP73               | TscR                  | SCKx Input Rise Time                                               | —                                                                                                                                                                                                             | —                   | _    | ns    | See parameter DO31 |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)                                | —                                                                                                                                                                                                             | —                   |      | ns    | See parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)                                | _                                                                                                                                                                                                             | _                   | _    | ns    | See parameter DO31 |  |

| SP35               | TscH2doV,             | SDOx Data Output Valid after                                       | —                                                                                                                                                                                                             | _                   | 15   | ns    | VDD > 2.7V         |  |

|                    | TscL2DoV              | SCKx Edge                                                          | —                                                                                                                                                                                                             | —                   | 20   | ns    | VDD < 2.7V         |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10                                                                                                                                                                                                            |                     |      | ns    | —                  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                       | 10                                                                                                                                                                                                            | _                   | _    | ns    | —                  |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                           |                     |      | ns    | —                  |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>             | 5                                                                                                                                                                                                             | —                   | 25   | ns    | _                  |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20                                                                                                                                                                                                     | —                   |      | ns    | —                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

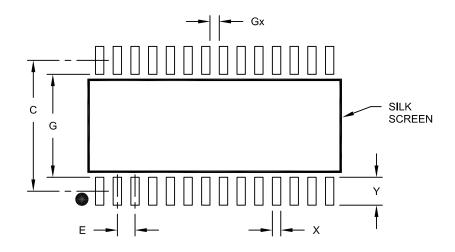

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Ν                | <b>ILLIMETER</b> | S        |      |

|--------------------------|------------------|------------------|----------|------|

| Dimensio                 | Dimension Limits |                  |          | MAX  |

| Contact Pitch            | E                |                  | 1.27 BSC |      |

| Contact Pad Spacing      | С                |                  | 9.40     |      |

| Contact Pad Width (X28)  | X                |                  |          | 0.60 |

| Contact Pad Length (X28) | Y                |                  |          | 2.00 |

| Distance Between Pads    | Gx               | 0.67             |          |      |

| Distance Between Pads    | G                | 7.40             |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

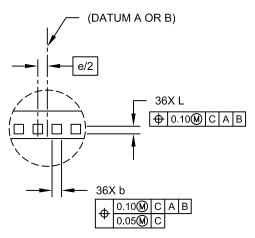

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | N      | <b>IILLIMETER</b> | S        |       |

|-------------------------|--------|-------------------|----------|-------|

| Dimensior               | Limits | MIN               | NOM      | MAX   |

| Number of Pins          | Ν      |                   | 36       |       |

| Number of Pins per Side | ND     |                   | 10       |       |

| Number of Pins per Side | NE     |                   | 8        |       |

| Pitch                   | е      |                   | 0.50 BSC | _     |

| Overall Height          | А      | 0.80              | 0.90     | 1.00  |

| Standoff                | A1     | 0.025             | -        | 0.075 |

| Overall Width           | Е      |                   | 5.00 BSC |       |

| Exposed Pad Width       | E2     | 3.60              | 3.75     | 3.90  |

| Overall Length          | D      |                   | 5.00 BSC |       |

| Exposed Pad Length      | D2     | 3.60              | 3.75     | 3.90  |

| Contact Width           | b      | 0.20              | 0.25     | 0.30  |

| Contact Length          | L      | 0.20              | 0.25     | 0.30  |

| Contact-to-Exposed Pad  | K      | 0.20              | -        | -     |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-187C Sheet 2 of 2

| TABLE A-1: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section                           | Update Description                                                                                                                                    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29.0 "Electrical Characteristics" | Updated the Absolute Maximum Ratings (removed Voltage on VCORE with respect to Vss).                                                                  |

|                                   | Added the SPDIP specification to the Thermal Packaging Characteristics (see Table 29-2).                                                              |

|                                   | Updated the Typical values for parameters DC20-DC24 in the Operating Current (IDD) specification (see Table 29-5).                                    |

|                                   | Updated the Typical values for parameters DC30a-DC34a in the Idle Current (IIDLE) specification (see Table 29-6).                                     |

|                                   | Updated the Typical values for parameters DC40i and DC40n and removed parameter DC40m in the Power-down Current (IPD) specification (see Table 29-7). |

|                                   | Removed parameter D320 (VCORE) from the Internal Voltage Regulator Specifications and updated the Comments (see Table 29-13).                         |

|                                   | Updated the Minimum, Typical, and Maximum values for parameter F20b in the Internal FRC Accuracy specification (see Table 29-17).                     |

|                                   | Removed parameter SY01 (TPWRT) and removed all Conditions from Resets Timing (see Table 29-20).                                                       |

|                                   | Updated all parameters in the CTMU Specifications (see Table 29-39).                                                                                  |

| 31.0 "Packaging Information"      | Added the 28-lead SPDIP package diagram information (see <b>31.1</b> "Package Marking Information" and <b>31.2</b> "Package Details").                |

| "Product Identification System"   | Added the SPDIP (SP) package definition.                                                                                                              |

# Revision C (November 2011)

All major changes are referenced by their respective section in Table A-2.

| TABLE A-2: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                             | Update Description                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|