Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 19                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128b-50i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 9: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

## 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

44

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|                 |                             | OUT I/O D<br>Pin Nui                        |                                       |                         |             | Í                    |                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------|---------------------------------------|-------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------|

| Pin Name        | 28-pin<br>QFN               |                                             |                                       |                         | Description |                      |                                                                                                 |

| PMA0            | 7                           | 10                                          | 8                                     | 3                       | I/O         | TTL/ST               | Parallel Master Port Address bit 0 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA1            | 9                           | 12                                          | 10                                    | 2                       | I/O         | TTL/ST               | Parallel Master Port Address bit 1 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA2            |                             | _                                           |                                       | 27                      | 0           | —                    | Parallel Master Port address                                                                    |

| PMA3            |                             | _                                           | _                                     | 38                      | 0           | _                    | (Demultiplexed Master modes)                                                                    |

| PMA4            |                             | _                                           | _                                     | 37                      | 0           | _                    | 7                                                                                               |

| PMA5            |                             | _                                           | _                                     | 4                       | 0           | _                    |                                                                                                 |

| PMA6            |                             | _                                           | _                                     | 5                       | 0           | _                    | -                                                                                               |

| PMA7            |                             | _                                           | _                                     | 13                      | 0           | _                    | -                                                                                               |

| PMA8            |                             | _                                           | _                                     | 32                      | 0           | _                    | -                                                                                               |

| PMA9            |                             | _                                           | _                                     | 35                      | 0           | _                    | -                                                                                               |

| PMA10           |                             |                                             | _                                     | 12                      | 0           |                      | -                                                                                               |

| PMCS1           | 23                          | 26                                          | 29                                    | 15                      | 0           |                      | Parallel Master Port Chip Select 1 strob                                                        |

|                 | 20 <sup>(2)</sup>           | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup>                     | 10 <sup>(2)</sup>       | -           |                      | Parallel Master Port data (Demultiplexed                                                        |

| PMD0            | 1 <sup>(3)</sup>            | <br>4 <sup>(3)</sup>                        | 35 <sup>(3)</sup>                     | 21 <sup>(3)</sup>       | I/O         | TTL/ST               | Master mode) or address/data                                                                    |

|                 | 19(2)                       | 22(2)                                       | 25(2)                                 | <u>9</u> (2)            |             |                      | (Multiplexed Master modes)                                                                      |

| PMD1            | 2(3)                        | 5 <sup>(3)</sup>                            | 36 <sup>(3)</sup>                     | 22 <sup>(3)</sup>       | I/O         | TTL/ST               |                                                                                                 |

|                 | 18(2)                       | 21 <sup>(2)</sup>                           | 24 <sup>(2)</sup>                     | 8 <sup>(2)</sup>        |             |                      | -                                                                                               |

| PMD2            | <u></u>                     | 6 <sup>(3)</sup>                            | 1 <sup>(3)</sup>                      | 23(3)                   | I/O         | TTL/ST               |                                                                                                 |

| PMD3            | 15                          | 18                                          | 19                                    | 1                       | I/O         | TTL/ST               | -                                                                                               |

| PMD4            | 10                          | 10                                          | 18                                    | 44                      | 1/O         | TTL/ST               | -                                                                                               |

| PMD5            | 13                          | 16                                          | 17                                    | 43                      | I/O         | TTL/ST               | -                                                                                               |

| PMD5<br>PMD6    | 13<br>12 <sup>(2)</sup>     | 15 <sup>(2)</sup>                           | 16 <sup>(2)</sup>                     | 43<br>42 <sup>(2)</sup> | 1/0         | 111/31               | -                                                                                               |

| FIVIDO          | 28(3)                       | 3( <b>3</b> )                               | 34 <b>(3)</b>                         | 20(3)                   | I/O         | TTL/ST               |                                                                                                 |

| PMD7            | <u>11(2)</u>                | 14(2)                                       | 15 <sup>(2)</sup>                     | 41 <sup>(2)</sup>       |             |                      | -                                                                                               |

| PINDI           | 27 <sup>(3)</sup>           | 2 <sup>(3)</sup>                            | 33( <b>3</b> )                        | 19 <sup>(3)</sup>       | I/O         | TTL/ST               |                                                                                                 |

| PMRD            | 2/07                        | 24                                          | 27                                    | 19(1)                   | 0           |                      | Derellel Meeter Pert read stroke                                                                |

| PINIRD          | 21<br>22 <sup>(2)</sup>     | 24<br>25 <sup>(2)</sup>                     | 27<br>28 <sup>(2)</sup>               | 14 <sup>(2)</sup>       | 0           |                      | Parallel Master Port read strobe                                                                |

| PMWR            | <u></u><br>4 <sup>(3)</sup> | 25 <sup>(2)</sup><br>7 <sup>(3)</sup>       | 28 <sup>(-)</sup><br>2 <sup>(3)</sup> | 24 <sup>(3)</sup>       | 0           | —                    | Parallel Master Port write strobe                                                               |

| VBUS            | 12(3)                       | 15 <sup>(3)</sup>                           | 16 <sup>(3)</sup>                     | 42(3)                   |             | Analog               | USB bus power monitor                                                                           |

| VBUS<br>VUSB3V3 | 20 <sup>(3)</sup>           | 23(3)                                       | 26 <sup>(3)</sup>                     | 10 <sup>(3)</sup>       | P           | Analog               | USB internal transceiver supply. This pin                                                       |

| VUSBSVS         | 20.7                        | 23.7                                        | 20.7                                  | 10.7                    | Г           | _                    | must be connected to VDD.                                                                       |

| VBUSON          | 22 <sup>(3)</sup>           | 25 <sup>(3)</sup>                           | 28 <sup>(3)</sup>                     | 14 <sup>(3)</sup>       | 0           | _                    | USB Host and OTG bus power control output                                                       |

| D+              | 18 <sup>(3)</sup>           | 21 <sup>(3)</sup>                           | 24 <sup>(3)</sup>                     | 8 <sup>(3)</sup>        | I/O         | Analog               | USB D+                                                                                          |

| –<br>D-         | 19(3)                       | 22 <sup>(3)</sup>                           | 25 <sup>(3)</sup>                     | 9 <sup>(3)</sup>        | I/O         | Analog               | USB D-                                                                                          |

| Legend: C       | CMOS = CI<br>ST = Schm      | MOS compa<br>itt Trigger in<br>input buffer | atible input                          | or output               |             | Analog =<br>O = Outp | Analog input P = Power                                                                          |

###

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

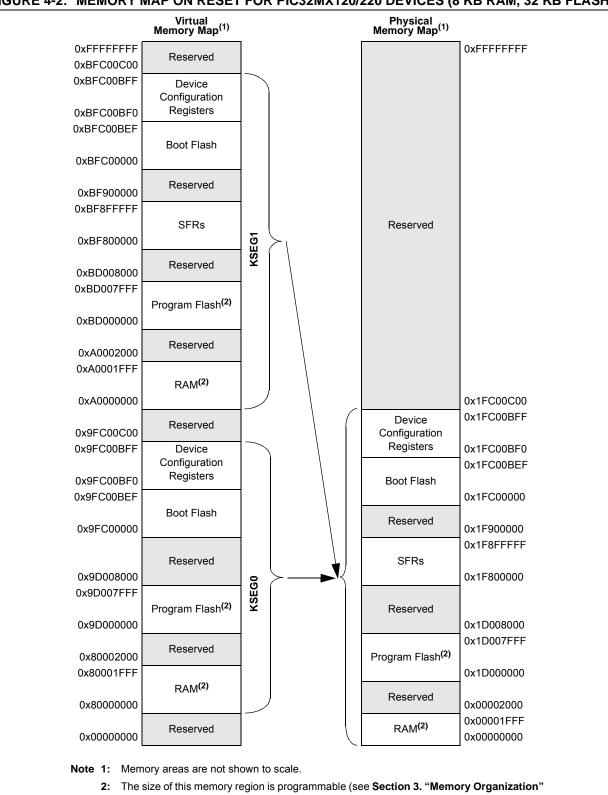

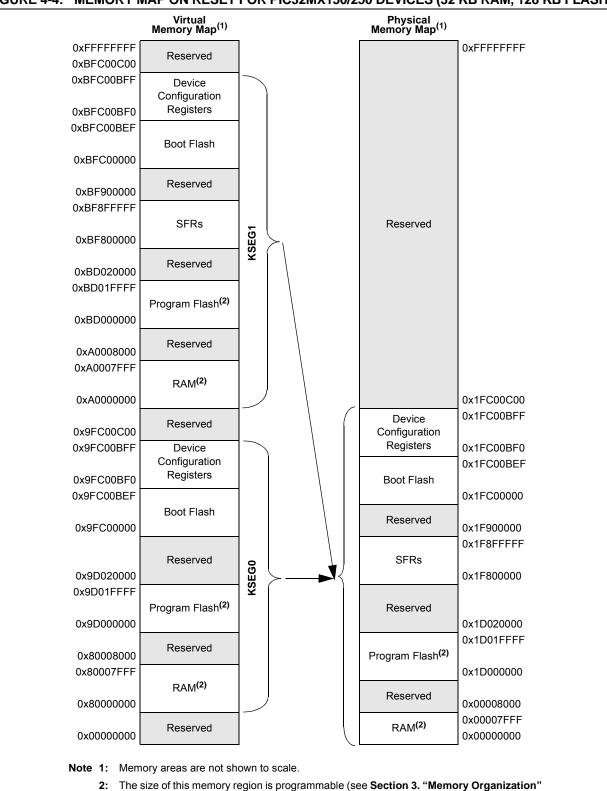

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

## 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

### FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX120/220 DEVICES (8 KB RAM, 32 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|

|              | U-0                         | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                           | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |

|              | R/W-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                              |                   |                   |                     |                   |                  |                  |  |

| 45.0         | R/W-0                       | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |

| 15:8         | ON                          | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |

|              | U-0                         | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                             |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |

### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable HS = Hardware Settable |                          |                    |

|-------------------|------------------------------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit                               | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                               | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

|              |                   |                   |                          |                   | -                     |                       |                  |                      |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31.24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | ISTATE            | SEO               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | DDDDCT           | USBEN <sup>(4)</sup> |

|              | JSTATE            | SE0               | TOKBUSY <sup>(1,5)</sup> | USBRST            | HUSIEN-               | RESUME                | PPBRST           | SOFEN <sup>(5)</sup> |

### REGISTER 10-11: U1CON: USB CONTROL REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

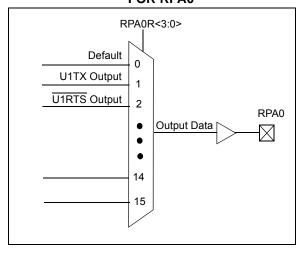

### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

# 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

### 11.3.6.1 Control Register Lock Sequence

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, IOLOCK (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The Configuration bit, IOL1WAY (DEVCFG3<29>), blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | _                 | _                 | -                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 10.0         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | —                 | -                | _                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS             | S<1:0>            |                   | TSYNC             | TCS              |                  |

### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1)</sup>

- 1 = Timer is enabled

- 0 = Timer is disabled

### bit 14 Unimplemented: Read as '0'

### bit 13 **SIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

### bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to Timer1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

### bit 11 **TWIP:** Asynchronous Timer Write in Progress bit

### In Asynchronous Timer mode:

- 1 = Asynchronous write to the Timer1 register in progress

- 0 = Asynchronous write to Timer1 register is complete

- In Synchronous Timer mode:

This bit is read as '0'.

- bit 10-8 **Unimplemented:** Read as '0'

- bit 7 TGATE: Timer Gated Time Accumulation Enable bit

- When TCS = 1:

This bit is ignored.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

### bit 6 Unimplemented: Read as '0'

### bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

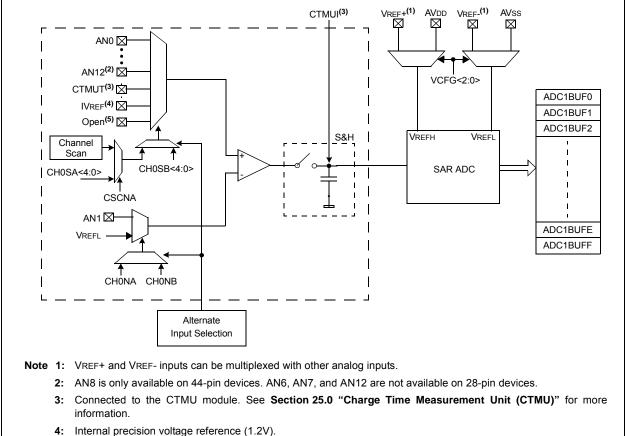

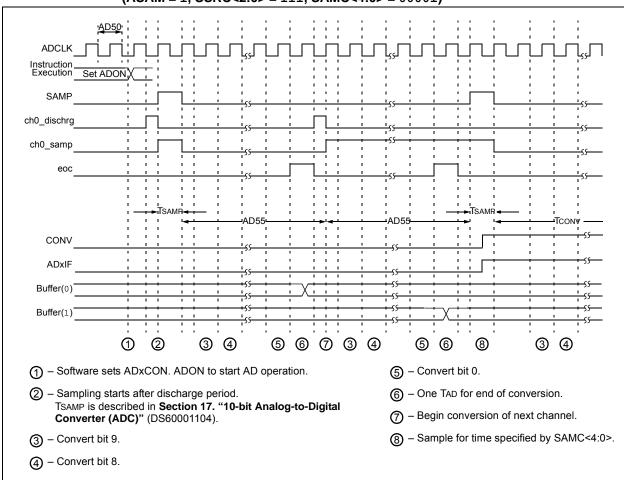

### 22.0 **10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

**FIGURE 22-1:**

- Up to 13 analog input pins

- External voltage reference input pins

- · One unipolar, differential Sample and Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

### 5: This selection is only used with CTMU capacitive and time measurement.

ADC1 MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         | VCFG<2:0>         |                   |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              |                   |                   | SMP               | I<3:0>            |                   | BUFM             | ALTS             |

### REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |  |  |  |

|-----|--------------------|--------------------|--|--|--|

| 000 | AVDD               | AVss               |  |  |  |

| 001 | External VREF+ pin | AVss               |  |  |  |

| 010 | AVdd               | External VREF- pin |  |  |  |

| 011 | External VREF+ pin | External VREF- pin |  |  |  |

| 1xx | AVDD               | AVss               |  |  |  |

### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

### bit 6 Unimplemented: Read as '0'

### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

## 26.0 POWER-SAVING FEATURES

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

## 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

### 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

### 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

### 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

### 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|-----------------------------|-------------------|------------------|------------------|--|

|              | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup> |                   |                  |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                             |                   |                  |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                             |                   |                  |                  |  |

| 7:0          | R                           | R                 | R                   | R                 | R                           | R                 | R                | R                |  |

|              | DEVID<7:0>(1)               |                   |                     |                   |                             |                   |                  |                  |  |

### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Legena.           |                                                                 |                      |                    |

|-------------------|-----------------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | eadable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                                | '0' = Bit is cleared | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

| DC CHARACTERISTICS |        |                                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                         |  |

|--------------------|--------|-----------------------------------------------------------|------------------------------------------------------|---------|------|-------|-----------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                           | Min.                                                 | Typical | Max. | Units | Comments                                                                                |  |

| D300               | VIOFF  | Input Offset Voltage                                      | -                                                    | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |

| D301               | VICM   | Input Common Mode Voltage                                 | 0                                                    | —       | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |

| D302               | CMRR   | Common Mode Rejection Ratio                               | 55                                                   | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |

| D303A              | TRESP  | Large Signal Response Time                                | _                                                    | 150     | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |

| D303B              | TSRESP | Small Signal Response Time                                | -                                                    | 1       | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |

| D304               | ON2ov  | Comparator Enabled to Output<br>Valid                     | —                                                    | _       | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |

| D305               | IVREF  | Internal Voltage Reference                                | 1.14                                                 | 1.2     | 1.26 | V     | —                                                                                       |  |

| D312               | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | —                                                    | —       | 10   | μs    | (Note 3)                                                                                |  |

### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| AC CHARACTERISTICS |                        |                                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |         |       |                                                           |  |

|--------------------|------------------------|----------------------------------------------------------------------|------------------------------------------------------|------------------------|---------|-------|-----------------------------------------------------------|--|

| Param.<br>No.      | Sympol Characteristics |                                                                      | Min.                                                 | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                |  |

| Clock Parameters   |                        |                                                                      |                                                      |                        |         |       |                                                           |  |

| AD50               | TAD                    | ADC Clock Period <sup>(2)</sup>                                      | 65                                                   |                        |         | ns    | See Table 30-35                                           |  |

| Convers            | sion Rate              |                                                                      |                                                      |                        |         |       | ·                                                         |  |

| AD55               | TCONV                  | Conversion Time                                                      | _                                                    | 12 Tad                 | —       | _     | —                                                         |  |

| AD56 FCNV          | FCNV                   | Throughput Rate<br>(Sampling Speed)                                  | —                                                    |                        | 1000    | ksps  | AVDD = 3.0V to 3.6V                                       |  |

|                    |                        |                                                                      | —                                                    | _                      | 400     | ksps  | AVDD = 2.5V to 3.6V                                       |  |

| AD57               | TSAMP                  | Sample Time                                                          | 1 Tad                                                | _                      | —       | _     | TSAMP must be $\geq$ 132 ns                               |  |

| Timing             | Paramete               | rs                                                                   |                                                      |                        |         |       |                                                           |  |

| AD60               | TPCS                   | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               |                                                      | 1.0 Tad                | —       | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |  |

| AD61               | TPSS                   | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 Tad                                              | —                      | 1.5 Tad | _     | _                                                         |  |

| AD62               | TCSS                   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | —                                                    | 0.5 Tad                | —       |       | _                                                         |  |

| AD63               | TDPU                   | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _                                                    | _                      | 2       | μS    | _                                                         |  |

### TABLE 30-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### FIGURE 30-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)