#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128b-i-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4:PIN NAMES FOR 28-PIN USB DEVICES

| 28                                              | PIN SOIC, SPDIP, SSOP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                                                                                                                                                                                                                                                                                   |                                                                |                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | 1<br>SSOP                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                             | 1 28 1 28<br>SOIC SPDIP                                                                                                                                                                                            |

|                                                 | PIC32MX210F016B<br>PIC32MX220F032B<br>PIC32MX230F064B<br>PIC32MX230F256B<br>PIC32MX250F128B<br>PIC32MX270F256B                                                                                                                                                                                                                                                                                                        |                                                                |                                                                                                                                                                                                                    |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |                                                                                                                                                                                                                    |

| Pin #                                           | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                         | Pin #                                                          | Full Pin Name                                                                                                                                                                                                      |

| <b>Pin #</b>                                    | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Pin #</b>                                                   | Full Pin Name                                                                                                                                                                                                      |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |                                                                                                                                                                                                                    |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

|                                                 | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                                                            | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                                                            | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0                                                                                                                                                                                                                                                                                                                                                                             | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1                                                                                                                                                                                                 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2                                                                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss                                                                                   | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2                                                        | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | VCAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2         OSC2/CLKO/RPA3/PMA0/RA3                        | 15<br>16<br>17<br>18<br>19<br>20<br>21<br>21<br>22<br>23<br>24 | VBUS<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED2/RPB10/D+/CTED11/RB10<br>PGEC2/RPB11/D-/RB11<br>VUSB3V3<br>AN11/RPB13/CTPLS/PMRD/RB13 |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2         OSC2/CLKO/RPA3/PMA0/RA3         SOSCI/RPB4/RB4 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | VcAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 10                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                             | AN11/RPB13/CTPLS/PMRD/RB13                                                                                                                                                                                         |

| 11                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                             | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB                                                                                                                                                                     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

|          |                                        | Pin Nu                                | mber <sup>(1)</sup>                    |                                        |             |                |                                                                         |

|----------|----------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC     | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | <sub>11</sub> (3)                      | 14 <sup>(3)</sup>                     | 15 <b>(3)</b>                          | 41 <sup>(3)</sup>                      | I           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                                     | 2                                     | 33                                     | 19                                     | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                                     | 3                                     | 34                                     | 20                                     | I           | ST             | 7                                                                       |

| CTED3    | 13                                     | 16                                    | 17                                     | 43                                     | I           | ST             | 7                                                                       |

| CTED4    | 15                                     | 18                                    | 19                                     | 1                                      | I           | ST             | 7                                                                       |

| CTED5    | 22                                     | 25                                    | 28                                     | 14                                     | I           | ST             | 7                                                                       |

| CTED6    | 23                                     | 26                                    | 29                                     | 15                                     | I           | ST             | 7                                                                       |

| CTED7    | _                                      | _                                     | 20                                     | 5                                      | I           | ST             | 7                                                                       |

| CTED8    | _                                      |                                       | _                                      | 13                                     | I           | ST             | 7                                                                       |

| CTED9    | 9                                      | 12                                    | 10                                     | 34                                     | I           | ST             | 7                                                                       |

| CTED10   | 14                                     | 17                                    | 18                                     | 44                                     | I           | ST             | 7                                                                       |

| CTED11   | 18                                     | 21                                    | 24                                     | 8                                      | I           | ST             | 7                                                                       |

| CTED12   | 2                                      | 5                                     | 36                                     | 22                                     | I           | ST             | 7                                                                       |

| CTED13   | 3                                      | 6                                     | 1                                      | 23                                     | I           | ST             | 7                                                                       |

| CTPLS    | 21                                     | 24                                    | 27                                     | 11                                     | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                                      | 4                                     | 35                                     | 21                                     | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 1        |

| PGEC1    | 2                                      | 5                                     | 36                                     | 22                                     | Ι           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                                     | 21                                    | 24                                     | 8                                      | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 2        |

| PGEC2    | 19                                     | 22                                    | 25                                     | 9                                      | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup><br>27 <sup>(3)</sup> | 14 <sup>(2)</sup><br>2 <sup>(3)</sup> | 15 <sup>(2)</sup><br>33 <sup>(3)</sup> | 41 <sup>(2)</sup><br>19 <sup>(3)</sup> | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 3        |

|          | 12 <b>(2)</b>                          | 15 <b>(2)</b>                         | 16 <b>(2)</b>                          | 42 <sup>(2)</sup>                      |             | OT             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup>                      | 3 <b>(3)</b>                          | 34 <sup>(3)</sup>                      | 20 <sup>(3)</sup>                      |             | ST             | Debugging Communication Channel 3                                       |

| PGED4    | —                                      | —                                     | 3                                      | 12                                     | I/O         | ST             | Data I/O pin for Programming/Debuggir<br>Communication Channel 4        |

| PGEC4    | —                                      | —                                     | 4                                      | 13                                     | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer PPS = Peripheral Pin Select

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**2:** Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

— = N/A

|          |                         | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                      |                                                                                      |  |  |

|----------|-------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------------|--------------------------------------------------------------------------------------|--|--|

| Pin Name | 28-pin<br>QFN           | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                          |  |  |

| MCLR     | 26                      | 1                                 | 32                  | 18                              | I/P         | ST                   | Master Clear (Reset) input. This pin is an active-low Reset to the device.           |  |  |

| AVDD     | 25                      | 28                                | 31                  | 17                              | Р           | _                    | Positive supply for analog modules. This<br>pin must be connected at all times.      |  |  |

| AVss     | 24                      | 27                                | 30                  | 16                              | Р           | —                    | Ground reference for analog modules                                                  |  |  |

| Vdd      | 10                      | 13                                | 5, 13, 14,<br>23    | 28, 40                          | Р           | _                    | Positive supply for peripheral logic and<br>I/O pins                                 |  |  |

| VCAP     | 17                      | 20                                | 22                  | 7                               | Р           | —                    | CPU logic filter capacitor connection                                                |  |  |

| Vss      | 5, 16                   | 8, 19                             | 6, 12, 21           | 6, 29, 39                       | Р           | _                    | Ground reference for logic and I/O pins.<br>This pin must be connected at all times. |  |  |

| VREF+    | 27                      | 2                                 | 33                  | 19                              | I           | Analog               | Analog voltage reference (high) input                                                |  |  |

| VREF-    | 28                      | 3                                 | 34                  | 20                              | I           | Analog               | Analog voltage reference (low) input                                                 |  |  |

| Legend:  | CMOS = CM<br>ST = Schmi |                                   | •                   |                                 |             | Analog =<br>O = Outp | Analog input P = Power<br>ut I = Input                                               |  |  |

#### TADI E 4 4. DINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

| . , .     |

|-----------|

| P = Powe  |

| l = Input |

| — = N/A   |

|           |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

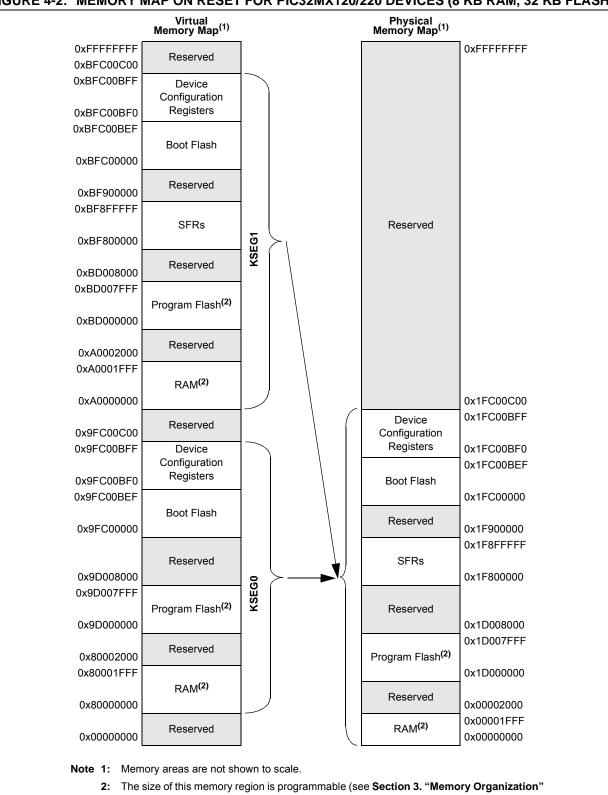

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX120/220 DEVICES (8 KB RAM, 32 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                       | —                 | —                 |                   | _                | —                |  |  |  |  |

| 23:16        | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | _                       | —                 | —                 | _                 | —                | —                |  |  |  |  |

| 45.0         | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | _                       | —                 | _                 | _                 | _                | —                |  |  |  |  |

| 7.0          | U-0 U-0           |                   | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | —                 | _                 | TUN<5:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | —                 | —                 |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

## 11.4 Ports Control Registers

## TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |                          |                       | Bits                    | 6                       |      |      |          |          |          |          |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-----------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                  | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       |      | _    | _        | _        | —        | —        | _        | 0000       |

|                             |                                 | 15:0      | _     | —     | —     | —     | —     | -                        |                       |                         | —                       | _    | _    | —        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | —     | —     | —     | —     | —                        |                       |                         | —                       | _    | _    |          | —        | _        | _        | —        | 0000       |

| 0010                        |                                 | 15:0      | —     | —     | —     | —     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup> | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | —    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | —     | —     | —     | —     | _     | —                        | —                     | _                       | —                       | _    | —    |          |          |          |          |          | 0000       |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | _     | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>    | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | —    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | ) LATA                          | 31:16     | _     | —     | —     | —     | _     |                          | _                     | _                       | —                       | —    | —    | _        | _        | _        |          | _        | 0000       |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | —     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>  | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | —    | —    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | —     | —     | —     | —     | —     | —                        |                       | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0040                        | ODOA                            | 15:0      | —     | —     | —     | —     | —     | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>  | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    | —    | —    | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0030                        | CINFUA                          | 15:0      | _     | _     | —     | —     | _     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup> | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | —    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 6060                        | CNPDA                           | 31:16     | —     | —     | —     | —     |       | _                        |                       |                         |                         | —    | —    |          |          | —        |          |          | 0000       |

| 0000                        | CINFDA                          | 15:0      | _     | _     | —     | —     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup> | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | —    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 6070                        | CNCONA                          | 31:16     | —     | —     | —     | —     |       | _                        |                       | _                       | _                       | —    | —    |          |          | —        |          |          | 0000       |

| 0070                        | CINCONA                         | 15:0      | ON    | —     | SIDL  | —     | _     | _                        | _                     | _                       | —                       | _    | _    | _        | —        | —        | —        | —        | 0000       |

| 6080                        | CNENA                           | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       | _    | —    | —        | _        | _        | _        | _        | 0000       |

| 0000                        | CINEINA                         | 15:0      | _     | _     | —     | —     |       | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup> | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   |      |      | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

| 6000                        | CNISTATA                        | 31:16     | _     | _     | —     | —     |       |                          |                       |                         | _                       |      | _    |          |          | —        | _        |          | 0000       |

| 0090                        | CNSTATA                         | 15:0      | _     | _     | —     | —     |       | CNSTATA10 <sup>(2)</sup> | CNSTATA9(2)           | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> |      |      | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is only available on 44-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

### Legend: