#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 014110                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128b-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.2 Bus Matrix Control Registers

## TABLE 4-2: BUS MATRIX REGISTER MAP

| ess (                       |                         | a         |       |       |       |       |       |       |      |      |      | Bits         |      |           |           |           |            |          |               |

|-----------------------------|-------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | —     | _     | _     | _     | -     | _     | _    | _    |      | —            | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | BINIXCON                | 15:0      |       |       | _     | _     |       | -     |      | _    |      | BMXWSDRM     | _    | _         | -         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    |      | —            | _    | —         | _         | _         | _          | —        | 0000          |

| 2010                        | DIVIAUNEDA              | 15:0      |       |       |       |       |       |       |      |      | BN   | IXDKPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | _     | _     | _     |       | _     | —     | _    | _    | _    | —            | _    | _         | _         | _         | _          | _        | 0000          |

|                             |                         | 15:0      |       |       |       |       |       |       |      |      |      | 0000         |      |           |           |           |            |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | —     | —     | —     |       | —     | —     | —    | —    | —    | —            | —    | —         | —         | —         | —          | —        | 0000          |

| 2000                        |                         | 15:0      |       |       |       |       |       |       |      |      | BN   | IXDUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |       |       |       |       |       |      |      | BM   | XDRMSZ<31:0  | >    |           |           |           |            |          | xxxx          |

|                             |                         | 15:0      |       |       |       | 1     |       |       |      | 1    |      |              |      | 1         |           |           |            |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —     | —     | —     |       | —     | -     | —    | _    | —    | _            | —    | —         |           | BMXPUPBA  | <19:16>    |          | 0000          |

|                             |                         | 15:0      |       |       |       |       |       |       |      |      | BN   | IXPUPBA<15:0 | >    |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |       |       |       |       |       |       |      |      | BM   | IXPFMSZ<31:0 | >    |           |           |           |            |          | xxxx          |

| 2000                        | 2                       | 15:0      |       |       |       |       |       |       |      |      | 5.   |              |      |           |           |           |            |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |       |       |       |       |       |       |      |      | BM   | XBOOTSZ<31:0 | )>   |           |           |           |            |          | 0000          |

|                             | # (20010E               | 15:0      |       |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          | 0C00          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | ¢,        |       | Bits  |       |       |             |       |        |        |      |      |      |      |             |      |        |                  |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|--------|--------|------|------|------|------|-------------|------|--------|------------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4 | 19/3        | 18/2 | 17/1   | 16/0             | All<br>Resets |

| 1100                        | 1007                            | 31:16     | _     | —     | —     |       | SPI1IP<2:0> |       | SPI1IS | S<1:0> | -    | —    | —    | US   | SBIP<2:0>(2 | :)   | USBIS  | <1:0> <b>(2)</b> | 0000          |

| 1100                        | IPC7                            | 15:0      | _     | -     | —     | (     | CMP3IP<2:0> | >     | CMP3IS | S<1:0> | _    | _    | _    | CI   | MP2IP<2:0>  | •    | CMP2I  | S<1:0>           | 0000          |

| 1110                        | IPC8                            | 31:16     | _     | _     | —     |       | PMPIP<2:0>  |       | PMPIS  | S<1:0> | _    | —    | _    | (    | CNIP<2:0>   |      | CNIS   | <1:0>            | 0000          |

| 1110                        | IPCo                            | 15:0      |       | —     | _     |       | I2C1IP<2:0> |       | I2C1IS | <1:0>  | —    | —    | _    | I    | J1IP<2:0>   |      | U1IS   | <1:0>            | 0000          |

| 1120                        | IPC9                            | 31:16     |       | —     | _     | (     | CTMUIP<2:0  | >     | CTMU   | S<1:0> | —    | —    | _    | 12   | 2C2IP<2:0>  |      | 12C218 | 6<1:0>           | 0000          |

| 1120                        | IFC9                            | 15:0      | -     | —     | _     |       | U2IP<2:0>   |       | U2IS<  | <1:0>  | _    | _    | _    | S    | PI2IP<2:0>  |      | SPI2IS | S<1:0>           | 0000          |

| 1130                        | IPC10                           | 31:16     | —     | _     | —     | [     | DMA3IP<2:0> | >     | DMA3IS | S<1:0> | _    | —    | _    | DI   | MA2IP<2:0>  | •    | DMA2I  | S<1:0>           | 0000          |

| 1130                        | IFC IU                          | 15:0      | _     | _     | _     | [     | DMA1IP<2:0> | >     | DMA1IS | S<1:0> | _    | _    | _    | DI   | VA0IP<2:0   | •    | DMA0I  | S<1:0>           | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |  |  |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

### Legend:

| <b>L</b> ogonan   |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

## REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|

|              | U-0                         | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                           | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |

|              | R/W-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                              |                   |                   |                     |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                       | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |

| 15:8         | ON                          | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |

| 7:0          | U-0                         | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                             |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |

### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

## REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| =0901141          |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 |                   |                   |                   | _                | —                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 |                   |                   | -                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

## REGISTER 10-4: U10TGCON: USB OTG CONTROL REGISTER

## Legend:

| Logona                            |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPUL | UP: D | )+ Pull-U | p Enable | bit |  |

|-------|-------|-------|-----------|----------|-----|--|

|       |       |       |           |          |     |  |

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

# bit 6 **DMPULUP:** D- Pull-Up Enable bit

- It 6 DIVIPOLOP: D- Pull-Op Enable bit

- 1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

- bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D + data line pull-down resistor is enabled

- 0 = D + data line pull-down resistor is disabled

- bit 4 **DMPULDWN:** D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 VBUSON: VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

- bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

- bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

# 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

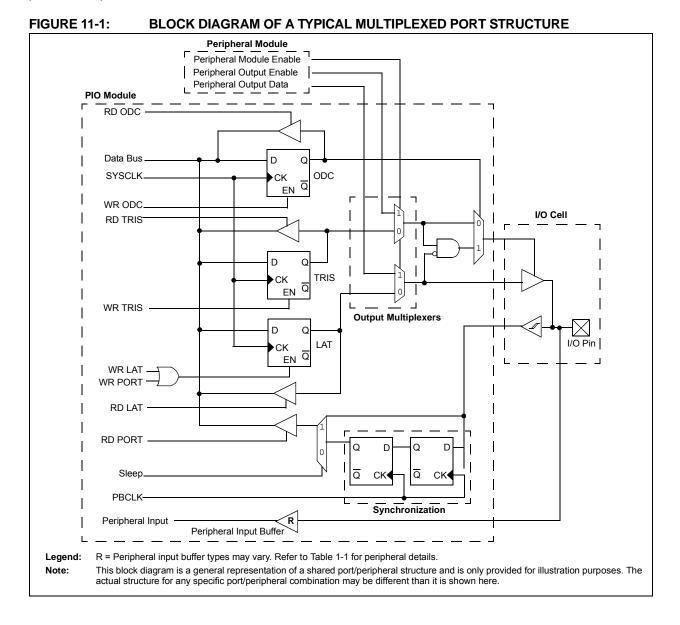

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Key features of this module include:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

|              |                   |                   |                   |                   |                   |                   |                  | ., _, _,         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | _                | _                |

## **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

NOTES:

# 19.1 UART Control Registers

# TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6         |        |        |        |       |        |       |       | Bi                  | ts          |         |       |             |        |       |        |       | 6          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|--------|--------|--------|-------|--------|-------|-------|---------------------|-------------|---------|-------|-------------|--------|-------|--------|-------|------------|

| 6000         0 MODE         15.0         ON         -         SIDL         IREN         RTSMD         -         UEN<1:0>         WAKE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1:0>         STSL         0.00           610         U1STA(1)         31:16         -         -         -         -         ADM_EN         VERSE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1:0>         STSL         0.00           600         U1STA(1)         15.0         UTXINV         URXEN         UTXENK         UTXEN         TRM         URXEN         TRMT         URXEN         ADDEN         RIDE         PERR         PERR         OER         URXDA         0100           600         U1TXREG         31:16         -         -         -         -         -         -         -         -         0000           6100         U1RXREG         31:16         -         -         -         -         -         -         -         -         -         0000           6100         U1RXREG         31:16         -         -         -         -         -         -         -         -         0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8                | 23/7        | 22/6    | 21/5  | 20/4        | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

| 610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610 <td>6000</td> <td></td> <td>31:16</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td>_</td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td></td> <td></td> <td>—</td> <td>_</td> <td>_</td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6000                        |                  | 31:16     |        |        | _      | _     | —      | _     |       | _                   | _           | —       |       |             | —      | _     | _      | _     | 0000       |

| 600         UTXIST         15.0         UTXIST         UTXINV         UTXRNV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000                        | 15:0             |           | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN   | -                   | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSEI | L<1:0> | STSEL | 0000       |

| 15:0         15:0         01XBE         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6010                        | 111STA(1)        | 31:16     | _      | _      | _      | —     | —      | _     | _     | ADM_EN              |             |         |       | ADDR        | 2<7:0> |       |        |       | 0000       |

| 600         UTXRE         1         -         -         -         -         -         -         -         -         -         -         000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0010                        | UIUIA            | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT                | URXIS       | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6020                        |                  | 31:16     | —      | -      | —      | _     | —      | —     | -     | —                   | _           | —       | —     | _           | _      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0020                        | UTTAKLG          | 15:0      | _      |        | _      |       | _      | -     |       |                     |             |         | Tra   | nsmit Regis | ster   |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6030                        |                  | 31:16     | _      |        | _      |       | _      | -     |       | _                   |             | _       | _     |             | -      |       | _      |       | 0000       |

| 600       11       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0030                        | UINAREG          | 15:0      | _      |        | _      |       | _      | -     |       |                     |             |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| 15:0         Bale Rate Generator Present         1000           6200         16:0 $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6040                        |                  | 31:16     | -      |        | -      |       | _      | -     |       | —                   |             | _       | -     |             | -      |       | -      |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00+0                        | 0 IDIXO          | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene         | erator Pres | caler   |       |             |        |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6200                        | 112MODE(1)       | 31:16     | _      | _      | _      | —     | —      | _     | _     | —                   | -           | —       | _     | -           | —      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0200                        | OZINODL          | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>               | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE  | L<1:0> | STSEL | 0000       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6210                        | 112974(1)        | 31:16     | _      |        | _      |       | _      | -     |       | ADM_EN              |             |         |       | ADDR        | <7:0>  |       |        |       | 0000       |

| 6220     U2TXREG     15:0     -     -     -     -     -     -     -     -     000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     0000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     0000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0210                        | 0231A. /         | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT                | URXISE      | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| 150     -     -     -     -     -     -     -     -     000       620     U2RXEG     31:16     -     -     -     -     -     -     -     -     000       620     U2BRG(1)     31:16     -     -     -     -     -     -     -     -     -     000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     -     000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6220                        |                  | 31:16     | _      |        | _      |       | _      | -     |       | _                   |             | _       | _     |             | -      |       | _      |       | 0000       |

| 6230     U2RXREG     -     -     -     -     -     -     -     0000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0220                        | UZTARLO          | 15:0      | _      |        | _      |       | _      | _     |       | Transmit Register 0 |             |         | 0000  |             |        |       |        |       |            |

| 150       -       -       -       -       -       -       -       0000         6240       U2BRG <sup>(1)</sup> 31:16       -       -       -       -       -       -       -       -       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6230                        |                  | 31:16     | _      | _      | _      | _     | _      | _     | _     | _                   | _           | _       | _     | _           | _      | _     | _      | _     | 0000       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0230                        | UZNAREG          | 15:0      | _      | _      | _      | _     | _      | _     | _     |                     |             |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| 02240     02000     15:0     Baud Rate Generator Prescaler     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6240                        |                  | 31:16     | _      | _      | _      | _     | _      | _     | _     | _                   | _           | _       | _     | _           | _      | _     | _      | _     | 0000       |