Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 19                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN (6x6)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128bt-50i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

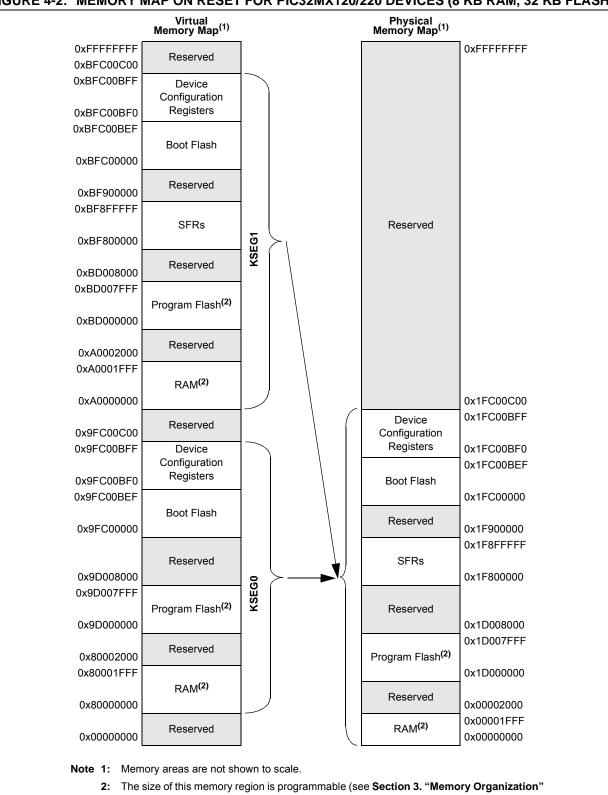

#### FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX120/220 DEVICES (8 KB RAM, 32 KB FLASH)

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit |                   |       |       |                   |                   |                   |                  |                  |  |  |  |

|-----------------------------------------|-------------------|-------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range                            | Bit<br>31/23/15/7 |       |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24                                   | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

|                                         | —                 | _     | _     | —                 | _                 | —                 | _                | —                |  |  |  |

| 00.40                                   | U-0               | U-0   | U-0   | U-0               | U-0 U-0           |                   | U-0              | U-0              |  |  |  |

| 23:16                                   | —                 | —     | _     | —                 | _                 | —                 | —                | —                |  |  |  |

| 45.0                                    | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8                                    |                   |       |       | BMXDU             | DBA<15:8>         |                   |                  |                  |  |  |  |

| 7.0                                     | R-0               | R-0   | R-0   | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0                                     |                   |       |       | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

#### bit 9-0 BMXDUDBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|--------------------|--------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                | U-0                |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                     | -                  | —                  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                     | -                  | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0                 | R/W-0, HS          | R/W-0              |

| 15:8         |                   | _                 | _                 | -                 | _                 | _                   | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS R/W-0, HS |                    | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE                | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-10 Unimplemented: Read as '0'

| bit 9 | CMR: Configuration Mismatch Reset Flag bit             |

|-------|--------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred          |

|       | 0 = Configuration mismatch Reset has not occurred      |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit            |

|       | 1 = Regulator is enabled and is on during Sleep mode   |

|       | 0 = Regulator is disabled and is off during Sleep mode |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit               |

|       | 1 = Master Clear (pin) Reset has occurred              |

|       | 0 = Master Clear (pin) Reset has not occurred          |

| bit 6 | SWR: Software Reset Flag bit                           |

|       | 1 = Software Reset was executed                        |

|       | 0 = Software Reset as not executed                     |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                 |

|       | 1 = WDT Time-out has occurred                          |

|       | 0 = WDT Time-out has not occurred                      |

| bit 3 | SLEEP: Wake From Sleep Flag bit                        |

|       | 1 = Device was in Sleep mode                           |

|       | 0 = Device was not in Sleep mode                       |

| bit 2 | IDLE: Wake From Idle Flag bit                          |

|       | 1 = Device was in Idle mode                            |

|       | 0 = Device was not in Idle mode                        |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>           |

|       | 1 = Brown-out Reset has occurred                       |

|       | 0 = Brown-out Reset has not occurred                   |

| bit 0 | POR: Power-on Reset Flag bit <sup>(1)</sup>            |

|       | 1 = Power-on Reset has occurred                        |

|       | 0 = Power-on Reset has not occurred                    |

|       |                                                        |

**Note 1:** User software must clear this bit to view next detection.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-----------------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0                         | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

|              | _                           | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

|              | R/W-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                              |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0                       | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |  |

| 15:8         | ON                          | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |  |

|              | U-0                         | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                             |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |  |  |  |

|-------------------|-------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |

|              | —                 | -                 | —                    | -                    | —                 | —                 | _                      | -                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0 U-0           |                        | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                    | —                    | —                 | —                 | —                      | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |

| 15.0         | —                 | -                 | —                    | -                    | —                 | —                 | -                      | -                |  |  |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |  |  |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |  |  |  |

|              | DISEF             | DIVIALE           | DIVIALLY             | BIOLE                | DINOLF            | GIVE IDEF         | EOFEF <sup>(3,5)</sup> |                  |  |  |  |  |

#### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re  | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

- 0 = No address error

- bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 BTOEF: Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### TABLE 11-5: PORTC REGISTER MAP

| ess                         | -                                 |           |       |       |       |       |       |       |                    |                       |                         | Bits                  |                       |                         |                    |                       |          |          |            |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------------|-----------------------|-------------------------|-----------------------|-----------------------|-------------------------|--------------------|-----------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9               | 24/8                  | 23/7                    | 22/6                  | 21/5                  | 20/4                    | 19/3               | 18/2                  | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     |       | _     |       |       | —     | —     | _                  |                       | _                       |                       | _                     | _                       | —                  | _                     | —        |          | 0000       |

| 0200                        | ,                                 | 15:0      | —     | —     | —     | —     | —     | —     |                    |                       | —                       |                       |                       | _                       | ANSC3(4)           | ANSC2 <sup>(3)</sup>  | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | —     | —     | —     | —     | —                  | —                     | —                       | —                     | —                     | —                       | —                  | —                     | —        |          | 0000       |

| 0210                        | 11100                             | 15:0      | _     | _     | —     | —     | —     | —     | TRISC9             | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup> | TRISC5 <sup>(3)</sup> | TRISC4 <sup>(3)</sup>   | TRISC3             | TRISC2 <sup>(3)</sup> | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | —     | —     | _                  |                       | _                       |                       | _                     |                         |                    |                       |          |          | 0000       |

| 0220 1 01(10                | 15:0                              | _         | _     | —     | —     | —     | —     | RC9   | RC8 <sup>(3)</sup> | RC7 <sup>(3)</sup>    | RC6 <sup>(3)</sup>      | RC5 <sup>(3)</sup>    | RC4 <sup>(3)</sup>    | RC3                     | RC2 <sup>(3)</sup> | RC1                   | RC0      | xxxx     |            |

| 6230                        | LATC                              | 31:16     | _     | _     | —     | —     | —     | —     | _                  |                       | _                       |                       |                       | _                       | —                  |                       | —        | —        | 0000       |

| 0230                        | 6230 LATC                         | 15:0      |       |       | _     | _     | _     | _     | LATC9              | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>  | LATC5 <sup>(3)</sup>  | LATC4 <sup>(3)</sup>    | LATC3              | LATC2 <sup>(3)</sup>  | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     |       |       | _     | _     | _     | _     | _                  |                       |                         |                       |                       |                         | _                  |                       | _        | _        | 0000       |

| 6240                        | ODCC                              | 15:0      |       |       | _     | _     | _     | _     | ODCC9              | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>  | ODCC5 <sup>(3)</sup>  | ODCC4 <sup>(3)</sup>    | ODCC3              | ODCC2 <sup>(3)</sup>  | ODCC1    | ODCC0    | 0000       |

| 0050                        |                                   | 31:16     |       |       | —     | —     | —     | -     | —                  | -                     | _                       | -                     | —                     | —                       | —                  | —                     | —        | —        | 0000       |

| 6250                        | CNPUC                             | 15:0      | _     | _     | _     | _     | —     | —     | CNPUC9             | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup> | CNPUC5 <sup>(3)</sup> | CNPUC4 <sup>(3)</sup>   | CNPUC3             | CNPUC2 <sup>(3)</sup> | CNPUC1   | CNPUC0   | 0000       |

| 0000                        |                                   | 31:16     | _     | _     | _     | _     | _     | _     | —                  | _                     | _                       | _                     | _                     | —                       | _                  | —                     | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | —     | —     | —     | —     | CNPDC9             | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup> | CNPDC5 <sup>(3)</sup> | CNPDC4 <sup>(3)</sup>   | CNPDC3             | CNPDC2 <sup>(3)</sup> | CNPDC1   | CNPDC0   | 0000       |

| 0070                        | anaana                            | 31:16     | _     | _     | —     | —     | —     | —     | _                  | _                     | _                       | _                     | —                     | —                       | —                  | _                     | —        | —        | 0000       |

| 6270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | —     | —     | —     | _                  | _                     | _                       | _                     | _                     | —                       | —                  | _                     | —        | _        | 0000       |

|                             |                                   | 31:16     | _     | _     | _     |       | —     | _     |                    |                       | _                       |                       | _                     | _                       | _                  | _                     | —        | —        | 0000       |

| 6280                        | CNENC                             | 15:0      | _     | _     | _     |       | —     | _     | CNIEC9             | CNIEC8(3)             | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)             | CNIEC5 <sup>(3)</sup> | CNIEC4 <sup>(3)</sup>   | CNIEC3             | CNIEC2 <sup>(3)</sup> | CNIEC1   | CNIEC0   | 0000       |

|                             |                                   | 31:16     | _     | _     | _     | _     | _     | _     | _                  |                       | _                       |                       | _                     | _                       | —                  |                       | —        | —        | 0000       |

| 6290                        | CNSTATC                           | 15:0      | _     | _     | _     | _     | _     | _     | CNSTATC9           | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6(3)           | CNSTATC5(3)           | CNSTATC4 <sup>(3)</sup> | CNSTATC3           | CNSTATC2(3)           | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

3: This bit is only available on 44-pin devices.

4: This bit is only available on USB-enabled devices with 36 or 44 pins.

## TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | _    | 0000       |

| FB8C                        | RPCOR                | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | —    | 0000       |

| FB90                        | KPC9R <sup>w</sup>   | 15:0      |       | —     | —     | —     | _     | -     | —    | —    | _    | _    | —    |      |      | RPC9 | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

# 14.1 Watchdog Timer Control Registers

# TABLE 14-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                       |                                 | 6         |       | Bits  |       |       |       |       |      |      |      |      |      |      |      | s    |      |      |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                      | WDTCON                          | 31:16     | _     | —     | _     | —     | _     |       | _    | _    | -    | _    | —    | -    | _    | —    | -    | —    | 0000       |

| 0000                      | WDICON                          | 15:0      | ON    | _     |       | _     | _     | _     |      | _    |      |      |      |      |      |      | 0000 |      |            |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

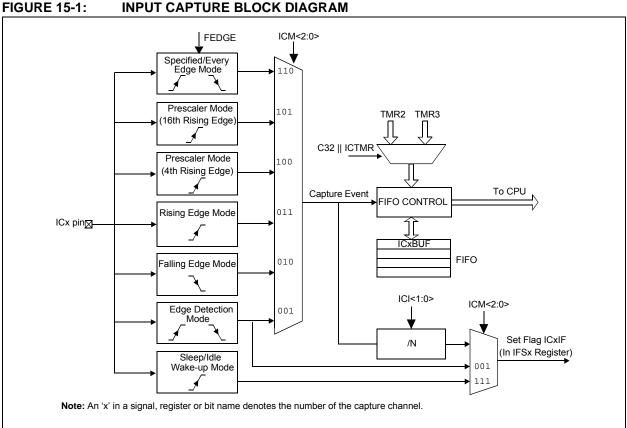

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

# 16.1 Output Compare Control Registers

## TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |                   | Bits  |       |       |       |       |       |      |       |         |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|-------------------|-------|-------|-------|-------|-------|-------|------|-------|---------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16             | —     | —     | —     | —     | —     | —     | —    | _     | —       | —    | —    | —     | —      | _    | —        | _    | 0000         |

| 0000                        | 001001                          | 15:0              | ON    | —     | SIDL  | —     | —     | —     |      | —     | —       | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0     |       |       |       |       |       |       |      | OC1R  | <31:0>  |      |      |       |        |      |          |      | xxxx         |

| 3020                        | OC1RS                           | 31:16<br>15:0     |       |       |       |       |       |       |      | OC1RS | S<31:0> |      |      |       |        |      |          |      | xxxx         |

| 0000                        | 00000                           | 31:16             | —     | _     | _     | _     | _     | _     |      | _     | —       | —    | _    | —     | —      | —    | —        | —    | 0000         |

| 3200                        | OC2CON                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3210                        | OC2R                            | 31:16             |       |       |       |       |       |       |      | OC2R  | ~21.0>  |      |      |       |        |      |          |      | xxxx         |

| 3210                        | UCZR                            | 15:0              |       |       |       |       |       |       |      | UCZR  | <31.0>  |      |      |       |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 31:16             |       |       |       |       |       |       |      | OC2RS | 2-31-05 |      |      |       |        |      |          |      | XXXX         |

| 3220                        | 00283                           | 15:0              |       |       |       |       |       |       |      | UCZRO | 5<31.02 |      |      |       |        |      |          |      | XXXX         |

| 3400                        | OC3CON                          | 31:16             | _     | _     | _     | _     | _     | _     | _    | _     | _       | _    | _    | _     | —      |      | —        |      | 0000         |

| 3400                        | 003001                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | -       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0     |       |       |       |       |       |       |      | OC3R  | <31:0>  |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16             |       |       |       |       |       |       |      | OC3R8 | 221.05  |      |      |       |        |      |          |      | XXXX         |

| 3420                        | 00383                           | 15:0              |       |       |       |       |       |       |      | UCSRC | 5-51.0- |      |      |       |        |      |          |      | XXXX         |

| 3600                        | OC4CON                          | 31:16             | —     | _     | _     | _     | _     | _     | _    | _     | —       | —    | _    | —     | —      |      | —        | _    | 0000         |

| 3000                        | 004001                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | -       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16             |       |       |       |       |       |       |      | OC4R  | <31.0>  |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0041                            | 15:0              |       |       |       |       |       |       |      | 0041  | ST.02   |      |      |       |        |      |          |      | xxxx         |

| 3620                        | OC4RS                           | 31:16             |       |       |       |       |       |       |      | OC4RS | 231.05  |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00410                           | 15:0              |       |       |       |       |       |       |      | 00400 | 5-51.02 |      |      |       |        |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16             | -     | _     | —     | _     | _     | _     | _    | _     | -       | _    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | 000000                          | 15:0              | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —       | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16             |       |       |       |       |       |       |      | OC5R  | <31.0>  |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0000                            | 15:0              |       |       |       |       |       |       |      | OUJK  | -01.02  |      |      |       |        |      |          |      | xxxx         |

| 3820                        | OC5RS                           | 31:16             |       |       |       |       |       |       |      | OC5RS | <31·0>  |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00010                           | 15 <sup>.</sup> 0 |       |       |       |       |       |       |      | 00000 | -01.02  |      |      |       |        |      |          |      | xxxx         |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 17.1 SPI Control Registers

# TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| ess                         |                                 | Bits      |               |         |        |              |              |              |           |        |         |           |        |        |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|-----------|--------|--------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6      | 21/5   | 20/4   | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —         | _      | -      | —           | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | —             | _       | _      |              | RXE          | BUFELM<4:    | 0>        |        | —       | —         | -      |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| 5610                        |                                 | 15:0      | _             | —       | —      | FRMERR       | SPIBUSY      | —            | —         | SPITUR | SRMT    | SPIROV    | SPIRBE | —      | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 3020                        |                                 | 15:0      |               |         |        |              |              |              |           | Brance | .01.0   |           |        |        |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | —             | —       | _      | —            | —            | —            | —         | —      | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 0000                        |                                 | 15:0      | _             | —       | _      |              |              |              |           |        | E       | 3RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | —            | —            | —            | —         | —      | —       | —         | _      | _      | —           | _        | —      | —       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | _       |        | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —         | -      | -      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —         |        |        | _           |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 3F1200N                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5410                        | SPI2STAT                        | 31:16     | —             | —       |        |              | RXE          | BUFELM<4:    | 0>        |        | _       | -         |        |        | TX          | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV    | SPIRBE | _      | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.0>   |           |        |        |             |          |        |         | 0000       |

| 5420                        |                                 | 15:0      |               |         |        |              |              |              |           | Brance |         |           |        |        |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | —             | —       | _      | —            | —            | —            | —         | —      | —       | —         | —      | —      | —           | —        | —      | —       | 0000       |

| 5730                        |                                 | 15:0      |               | —       | —      |              |              |              |           |        | E       | 3RG<12:0> |        |        |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | _            | —            | _            | —         | —      | —       | —         | _      | —      | —           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | —       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —         | _      | _      | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

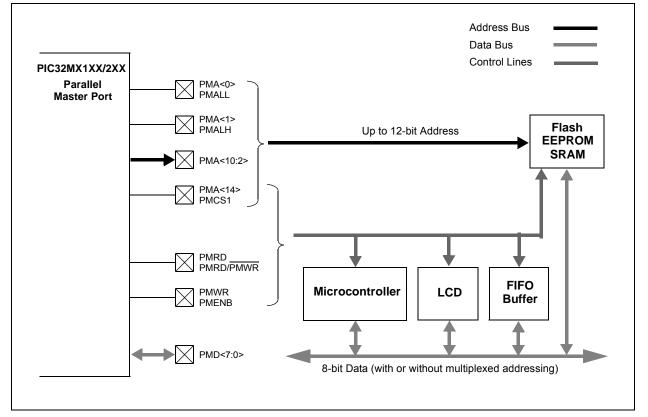

# 20.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to Section 13. "Parallel<br>Master Port (PMP)" (DS60001128), |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | which is available from the <i>Documentation</i><br>> <i>Reference Manual</i> section of the<br>Microchip PIC32 web site<br>(www.microchip.com/pic32).                                                                                                                                       |

The PMP is a parallel 8-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Key features of the PMP module include:

- Fully multiplexed address/data mode

- Demultiplexed or partially multiplexed address/ data mode

- up to 11 address lines with single Chip Select

- up to 12 address lines without Chip Select

- One Chip Select line

- Programmable strobe options

- Individual read and write strobes or;

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- · Legacy parallel slave port support

- · Enhanced parallel slave support

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- · Selectable input voltage levels

Figure 20-1 illustrates the PMP module block diagram.

#### FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 Трв

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 Трв

- 10 = Wait of 2 TPB

- 01 = Wait of 1 ТРВ

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read

If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

## 23.1 Comparator Control Registers

#### TABLE 23-1: COMPARATOR REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |       |      | Bi   | its  |        |      |      |      |       |       |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Reset |

| 4000                        | CM1CON                          | 31:16     | _     | —     | _     | _     | -     | _     |      | -    | —    | _      | -    | —    | —    | —     | _     | _     | 0000      |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A010                        | CM2CON                          | 31:16     | —     | -     |       |       | -     |       | -    | -    | —    | —      | -    | _    | —    | —     |       | —     | 0000      |

| AUTO                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | _     |       | _     |      | COUT | EVPO | L<1:0> |      | CREF | _    | _     | CCH   | <1:0> | 00C3      |

| A020                        | CM3CON                          | 31:16     | _     | _     | _     | _     |       | _     |      |      | _    | _      |      | _    | _    | _     | _     | _     | 0000      |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A060                        | CMSTAT                          | 31:16     | —     | _     | _     | _     | -     | _     | _    |      | —    | _      | -    | _    | _    | —     | _     | —     | 0000      |

| 7000                        | CIVISTAI                        | 15:0      | _     | _     | SIDL  | _     |       | _     |      |      | -    | _      |      | _    |      | C3OUT | C2OUT | C10UT | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

NOTES:

### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        |         | STICS                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |                    |       |                                                                 |  |  |  |  |

|---------------|---------|-------------------------------------------------------------|-------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                             | Min.                                                  | Тур. | Max.               | Units | Comments                                                        |  |  |  |  |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                     | _    | 10                 | μs    | See Note 1                                                      |  |  |  |  |

| D313          | DACREFH | CVREF Input Voltage                                         | AVss                                                  | _    | AVDD               | V     | CVRSRC with CVRSS = 0                                           |  |  |  |  |

|               |         | Reference Range                                             | VREF-                                                 | _    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |  |  |

| D314          | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                     | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |  |  |

|               |         |                                                             | 0.25 x<br>DACREFH                                     | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |  |  |

| D315          | DACRES  | Resolution                                                  | —                                                     | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |  |  |  |

|               |         |                                                             | _                                                     | —    | DACREFH/32         | _     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |  |  |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                            |                                                       | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |  |  |

|               |         |                                                             |                                                       | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |  |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

**2:** These parameters are characterized but not tested.

#### TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHA        | RACTERIS | STICS                           | (unles | ard Operat<br>s otherwis<br>ing temper | e stated<br>ature | <b>1)</b><br>-40°C ≤ <sup>°</sup> | : <b>2.3V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +105°C for V-temp             |

|---------------|----------|---------------------------------|--------|----------------------------------------|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol   | Characteristics                 | Min.   | Typical                                | Max.              | Units                             | Comments                                                                                           |

| D321          | Cefc     | External Filter Capacitor Value | 8      | 10                                     |                   | μF                                | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |

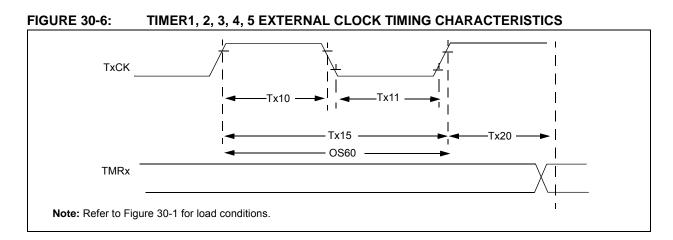

### TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS | TICS <sup>(1)</sup>                                         |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                            |         |      |       |                               |  |  |  |  |

|---------------|-----------|-------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|------|-------|-------------------------------|--|--|--|--|

| Param.<br>No. | Symbol    | Charac                                                      | teristics <sup>(2)</sup>  |                                                                                                                                                                                                                                                                                     | Min.                                       | Typical | Max. | Units | Conditions                    |  |  |  |  |

| TA10          | T⊤xH      | TxCK<br>High Time                                           | Synchronow with presca    |                                                                                                                                                                                                                                                                                     | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —       | —    | ns    | Must also meet parameter TA15 |  |  |  |  |

|               |           |                                                             | Asynchrono<br>with presca |                                                                                                                                                                                                                                                                                     | 10                                         | —       | _    | ns    | —                             |  |  |  |  |

| TA11          | T⊤xL      | TxCK<br>Low Time                                            | Synchronor<br>with presca |                                                                                                                                                                                                                                                                                     | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns          | —       | —    | ns    | Must also meet parameter TA15 |  |  |  |  |

|               |           |                                                             | Asynchrono<br>with presca |                                                                                                                                                                                                                                                                                     | 10                                         | _       | _    | ns    | —                             |  |  |  |  |

| TA15          | ΤτχΡ      | TxCK<br>Input Period                                        | Synchrono<br>with presca  |                                                                                                                                                                                                                                                                                     | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns | -       | _    | ns    | VDD > 2.7V                    |  |  |  |  |

|               |           |                                                             |                           |                                                                                                                                                                                                                                                                                     | [(Greater of 25 ns or<br>2 Трв)/N] + 50 ns | -       | —    | ns    | VDD < 2.7V                    |  |  |  |  |

|               |           |                                                             | Asynchrono<br>with presca |                                                                                                                                                                                                                                                                                     | 20                                         | -       | _    | ns    | VDD > 2.7V<br>(Note 3)        |  |  |  |  |

|               |           |                                                             |                           |                                                                                                                                                                                                                                                                                     | 50                                         | -       | _    | ns    | VDD < 2.7V<br>(Note 3)        |  |  |  |  |

| OS60          | FT1       | SOSC1/T1C<br>Input Freque<br>(oscillator en<br>the TCS (T10 | ncy Range<br>abled by set |                                                                                                                                                                                                                                                                                     | 32                                         | —       | 100  | kHz   | -                             |  |  |  |  |

| TA20          | TCKEXTMRL | Delay from E<br>Clock Edge t<br>Increment                   |                           | К                                                                                                                                                                                                                                                                                   |                                            | —       | 1    | Трв   | —                             |  |  |  |  |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).