Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128bt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|                 |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | rals                               |                    |                     |     |     | <u> </u>                                 |      | ls)                          |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|-----|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l²C | PMP | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F064B | 28   | 64+3                               | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F064C | 36   | 64+3                               | 16               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Υ    | VTLA                            |

| PIC32MX130F064D | 44   | 64+3                               | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX150F128B | 28   | 128+3                              | 32               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX150F128C | 36   | 128+3                              | 32               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX150F128D | 44   | 128+3                              | 32               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F256B | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F256D | 44   | 256+3                              | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX170F256B | 28   | 256+3                              | 64               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX170F256D | 44   | 256+3                              | 64               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

## TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming™ (ICSP™)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 31:24        |                   | _                 |                   | —                 | _                 |                      | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                    | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0            | R/W-0            |

| 15:8         |                   | _                 |                   | _                 | _                 | S                    | RIPL<2:0>(1)     |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

#### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D:                | Dir              | Dit              |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | IPTMF             | <31:24>           |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = FSCM has detected a clock failure                                                                                                                          |

|         | 0 = No clock failure has been detected                                                                                                                         |

| bit 2   | UFRCEN: USB FRC Clock Enable bit <sup>(1)</sup>                                                                                                                |

|         | <ul> <li>1 = Enable the FRC as the clock source for the USB clock source</li> <li>0 = Use the Primary Oscillator or USB PLL as the USB clock source</li> </ul> |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                 |

|         | 1 = Enable the Secondary Oscillator                                                                                                                            |

|         | 0 = Disable the Secondary Oscillator                                                                                                                           |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                                                                                            |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                |

| Note 1: | This bit is only available on PIC32MX2XX devices.                                                                                                              |

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------|-------------------|-------------------|-------------------|-------------------------------------------|-------------------|------------------|------------------|--|--|

|              | U-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                                     | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | _                           |                   |                   | R                 | )<2017<2000000000000000000000000000000000 | 1,3)              |                  |                  |  |  |

|              | R/W-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-0                                     | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                   |                   |                   |                                           |                   |                  |                  |  |  |

| 45.0         | R/W-0                       | U-0               | R/W-0             | R/W-0             | R/W-0                                     | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |

| 15:8         | ON                          | _                 | SIDL              | OE                | RSLP <sup>(2)</sup>                       | _                 | DIVSWEN          | ACTIVE           |  |  |

|              | U-0                         | U-0               | U-0               | U-0               | R/W-0                                     | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                             |                   |                   |                   |                                           | ROSEL             | .<3:0>(1)        |                  |  |  |

#### REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | -                 | _                 |                   |                  | —                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHSPTR            | <15:8>            |                   | - <u> </u>       |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |

#### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | _     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

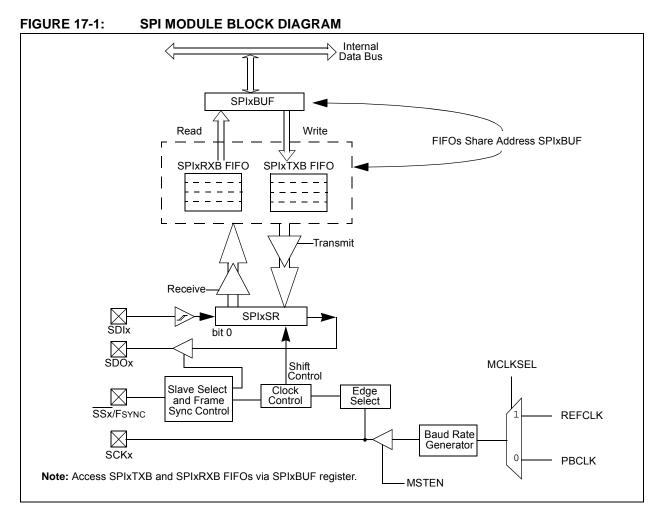

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- Master mode and Slave mode support

- Four clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

| REGIST    | ER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                         |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                             |  |  |  |  |  |  |  |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                         |  |  |  |  |  |  |  |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                               |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup>                                                          |  |  |  |  |  |  |  |

|           | 1 = Enhanced Buffer mode is enabled                                                                        |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer mode is disabled                                                                       |  |  |  |  |  |  |  |

| bit 15    | ON: SPI Peripheral On bit <sup>(1)</sup>                                                                   |  |  |  |  |  |  |  |

|           | 1 = SPI Peripheral is enabled                                                                              |  |  |  |  |  |  |  |

|           | 0 = SPI Peripheral is disabled                                                                             |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                 |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                |  |  |  |  |  |  |  |

|           | 1 = Discontinue module operation when the device enters Idle mode                                          |  |  |  |  |  |  |  |

|           | 0 = Continue module operation when the device enters Idle mode                                             |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDOx pin bit                                                                               |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                      |  |  |  |  |  |  |  |

|           | 0 = SDOx pin is controlled by the module                                                                   |  |  |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                           |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                            |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                |  |  |  |  |  |  |  |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |

|           | 0 1 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |

|           | 0 0 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                  |  |  |  |  |  |  |  |

|           |                                                                                                            |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                            |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                |  |  |  |  |  |  |  |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                   |  |  |  |  |  |  |  |

|           | 0 	 1 	 10-51                                                                                              |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                       |  |  |  |  |  |  |  |

| bit 5     | Master mode (MSTEN = 1):                                                                                   |  |  |  |  |  |  |  |

|           | 1 = Input data sampled at end of data output time                                                          |  |  |  |  |  |  |  |

|           | 0 = Input data sampled at middle of data output time                                                       |  |  |  |  |  |  |  |

|           | Slave mode (MSTEN = 0):                                                                                    |  |  |  |  |  |  |  |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                       |  |  |  |  |  |  |  |

|           | To write a '1' to this bit, the MSTEN value = 1 must first be written.                                     |  |  |  |  |  |  |  |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                              |  |  |  |  |  |  |  |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit) |  |  |  |  |  |  |  |

|           | 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit) |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                 |  |  |  |  |  |  |  |

|           | $1 = \overline{SSx}$ pin used for Slave mode                                                               |  |  |  |  |  |  |  |

|           | 0 = SSx pin not used for Slave mode, pin controlled by port function.                                      |  |  |  |  |  |  |  |

| bit 6     | <b>CKP:</b> Clock Polarity Select bit <sup>(4)</sup>                                                       |  |  |  |  |  |  |  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                      |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock is a low level; active state is a high level                                      |  |  |  |  |  |  |  |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in    |  |  |  |  |  |  |  |

|           | the SYSCLK cycle immediately following the instruction that clears the module's ON bit.                    |  |  |  |  |  |  |  |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                       |  |  |  |  |  |  |  |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI    |  |  |  |  |  |  |  |

|           | mode (FRMEN = 1).                                                                                          |  |  |  |  |  |  |  |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value |  |  |  |  |  |  |  |

|           | of CKP.                                                                                                    |  |  |  |  |  |  |  |

|           |                                                                                                            |  |  |  |  |  |  |  |

2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        |                   | _                 | _                 |                   | R                 | XBUFELM<4:        | 0>               |                  |  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        |                   | _                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |

| 15:8         |                   | —                 | _                 | FRMERR            | SPIBUSY           | —                 | —                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |  |

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware               |                    |  |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

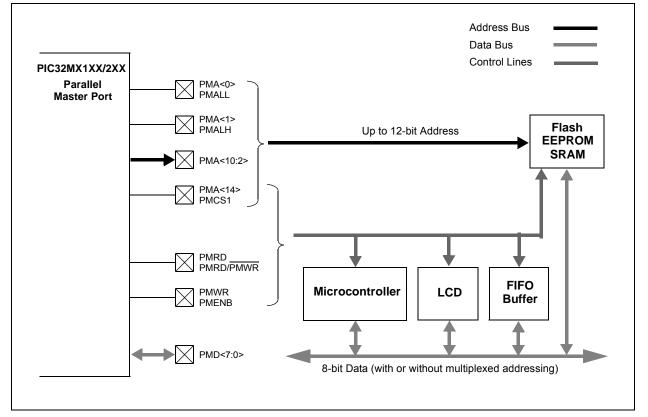

## 20.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to Section 13. "Parallel<br>Master Port (PMP)" (DS60001128), |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | which is available from the <i>Documentation</i><br>> <i>Reference Manual</i> section of the<br>Microchip PIC32 web site<br>(www.microchip.com/pic32).                                                                                                                                       |

The PMP is a parallel 8-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. Key features of the PMP module include:

- Fully multiplexed address/data mode

- Demultiplexed or partially multiplexed address/ data mode

- up to 11 address lines with single Chip Select

- up to 12 address lines without Chip Select

- One Chip Select line

- Programmable strobe options

- Individual read and write strobes or;

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- · Legacy parallel slave port support

- · Enhanced parallel slave support

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- · Selectable input voltage levels

Figure 20-1 illustrates the PMP module block diagram.

#### FIGURE 20-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

## TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | a         |       |                                    |       |       |       |       |         | Bi         | ts        |           |      |      |      |      |      |      | s          |

|-----------------------------|------------------|-----------|-------|------------------------------------|-------|-------|-------|-------|---------|------------|-----------|-----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8       | 23/7      | 22/6      | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9120                        | ADC1BUFB         | 31:16     |       |                                    |       |       |       |       | ADC Res | ult Word B |           | B<31.0>)  |      |      |      |      |      |      | 0000       |

| 0120                        | ABO IBOI B       | 15:0      |       | ADC Result Word B (ADC1BUFB<31:0>) |       |       |       |       |         |            |           | 0000      |      |      |      |      |      |      |            |

| 0130                        | ADC1BUFC         | 31:16     |       | ADC Result Word C (ADC1BUFC<31:0>) |       |       |       |       |         |            |           | 0000      |      |      |      |      |      |      |            |

| 9130                        | ADCIDUIC         | 15:0      |       |                                    |       |       |       |       | ADC NES |            | (ADC ID01 | 0~31.0~)  |      |      |      |      |      |      | 0000       |

| 0140                        | ADC1BUFD         | 31:16     |       |                                    |       |       |       |       |         |            | (ADC1BUF  |           |      |      |      |      |      |      | 0000       |

| 9140                        | ADC IDOI D       | 15:0      |       |                                    |       |       |       |       | ADC Nes |            | (ADC ID01 | D~31.0~)  |      |      |      |      |      |      | 0000       |

| 0150                        | ADC1BUFE         | 31:16     |       |                                    |       |       |       |       |         |            | (ADC1BUF  | E<31.0>)  |      |      |      |      |      |      | 0000       |

| 3150                        |                  | 15:0      |       |                                    |       |       |       |       |         |            |           | ∟ <01.07) |      |      |      |      |      |      | 0000       |

| 0160                        | ADC1BUFF         | 31:16     |       | ADC Result Word F (ADC1BUFF<31:0>) |       |       |       |       |         |            |           | 0000      |      |      |      |      |      |      |            |

| 9100                        | ADGIDUFF         | 15:0      |       |                                    |       |       |       |       | ADC Res |            |           | (~51.0~)  |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

#### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

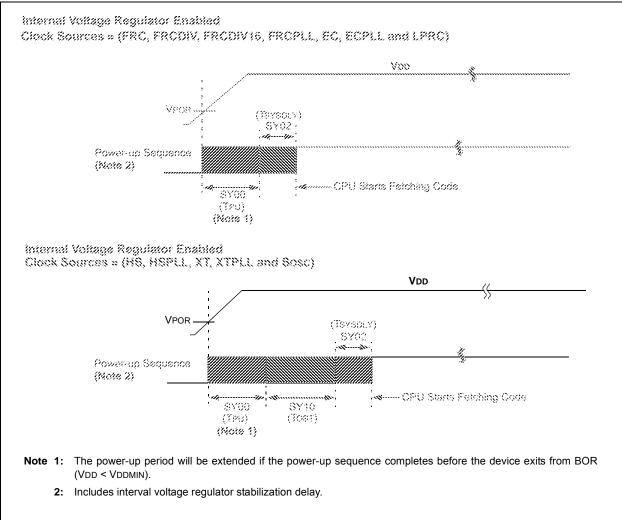

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

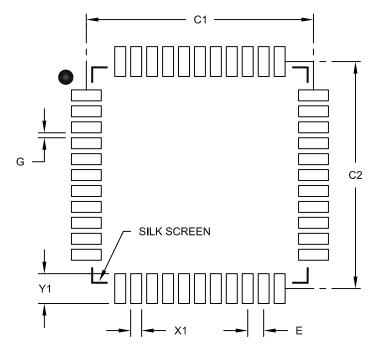

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |      |          |      |  |  |  |

|--------------------------|------------------|------|----------|------|--|--|--|

| Dimension                | Dimension Limits |      |          |      |  |  |  |

| Contact Pitch            | E                |      | 0.80 BSC |      |  |  |  |

| Contact Pad Spacing      | C1               |      | 11.40    |      |  |  |  |

| Contact Pad Spacing      | C2               |      | 11.40    |      |  |  |  |

| Contact Pad Width (X44)  | X1               |      |          | 0.55 |  |  |  |

| Contact Pad Length (X44) | Y1               |      |          | 1.50 |  |  |  |

| Distance Between Pads    | G                | 0.25 |          |      |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

## APPENDIX A: REVISION HISTORY

## Revision A (May 2011)

This is the initial released version of this document.

## **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX130F064C

- PIC32MX130F064D

- PIC32MX150F128B

- PIC32MX150F128CPIC32MX150F128D

- PIC32MX250F128C

PIC32MX250F128D

PIC32MX230F064B

PIC32MX230F064C

PIC32MX230F064D

PIC32MX250F128B

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

| Section                                                                    | Update Description                                                                                                                                                        |  |  |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |  |  |  |  |  |

| and Graphics Interfaces, USB, and Advanced Analog"                         | Added the SPDIP package reference (see Table 1, Table 2, and " <b>Pin Diagrams</b> ").                                                                                    |  |  |  |  |  |

|                                                                            | Added the new devices to the applicable pin diagrams.                                                                                                                     |  |  |  |  |  |

|                                                                            | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |  |  |  |  |  |

| 1.0 "Device Overview"                                                      | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |  |  |  |  |  |

|                                                                            | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |  |  |  |  |  |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"          | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |  |  |  |  |  |

#### TABLE A-1: MAJOR SECTION UPDATES

## **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

#### TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |

|                                                                                                                                   | Added Program Flash Size value for 256 KB Flash devices (see Register 4-5).                                                                          |

| 12.0 "Timer1"                                                                                                                     | The Timer1 block diagram was updated to include the 16-bit data bus (see Figure 12-1).                                                               |

| 13.0 "Timer2/3, Timer4/5"                                                                                                         | The Timer2-Timer5 block diagram (16-bit) was updated to include the 16-bit data bus (see Figure 13-1).                                               |

|                                                                                                                                   | The Timer2/3, Timer4/5 block diagram (32-bit) was updated to include the 32-<br>bit data bus (see Figure 13-1).                                      |

| 19.0 "Parallel Master Port (PMP)"                                                                                                 | The CSF<1:0> bit value definitions for '00' and '01' were updated (see Register 19-1).                                                               |

|                                                                                                                                   | Bit 14 in the Parallel Port Address register (PMADDR) was updated (see Register 19-3).                                                               |

| 20.0 "Real-Time Clock and                                                                                                         | The following registers were updated:                                                                                                                |

| Calendar (RTCC)"                                                                                                                  | RTCTIME (see Register 20-3)                                                                                                                          |

|                                                                                                                                   | RTCDATE (see Register 20-4)                                                                                                                          |

|                                                                                                                                   | ALRMTIME (see Register 20-5)                                                                                                                         |

|                                                                                                                                   | ALRMDATE (see Register 20-6)                                                                                                                         |

| 26.0 "Special Features"                                                                                                           | Updated the PWP bits (see Register 26-1).                                                                                                            |

| 29.0 "Electrical Characteristics"                                                                                                 | Added parameters DO50 and DO50a to the Capacitive Loading Requirements on Output Pins (see Table 29-14).                                             |

|                                                                                                                                   | Added Note 5 to the IDD DC Characteristics (see Table 29-5).                                                                                         |

|                                                                                                                                   | Added Note 4 to the IIDLE DC Characteristics (see Table 29-6).                                                                                       |

|                                                                                                                                   | Added Note 5 to the IPD DC Characteristics (see Table 29-7).                                                                                         |

|                                                                                                                                   | Updated the conditions for parameters USB321 (VOL) and USB322 (VOH) in the OTG Electrical Specifications (see Table 29-38).                          |

| Product Identification System                                                                                                     | Added 40 MHz speed information.                                                                                                                      |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| (64 KB RAM, 256 KB Flash)                         | 42  |

|---------------------------------------------------|-----|

| Memory Organization                               | 37  |

| Microchip Internet Web Site                       | 341 |

| MPLAB ASM30 Assembler, Linker, Librarian          | 254 |

| MPLAB Integrated Development Environment Software | 253 |

| MPLAB PM3 Device Programmer                       | 255 |

| MPLAB REAL ICE In-Circuit Emulator System         | 255 |

| MPLINK Object Linker/MPLIB Object Librarian       | 254 |

|                                                   |     |

## 0

| Oscillator Configuration | 73  |

|--------------------------|-----|

| Output Compare           | 161 |

## Ρ

| -                                  |     |

|------------------------------------|-----|

| Packaging                          |     |

| Details                            | 313 |

| Marking                            |     |

| Parallel Master Port (PMP)         |     |

| PIC32 Family USB Interface Diagram | 104 |

| Pinout I/O Descriptions (table)    | 20  |

| Power-on Reset (POR)               |     |

| and On-Chip Voltage Regulator      |     |

| Power-Saving Features              |     |

| CPU Halted Methods                 |     |

| Operation                          |     |

| with CPU Running                   |     |

| -                                  |     |

## R

| Real-Time Clock and Calendar (RTCC)            | .199 |

|------------------------------------------------|------|

| Register Maps                                  | 5–?? |

| Registers                                      |      |

| [pin name]R (Peripheral Pin Select Input)      |      |

| AD1CHS (ADC Input Select)                      | .217 |

| AD1CON1 (ADC Control 1)                        | 213  |

| AD1CON2 (ADC Control 2)                        | 215  |

| AD1CON3 (ADC Control 3)                        | 216  |

| AD1CSSL (ADC Input Scan Select)                | .218 |

| ALRMDATE (Alarm Date Value)                    | 208  |

| ALRMTIME (Alarm Time Value)                    | 207  |

| BMXBOOTSZ (Boot Flash (IFM) Size               | 51   |

| BMXCON (Bus Matrix Configuration)              | 46   |

| BMXDKPBA (Data RAM Kernel Program              |      |

| Base Address)                                  |      |

| BMXDRMSZ (Data RAM Size Register)              |      |

| BMXDUDBA (Data RAM User Data Base Address)     | 48   |

| BMXDUPBA (Data RAM User Program                |      |

| Base Address)                                  |      |

| BMXPFMSZ (Program Flash (PFM) Size)            | 51   |

| BMXPUPBA (Program Flash (PFM) User Program     |      |

| Base Address)                                  |      |

| CFGCON (Configuration Control)                 |      |

| CM1CON (Comparator 1 Control)                  |      |

| CMSTAT (Comparator Status Register)            |      |

| CNCONx (Change Notice Control for PORTx)       |      |

| CTMUCON (CTMU Control)                         |      |

| CVRCON (Comparator Voltage Reference Control). |      |

| DCHxCON (DMA Channel 'x' Control)              |      |

| DCHxCPTR (DMA Channel 'x' Cell Pointer)        |      |

| DCHxCSIZ (DMA Channel 'x' Cell-Size)           |      |

| DCHxDAT (DMA Channel 'x' Pattern Data)         |      |

| DCHxDPTR (Channel 'x' Destination Pointer)     | 99   |

| DCHxDSA (DMA Channel 'x' Destination           |      |

| Start Address)                                 |      |

| DCHxDSIZ (DMA Channel 'x' Destination Size)    |      |

| DCHxECON (DMA Channel 'x' Event Control)       |      |

| DCHxINT (DMA Channel 'x' Interrupt Control)    | 95   |

|                                                |      |

| DCHxSPTR (DMA Channel 'x' Source Pointer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                    |