Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 23                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 12x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128ct-v-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

#### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

|                 |                             | OUT I/O D<br>Pin Nui                        |                                       |                                 |             | Í                    |                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------|---------------------------------------|---------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------|

| Pin Name        | 28-pin<br>QFN               | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                        | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                                     |

| PMA0            | 7                           | 10                                          | 8                                     | 3                               | I/O         | TTL/ST               | Parallel Master Port Address bit 0 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA1            | 9                           | 12                                          | 10                                    | 2                               | I/O         | TTL/ST               | Parallel Master Port Address bit 1 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA2            |                             | _                                           |                                       | 27                              | 0           | —                    | Parallel Master Port address                                                                    |

| PMA3            |                             | _                                           | _                                     | 38                              | 0           | _                    | (Demultiplexed Master modes)                                                                    |

| PMA4            |                             | _                                           | _                                     | 37                              | 0           | _                    | 7                                                                                               |

| PMA5            |                             | _                                           | _                                     | 4                               | 0           | _                    |                                                                                                 |

| PMA6            |                             | _                                           | _                                     | 5                               | 0           | _                    | -                                                                                               |

| PMA7            |                             | _                                           | _                                     | 13                              | 0           | _                    | -                                                                                               |

| PMA8            |                             | _                                           | _                                     | 32                              | 0           | _                    | -                                                                                               |

| PMA9            |                             | _                                           | _                                     | 35                              | 0           | _                    | -                                                                                               |

| PMA10           |                             |                                             | _                                     | 12                              | 0           |                      | -                                                                                               |

| PMCS1           | 23                          | 26                                          | 29                                    | 15                              | 0           |                      | Parallel Master Port Chip Select 1 strob                                                        |

|                 | 20 <sup>(2)</sup>           | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup>                     | 10 <sup>(2)</sup>               | -           |                      | Parallel Master Port data (Demultiplexed                                                        |

| PMD0            | 1 <sup>(3)</sup>            | <br>4 <sup>(3)</sup>                        | 35 <sup>(3)</sup>                     | 21 <sup>(3)</sup>               | I/O         | TTL/ST               | Master mode) or address/data                                                                    |

|                 | 19(2)                       | 22(2)                                       | 25(2)                                 | <u>9</u> (2)                    |             |                      | (Multiplexed Master modes)                                                                      |

| PMD1            | 2(3)                        | 5 <sup>(3)</sup>                            | 36 <sup>(3)</sup>                     | 22 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

|                 | 18(2)                       | 21 <sup>(2)</sup>                           | 24 <sup>(2)</sup>                     | 8 <sup>(2)</sup>                |             |                      | -                                                                                               |

| PMD2            | <u></u>                     | 6 <sup>(3)</sup>                            | 1 <sup>(3)</sup>                      | 23(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD3            | 15                          | 18                                          | 19                                    | 1                               | I/O         | TTL/ST               | -                                                                                               |

| PMD4            | 10                          | 10                                          | 18                                    | 44                              | 1/O         | TTL/ST               | -                                                                                               |

| PMD5            | 13                          | 16                                          | 17                                    | 43                              | I/O         | TTL/ST               | -                                                                                               |

| PMD5<br>PMD6    | 12 <sup>(2)</sup>           | 15 <sup>(2)</sup>                           | 16 <sup>(2)</sup>                     | 43<br>42 <sup>(2)</sup>         | 1/0         | 111/31               | -                                                                                               |

| FIVIDO          | 28(3)                       | 3( <b>3</b> )                               | 34 <b>(3)</b>                         | 20(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD7            | <u>11(2)</u>                | 14(2)                                       | 15 <sup>(2)</sup>                     | 41 <sup>(2)</sup>               |             |                      | -                                                                                               |

| PINDI           | 27 <sup>(3)</sup>           | 2 <sup>(3)</sup>                            | 33( <b>3</b> )                        | 19 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

| PMRD            | 2/07                        | 24                                          | 27                                    | 19(1)                           | 0           |                      | Derellel Meeter Pert read stroke                                                                |

| PINIRD          | 21<br>22 <sup>(2)</sup>     | 24<br>25 <sup>(2)</sup>                     | 27<br>28 <sup>(2)</sup>               | 14 <sup>(2)</sup>               | 0           |                      | Parallel Master Port read strobe                                                                |

| PMWR            | <u></u><br>4 <sup>(3)</sup> | 25 <sup>(2)</sup><br>7 <sup>(3)</sup>       | 28 <sup>(-)</sup><br>2 <sup>(3)</sup> | 24 <sup>(3)</sup>               | 0           | —                    | Parallel Master Port write strobe                                                               |

| VBUS            | 12(3)                       | 15 <sup>(3)</sup>                           | 16 <sup>(3)</sup>                     | 42(3)                           |             | Analog               | USB bus power monitor                                                                           |

| VBUS<br>VUSB3V3 | 20(3)                       | 23(3)                                       | 26 <sup>(3)</sup>                     | 10 <sup>(3)</sup>               | P           | Analog               | USB internal transceiver supply. This pin                                                       |

| VUSBSVS         | 20.7                        | 23.7                                        | 20.7                                  | 10.7                            | Г           | _                    | must be connected to VDD.                                                                       |

| VBUSON          | 22 <sup>(3)</sup>           | 25 <sup>(3)</sup>                           | 28 <sup>(3)</sup>                     | 14 <sup>(3)</sup>               | 0           | _                    | USB Host and OTG bus power control output                                                       |

| D+              | 18 <sup>(3)</sup>           | 21 <sup>(3)</sup>                           | 24 <sup>(3)</sup>                     | 8 <sup>(3)</sup>                | I/O         | Analog               | USB D+                                                                                          |

| –<br>D-         | 19(3)                       | 22 <sup>(3)</sup>                           | 25 <sup>(3)</sup>                     | 9 <sup>(3)</sup>                | I/O         | Analog               | USB D-                                                                                          |

| Legend: C       | CMOS = CI<br>ST = Schm      | MOS compa<br>itt Trigger in<br>input buffer | atible input                          | or output                       |             | Analog =<br>O = Outp | Analog input P = Power                                                                          |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

## 8.1 Oscillator Control Regiters

| TAB                         | LE 8-1:                         | 09        | SCILLA | ATOR O | CONTR    | OL REG                                   | ISTER I                                                    | MAP   |          |      |         |                      |       |                     |      |                       |        |       |           |

|-----------------------------|---------------------------------|-----------|--------|--------|----------|------------------------------------------|------------------------------------------------------------|-------|----------|------|---------|----------------------|-------|---------------------|------|-----------------------|--------|-------|-----------|

| ess                         |                                 | 0         |        |        |          |                                          |                                                            |       |          |      | Bits    |                      |       |                     |      |                       |        |       | ú         |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14  | 29/13    | 28/12                                    | 27/11                                                      | 26/10 | 25/9     | 24/8 | 23/7    | 22/6                 | 21/5  | 20/4                | 19/3 | 18/2                  | 17/1   | 16/0  | All Reset |

| F000                        | OSCCON                          | 31:16     | —      | _      | Р        | LLODIV<2:0                               | :0> FRCDIV<2:0> — SOSCRDY PBDIVRDY PBDIV<1:0> PLLMULT<2:0> |       |          |      |         |                      | >     | x1xx <sup>(2)</sup> |      |                       |        |       |           |

| FUUU                        | 030001                          | 15:0      | —      |        | COSC<2:0 | V                                        | Ι                                                          |       | NOSC<2:0 | >    | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK | SLPEN               | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx(2)   |

| F010                        | OSCTUN                          | 31:16     | _      | _      |          | _                                        | _                                                          |       |          | _    | _       | _                    | _     | _                   |      | _                     | —      | _     | 0000      |

| 1010                        | 030101                          | 15:0      | _      | _      |          | _                                        | _                                                          |       |          | _    | _       | _                    |       |                     | TUN  | l<5:0>                |        |       | 0000      |

| 5000                        |                                 | 31:16     | _      |        |          |                                          |                                                            |       |          |      | RODIV<1 | 4:0>                 |       |                     |      |                       |        |       | 0000      |

| F020                        | REFOCON                         | 15:0      | ON     |        | SIDL     | SIDL OE RSLP - DIVSWEN ACTIVE ROSEL<3:0> |                                                            |       |          |      |         |                      |       | 0000                |      |                       |        |       |           |

| F000                        | DEFOTDIM                        | 31:16     |        |        |          | R                                        | OTRIM<8:0                                                  | )>    |          |      |         | _                    | _     | _                   | _    | _                     | _      | _     | 0000      |

| F030                        | REFOTRIM                        | 15:0      | _      | _      |          | _                                        | _                                                          |       |          | -    | _       | _                    | _     | _                   |      | _                     | —      | _     | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|----------------------|--------------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0                  | R/W-y                    | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |  |  |  |  |

| 31:24        | —                 | —                    | PLLODIV<2:0> FRCDIV<2:0> |                   |                   |                       |                  |                  |  |  |  |  |

| 00.40        | U-0               | R-0                  | R-1                      | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |  |  |  |  |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY                 | PBDI              | /<1:0>            | Р                     | LLMULT<2:0>      | •                |  |  |  |  |

| 45.0         | U-0               | R-0                  | R-0                      | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |  |  |  |  |

| 15:8         | —                 |                      | COSC<2:0>                |                   | —                 |                       | NOSC<2:0>        |                  |  |  |  |  |

| 7:0          | R/W-0             | R-0                  | R-0                      | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |  |  |  |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK                    | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |  |  |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | onfiguration bits on POR |                    |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi     | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

- bit 18-16 **PLLMULT<2:0>:** Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 = Clock is multiplied by 17

- 001 = Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (OSCCON<26:24>)

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x):

Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = The USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 =The USB PLL module is out of lock or USB PLL module start-up timer is in progress or the USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = The PLL module is in lock or PLL module start-up timer is satisfied

- 0 = The PLL module is out of lock, the PLL start-up timer is running, or the PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = The device will enter Sleep mode when a WAIT instruction is executed

- 0 = The device will enter Idle mode when a WAIT instruction is executed

- **Note 1:** This bit is only available on PIC32MX2XX devices.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- Low-Speed Host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

## TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | S    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5390                        | UIEF9                           | 15:0      |       |       | —     | —     | _     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

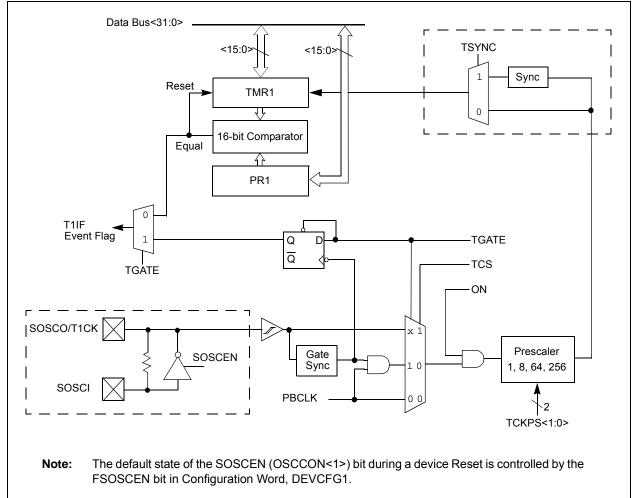

## 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 12-1 illustrates a general block diagram of Timer1.

## REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

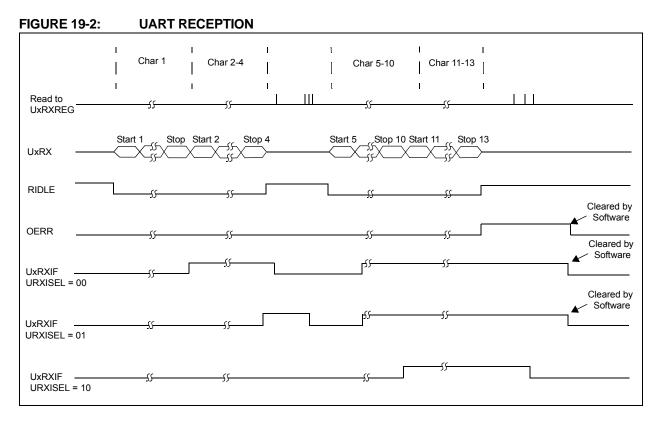

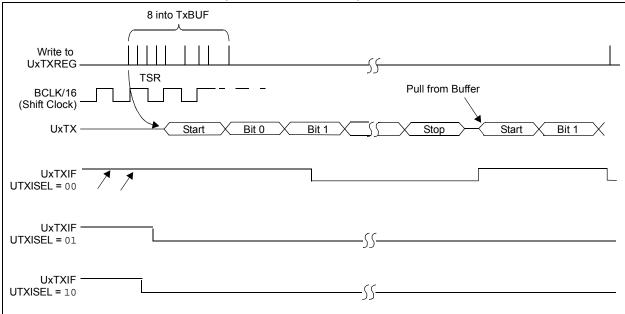

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | _                 | _                 | -                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | _                 | -                 | -                 | _                 | _                | —                |

| 45.0         | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | BUSY              | IRQM              | <1:0>             | INCM              | <1:0>             | _                 | MODE             | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAITB             | <1:0> <b>(1)</b>  |                   | WAITM             | <3:0>(1)          |                   | WAITE            | <1:0>(1)         |

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER

### Legend:

| 3                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

#### bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

#### bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 Unimplemented: Read as '0'

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMA<x:0>, and PMD<7:0>)

- 10 = Master mode 2 (PMCS1, PMRD, PMWR, PMA<x:0>, and PMD<7:0>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS1, PMD<7:0>, and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1, and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

### bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- . 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

## REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                     | —                      | _                 |                   | _                | —                |

| 22:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | -                     | —                      | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> |                   |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-1             | U-0               | U-1              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            |                   | _                | TDOEN            |

## **REGISTER 27-5: CFGCON: CONFIGURATION CONTROL REGISTER**

## Legend:

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 IOLOCK: Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed.

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed.

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed.

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed.

#### bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2-1 Unimplemented: Read as '1'

- bit 0 **TDOEN:** TDO Enable for 2-Wire JTAG bit

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

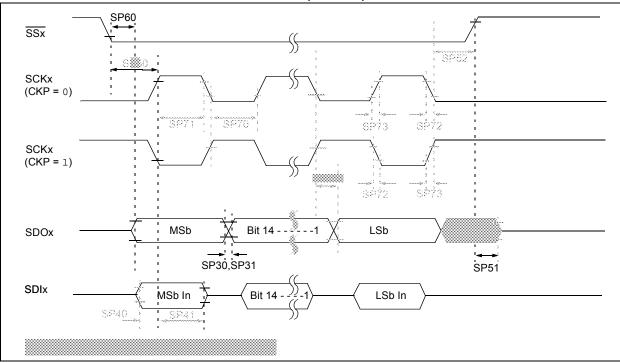

## FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                     |        |                        |      | 35°C for Industrial |                    |

|--------------------|-----------------------|---------------------------------------------------------------------------|--------|------------------------|------|---------------------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.   | Typical <sup>(2)</sup> | Max. | Units               | Conditions         |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)                                              | Tsck/2 | _                      | _    | ns                  | —                  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2 | —                      | _    | ns                  | —                  |

| SP72               | TscF                  | SCKx Input Fall Time                                                      | _      | 5                      | 10   | ns                  | —                  |

| SP73               | TscR                  | SCKx Input Rise Time                                                      | —      | 5                      | 10   | ns                  | —                  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —      | —                      | _    | ns                  | See parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —      | —                      | _    | ns                  | See parameter DO31 |

| SP35               | TscH2doV,             | SDOx Data Output Valid after                                              | _      | —                      | 20   | ns                  | VDD > 2.7V         |

|                    | TscL2DoV              | SCKx Edge                                                                 | _      | —                      | 30   | ns                  | VDD < 2.7V         |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10     | —                      | _    | ns                  | —                  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10     | —                      |      | ns                  | —                  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175    | —                      |      | ns                  | _                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

## TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА        | RACTERI | Standard Operating Conditions: 2.3V to 3.6VACTERISTICS(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Indu |         |         |          |       |                               |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|----------|-------|-------------------------------|

| Param.<br>No. | Symbol  | Characteristics                                                                                                                                          | Min.    | Typical | Max.     | Units | Conditions                    |

| MOS10         |         | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                                                                       | DC<br>4 |         | 50<br>50 |       | EC (Note 2)<br>ECPLL (Note 1) |

Note 1: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

**2:** This parameter is characterized, but not tested in manufacturing.

## TABLE 31-6:SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS | Standard Operating Conditions: 2.3V to 3.6VCTERISTICS(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for |                                    |   |   |    |            |

|---------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---|---|----|------------|

| Param.<br>No. | Symbol    | Characteristics                                                                                                                                | Min. Typical Max. Units Conditions |   |   |    | Conditions |

| MSP10         | TscL      | SCKx Output Low Time<br>(Note 1,2)                                                                                                             | Тѕск/2                             |   | — | ns | _          |

| MSP11         | TscH      | SCKx Output High Time (Note 1,2)                                                                                                               | Тѕск/2                             | _ | _ | ns | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

## TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                 |   |   |            |   |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---|---|------------|---|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                                                                                                  | Min. Typ. Max. Units Conditions |   |   | Conditions |   |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2)                                                                                                              | Тѕск/2                          | _ | _ | ns         | _ |

| MSP11              | TSCH   | SCKx Output High Time<br>(Note 1,2)                                                                                                             | Тѕск/2                          | _ | _ | ns         | — |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

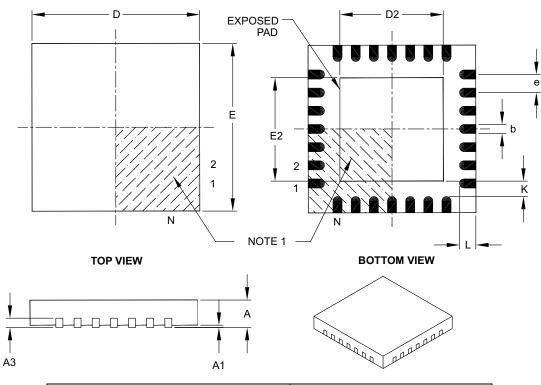

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units      | nits MILLIMETERS |          |      |

|------------------------|------------|------------------|----------|------|

| Dimens                 | ion Limits | MIN              | NOM      | MAX  |

| Number of Pins         | Ν          | 28               |          |      |

| Pitch                  | е          |                  | 0.65 BSC |      |

| Overall Height         | А          | 0.80             | 0.90     | 1.00 |

| Standoff               | A1         | 0.00             | 0.02     | 0.05 |

| Contact Thickness      | A3         | 0.20 REF         |          |      |

| Overall Width          | E          | 6.00 BSC         |          |      |

| Exposed Pad Width      | E2         | 3.65 3.70 4.20   |          |      |

| Overall Length         | D          | 6.00 BSC         |          |      |

| Exposed Pad Length     | D2         | 3.65             | 3.70     | 4.20 |

| Contact Width          | b          | 0.23             | 0.30     | 0.35 |

| Contact Length         | L          | 0.50             | 0.55     | 0.70 |

| Contact-to-Exposed Pad | К          | 0.20             | -        | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

# APPENDIX A: REVISION HISTORY

## Revision A (May 2011)

This is the initial released version of this document.

## **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX130F064C

- PIC32MX130F064D

- PIC32MX150F128B

- PIC32MX150F128CPIC32MX150F128D

- PIC32MX250F128C

PIC32MX250F128D

PIC32MX230F064B

PIC32MX230F064C

PIC32MX230F064D

PIC32MX250F128B

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

| Section                                                                    | Update Description                                                                                                                                                        |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |

| and Graphics Interfaces, USB, and Advanced Analog"                         | Added the SPDIP package reference (see Table 1, Table 2, and " <b>Pin Diagrams</b> ").                                                                                    |

|                                                                            | Added the new devices to the applicable pin diagrams.                                                                                                                     |

|                                                                            | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |

| 1.0 "Device Overview"                                                      | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |

|                                                                            | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"          | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |

## TABLE A-1: MAJOR SECTION UPDATES

## **Revision E (October 2012)**

All singular pin diagram occurrences of CVREF were changed to: CVREFOUT. In addition, minor text and formatting changes were incorporated throughout the document.

All major changes are referenced by their respective section in Table A-4.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                                | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>128 KB Flash and 32 KB SRAM)<br>with Audio and Graphics<br>Interfaces, USB, and Advanced<br>Analog" | <ul> <li>Updated the following feature sections:</li> <li>"Operating Conditions"</li> <li>"Communication Interfaces"</li> </ul>                                                                                                                                                                                                                                                                                                             |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | Removed Section 2.8 "Configuration of Analog and Digital Pins During ICSP Operations".                                                                                                                                                                                                                                                                                                                                                      |

| 3.0 "CPU"                                                                                                                              | Removed references to GPR shadow registers in <b>3.1 "Features"</b> and <b>3.2.1 "Execution Unit"</b> .                                                                                                                                                                                                                                                                                                                                     |

| 4.0 "Memory Organization"                                                                                                              | Updated the BRG bit range in the SPI1 and SPI2 Register Map (see Table 4-8).<br>Added the PWP<6> bit to the Device Configuration Word Summary<br>(see Table 4-17).                                                                                                                                                                                                                                                                          |

| 5.0 "Flash Program Memory"                                                                                                             | Added a note with Flash page size and row size information.                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.0 "Interrupt Controller"                                                                                                             | Updated the TPC<2:0> bit definitions (see Register 7-1).<br>Updated the IPTMR<31:0> bit definition (see Register 7-3).                                                                                                                                                                                                                                                                                                                      |

| 8.0 "Oscillator Configuration"                                                                                                         | Updated the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).<br>Updated the RODIV<14:0> bit definitions (see Register 8-3).                                                                                                                                                                                                                                                                                                            |