Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| roduct Status             | Active                                                                         |

|                           |                                                                                |

| ore Processor             | MIPS32® M4K™                                                                   |

| ore Size                  | 32-Bit Single-Core                                                             |

| peed                      | 40MHz                                                                          |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| eripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| umber of I/O              | 33                                                                             |

| rogram Memory Size        | 128KB (128K x 8)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 32K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 13x10b                                                                     |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type              | Surface Mount                                                                  |

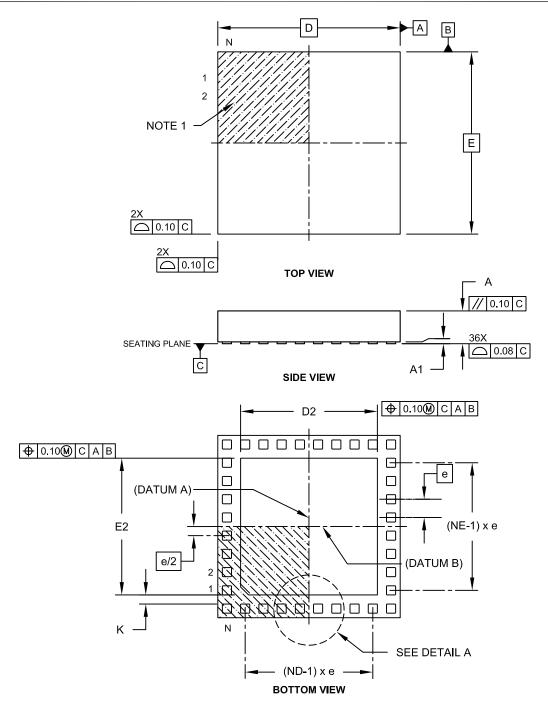

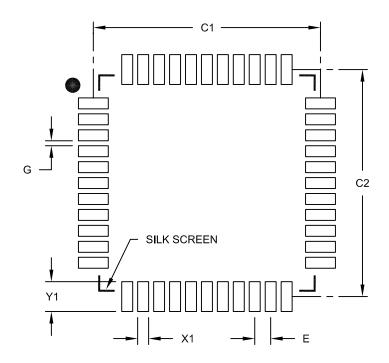

| ackage / Case             | 44-TQFP                                                                        |

| upplier Device Package    | 44-TQFP (10x10)                                                                |

| ırchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128d-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

28-PIN QFN (TOP VIEW)(1,2,3.4)

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

28

1

| Pin # | Full Pin Name                         |

|-------|---------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    |

| 5     | Vss                                   |

| 6     | OSC1/CLKI/RPA2/RA2                    |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3               |

| 8     | SOSCI/RPB4/RB4                        |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        |

| 10    | VDD                                   |

| 11    | PGED3/RPB5/PMD7/RB5                   |

| 12    | PGEC3/RPB6/PMD6/RB6                   |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7          |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8         |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 16   | Vss                                            |

| 17   | VCAP                                           |

| 18   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 19   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 20   | AN12/PMD0/RB12                                 |

| 21   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 22   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 24   | AVss                                           |

| 25   | AVDD                                           |

| 26   | MCLR                                           |

| 27   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 28   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IABLE I-I |                   | Pin Nu                            |                   |                                 | I/O     TTL/ST     Parallel Master Port data (Demultiplexed Master mode) or address/data (Multiplexed Master modes)       I/O     TTL/ST       O     —       Parallel Master Port read strobe |          |                                                                     |  |  |  |  |

|-----------|-------------------|-----------------------------------|-------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------|--|--|--|--|

| Pin Name  | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA    | 44-pin<br>QFN/<br>TQFP/<br>VTLA |                                                                                                                                                                                                                                                                                                                             |          | ·                                                                   |  |  |  |  |

| PMA0      | 7                 | 10                                | 8                 | 3                               |                                                                                                                                                                                                                                                                                                                             |          | (Buffered Slave modes) and output (Master modes)                    |  |  |  |  |

| PMA1      | 9                 | 12                                | 10                | 2                               | I/O                                                                                                                                                                                                                                                                                                                         | TTL/ST   | (Buffered Slave modes) and output                                   |  |  |  |  |

| PMA2      |                   | _                                 | _                 | 27                              | 0                                                                                                                                                                                                                                                                                                                           | _        |                                                                     |  |  |  |  |

| PMA3      |                   | _                                 | _                 | 38                              | 0                                                                                                                                                                                                                                                                                                                           | _        | (Demultiplexed Master modes)                                        |  |  |  |  |

| PMA4      |                   | _                                 | _                 | 37                              | 0                                                                                                                                                                                                                                                                                                                           | _        |                                                                     |  |  |  |  |

| PMA5      |                   | _                                 | _                 | 4                               | 0                                                                                                                                                                                                                                                                                                                           | _        |                                                                     |  |  |  |  |

| PMA6      |                   | _                                 | _                 | 5                               | 0                                                                                                                                                                                                                                                                                                                           | _        |                                                                     |  |  |  |  |

| PMA7      |                   | _                                 |                   | 13                              | 0                                                                                                                                                                                                                                                                                                                           | _        | 1                                                                   |  |  |  |  |

| PMA8      |                   | _                                 |                   | 32                              | 0                                                                                                                                                                                                                                                                                                                           | _        | 1                                                                   |  |  |  |  |

| PMA9      |                   | _                                 | _                 | 35                              | 0                                                                                                                                                                                                                                                                                                                           | _        | †                                                                   |  |  |  |  |

| PMA10     |                   | _                                 | _                 | 12                              | 0                                                                                                                                                                                                                                                                                                                           | _        | †                                                                   |  |  |  |  |

| PMCS1     | 23                | 26                                | 29                | 15                              | 0                                                                                                                                                                                                                                                                                                                           | _        | Parallel Master Port Chip Select 1 strobe                           |  |  |  |  |

| PMD0 -    | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                 | 26 <sup>(2)</sup> | 10 <sup>(2)</sup>               | 1/0                                                                                                                                                                                                                                                                                                                         | TTL /OT  | Parallel Master Port data (Demultiplexed                            |  |  |  |  |

|           | 1 <sup>(3)</sup>  | 4 <sup>(3)</sup>                  | 35(3)             | 21 <sup>(3)</sup>               | 1/0                                                                                                                                                                                                                                                                                                                         | 1111/51  | 1                                                                   |  |  |  |  |

| DMD4      | 19 <sup>(2)</sup> | 22(2)                             | 25 <sup>(2)</sup> | 9(2)                            | 1/0                                                                                                                                                                                                                                                                                                                         | TTI (OT  | (Multiplexed Master modes)                                          |  |  |  |  |

| PMD1      | 2 <sup>(3)</sup>  | 5(3)                              | 36 <sup>(3)</sup> | 22 <sup>(3)</sup>               | 1/0                                                                                                                                                                                                                                                                                                                         | TIL/SI   | •                                                                   |  |  |  |  |

| DMDO      | 18 <sup>(2)</sup> | 21 <sup>(2)</sup>                 | 24 <sup>(2)</sup> | 8(2)                            | 1/0                                                                                                                                                                                                                                                                                                                         | TTI (OT  |                                                                     |  |  |  |  |

| PMD2      | 3(3)              | 6(3)                              | 1(3)              | 23(3)                           | 1/0                                                                                                                                                                                                                                                                                                                         | IIL/SI   |                                                                     |  |  |  |  |

| PMD3      | 15                | 18                                | 19                | 1                               | I/O                                                                                                                                                                                                                                                                                                                         | TTL/ST   |                                                                     |  |  |  |  |

| PMD4      | 14                | 17                                | 18                | 44                              | I/O                                                                                                                                                                                                                                                                                                                         | TTL/ST   | †                                                                   |  |  |  |  |

| PMD5      | 13                | 16                                | 17                | 43                              | I/O                                                                                                                                                                                                                                                                                                                         | TTL/ST   | †                                                                   |  |  |  |  |

| PMD6      | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup> | 42 <sup>(2)</sup>               |                                                                                                                                                                                                                                                                                                                             |          | 1                                                                   |  |  |  |  |

|           | 28(3)             | <b>3(3)</b>                       | 34(3)             | 20(3)                           | 1/0                                                                                                                                                                                                                                                                                                                         | TIL/ST   |                                                                     |  |  |  |  |

| PMD7      | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup> | 41 <sup>(2)</sup>               | 1/0                                                                                                                                                                                                                                                                                                                         | TTI (0.T | †                                                                   |  |  |  |  |

|           | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)             | 19 <sup>(3)</sup>               | 1/0                                                                                                                                                                                                                                                                                                                         | IIL/SI   |                                                                     |  |  |  |  |

| PMRD      | 21                | 24                                | 27                | 11                              | 0                                                                                                                                                                                                                                                                                                                           | _        | Parallel Master Port read strobe                                    |  |  |  |  |

|           | 22 <sup>(2)</sup> | 25 <sup>(2)</sup>                 | 28 <sup>(2)</sup> | 14 <sup>(2)</sup>               |                                                                                                                                                                                                                                                                                                                             |          |                                                                     |  |  |  |  |

| PMWR      | <sub>4</sub> (3)  | 7 <sup>(3)</sup>                  | 2 <sup>(3)</sup>  | 24 <sup>(3)</sup>               | 0                                                                                                                                                                                                                                                                                                                           | _        | Parallel Master Port write strobe                                   |  |  |  |  |

| VBUS      | 12 <sup>(3)</sup> | 15 <sup>(3)</sup>                 | 16 <sup>(3)</sup> | 42(3)                           | I                                                                                                                                                                                                                                                                                                                           | Analog   | USB bus power monitor                                               |  |  |  |  |

| VUSB3V3   | 20 <sup>(3)</sup> | 23 <sup>(3)</sup>                 | 26 <sup>(3)</sup> | 10 <sup>(3)</sup>               | Р                                                                                                                                                                                                                                                                                                                           | _        | USB internal transceiver supply. This pin must be connected to VDD. |  |  |  |  |

| VBUSON    | 22 <sup>(3)</sup> | 25 <sup>(3)</sup>                 | 28 <sup>(3)</sup> | 14 <sup>(3)</sup>               | 0                                                                                                                                                                                                                                                                                                                           | _        | USB Host and OTG bus power control output                           |  |  |  |  |

| D+        | 18 <sup>(3)</sup> | 21 <sup>(3)</sup>                 | 24 <sup>(3)</sup> | 8(3)                            | I/O                                                                                                                                                                                                                                                                                                                         | Analog   | USB D+                                                              |  |  |  |  |

| D-        | 19 <sup>(3)</sup> | 22 <sup>(3)</sup>                 | 25 <sup>(3)</sup> | 9(3)                            | I/O                                                                                                                                                                                                                                                                                                                         | Analog   | USB D-                                                              |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

P = Power

TTL = TTL input buffer

O = Output

I = Input

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

PPS = Peripheral Pin Select — = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

| F         | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Exception | Description                                                                                                                             |

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a Corextend instruction when Corextend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

#### 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

# 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see **Section 26.0** "Power-Saving Features".

#### 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

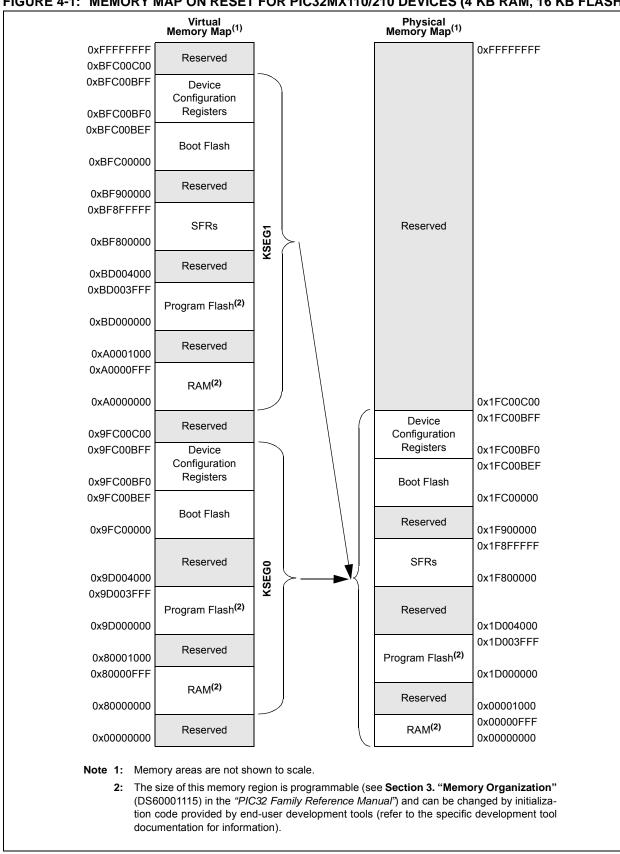

FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX110/210 DEVICES (4 KB RAM, 16 KB FLASH)

#### 4.2 Bus Matrix Control Registers

#### TABLE 4-2: BUS MATRIX REGISTER MAP

| ess                         |                         | ø.                              |                     |                     |       |       |       |       |      |      |      | Bits         |      |           |           |           |          |          |               |

|-----------------------------|-------------------------|---------------------------------|---------------------|---------------------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|----------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range                       | 31/15               | 30/14               | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1     | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16                           | _                   |                     | _     | _     | _     | _     |      | _    |      | _            | _    | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS | BMXERRIS | 001F          |

| 2000                        | PINIYCOM, ,             | 15:0 — — — — — — BMXWSDRM — — — |                     |                     |       |       |       |       |      |      | В    | MXARB<2:0>   |      | 0041      |           |           |          |          |               |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16                           | _                   | _                   | _     | _     | _     | _     |      | _    | -    | _            | _    | _         | _         | _         | _        | _        | 0000          |

| 2010                        | BIVINDREBA              | 15:0                            |                     |                     |       |       |       |       |      |      | BM   | XDKPBA<15:0  | >    |           |           |           |          |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16                           | _                   | _                   | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         | _         | _         | _        | _        | 0000          |

| 2020                        | DIVINDODDA              | 15:0                            | BMXDUDBA<15:0> 0000 |                     |       |       |       |       |      |      |      |              |      |           |           | 0000      |          |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16                           | _                   | _                   | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         | _         | _         | _        | _        | 0000          |

|                             |                         | 15:0                            |                     | BMXDUPBA<15:0> 0000 |       |       |       |       |      |      |      |              |      |           |           | 0000      |          |          |               |

| 2040                        | BMXDRMSZ                | 31:16                           | BMXDRMSZ<31:0>      |                     |       |       |       |       |      |      |      |              |      |           |           |           | xxxx     |          |               |

|                             |                         | 15:0                            |                     |                     | ı     |       | ı     |       |      | ı    |      |              | ı    |           | 1         |           |          |          | XXXX          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16                           | _                   | _                   | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         |           | BMXPUPB/  | \<19:16> |          | 0000          |

|                             |                         | 15:0                            |                     |                     |       |       |       |       |      |      | BM   | XPUPBA<15:0  | >    |           |           |           |          |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16                           |                     |                     |       |       |       |       |      |      | BM   | XPFMSZ<31:0  | >    |           |           |           |          |          | XXXX          |

|                             |                         | 15:0                            |                     |                     |       |       |       |       |      |      |      |              |      |           |           |           |          |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16                           |                     |                     |       |       |       |       |      |      | BMX  | (BOOTSZ<31:0 | )>   |           |           |           |          |          | 0000          |

|                             | , , , ,                 | 15:0                            |                     |                     |       |       |       |       |      |      |      |              |      |           |           |           |          |          | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31:24        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 31.24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7:0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMK              | EY<7:0>           |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

#### REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | NVMADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | NVMADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | NVMADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMAD             | DR<7:0>           |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 NVMADDR<31:0>: Flash Address bits

Bulk/Chip/PFM Erase: Address is ignored.

Page Erase: Address identifies the page to erase.

Row Program: Address identifies the row to program.

Word Program: Address identifies the word to program.

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0                          |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|-------------------------------------------|

| 24.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0                                     |

| 31:24        |                   |                       | BYTO              | <1:0>             | WBO <sup>(1)</sup> | -                 | _                | BITO                                      |

| 22.46        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0                                       |

| 23:16        | _                 | _                     | _                 | _                 | _                  | _                 | _                | 24/16/8/0  R/W-0  BITO  U-0  R/W-0  R/W-0 |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0                                     |

| 15:8         | _                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                                           |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0                                     |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       | •                                         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

- bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit (1)

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) =  $\underline{1}$  (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 PLEN<4:0>: Polynomial Length bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

These bits are unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Denotes the length of the polynomial – 1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| ▢             |

|---------------|

| DS60001       |

| O             |

| 0             |

| 0             |

| 0             |

| _             |

| $\rightarrow$ |

| 168J-         |

| ω             |

| <u>_</u>      |

| <u> </u>      |

| page          |

| Æ             |

| ×             |

| ťν            |

| _             |

| 135           |

| č             |

| ٠.            |

|               |

|               |

| TABLE 11-5: | PORTC REGISTER MA | 0 |

|-------------|-------------------|---|

| IADLE II-J. | PURIUREGISTER WA  | _ |

| ess                         | Register<br>Name <sup>(1,2)</sup> | 0         |       |       |       |       |       |       |          |                       |                         | Bits                    |                         |                       |                      |                         |          |          | 10         |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-------------------------|-------------------------|-----------------------|----------------------|-------------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) |                                   | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                    | 21/5                    | 20/4                  | 19/3                 | 18/2                    | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     | ı     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | ı        | ı        | 0000       |

| 0200                        | ANSELC                            | 15:0      | -     | _     | _     | _     | _     | _     | _        | -                     | _                       | _                       | _                       | _                     | ANSC3 <sup>(4)</sup> | ANSC2 <sup>(3)</sup>    | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       | _                       | _                       |                       | _                    | _                       | _        | _        | 0000       |

| 0210                        | TRISC                             | 15:0      | I     | _     | _     | _     | _     |       | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup>   | TRISC5 <sup>(3)</sup>   | TRISC4 <sup>(3)</sup> | TRISC3               | TRISC2 <sup>(3)</sup>   | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       |                       |                      |                         |          |          | 0000       |

| 0220                        | PORTC                             | 15:0      | I     | _     | _     | _     | _     | _     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>      | RC5 <sup>(3)</sup>      | RC4 <sup>(3)</sup>    | RC3                  | RC2 <sup>(3)</sup>      | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0230                        | LKI                               | 15:0      | I     | _     | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>    | LATC5 <sup>(3)</sup>    | LATC4 <sup>(3)</sup>  | LATC3                | LATC2 <sup>(3)</sup>    | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0240                        | ODCC                              | 15:0      | _     | _     | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>    | ODCC5 <sup>(3)</sup>    | ODCC4 <sup>(3)</sup>  | ODCC3                | ODCC2 <sup>(3)</sup>    | ODCC1    | ODCC0    | 0000       |

| 6250                        | CNPUC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0250                        | CNPUC                             | 15:0      | I     | _     | _     | _     | _     | _     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup>   | CNPUC5 <sup>(3)</sup>   | CNPUC4 <sup>(3)</sup> | CNPUC3               | CNPUC2 <sup>(3)</sup>   | CNPUC1   | CNPUC0   | 0000       |

| 0000                        | CNIDDO                            | 31:16     | _     | _     | _     | _     | _     | _     | _        | _                     | _                       | _                       | _                       | _                     | _                    | _                       | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | _     | _     | _     | _     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup>   | CNPDC5 <sup>(3)</sup>   | CNPDC4 <sup>(3)</sup> | CNPDC3               | CNPDC2 <sup>(3)</sup>   | CNPDC1   | CNPDC0   | 0000       |

| 6070                        | CNICONIC                          | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 6200                        | CNENC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        |                       | _                       | _                       | _                       |                       | _                    | _                       | _        |          | 0000       |

| 6280                        | CNENC                             | 15:0      | I     | _     | _     | _     | _     | _     | CNIEC9   | CNIEC8 <sup>(3)</sup> | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)               | CNIEC5 <sup>(3)</sup>   | CNIEC4 <sup>(3)</sup> | CNIEC3               | CNIEC2 <sup>(3)</sup>   | CNIEC1   | CNIEC0   | 0000       |

| 6200                        | CNICTATO                          | 31:16     | I     | _     | _     | _     | _     | _     | _        |                       | _                       |                         | _                       |                       | _                    | _                       | _        |          | 0000       |

| 0290                        | CNSTATC                           | 15:0      |       | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6 <sup>(3)</sup> | CNSTATC5 <sup>(3)</sup> | CNSTATC4(3)           | CNSTATC3             | CNSTATC2 <sup>(3)</sup> | CNSTATC1 | CNSTATCO | 0000       |

${f x}$  = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for

- PORTC is not available on 28-pin devices. 2:

- This bit is only available on 44-pin devices.

- This bit is only available on USB-enabled devices with 36 or 44 pins.

**TABLE 11-6:** PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAU4                        | INTIK            | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17100                       | IIVIZIX          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17.00                       | IIIII            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| FA10                        | INT4R            | 31:16     |       |       | _     | _     | _     |       |      |      |      | _    |      |      | _    | _     | _      | _    | 0000       |

| .,                          |                  | 15:0      |       |       |       | _     | _     |       |      |      |      | _    |      |      |      | INT4F | R<3:0> | ı    | 0000       |

| FA18                        | T2CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CKI | R<3:0> |      | 0000       |

| FA1C                        | T3CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       | _     | _     | _     | _     | _     |      |      |      | _    |      |      |      | T3CKI | R<3:0> | ı    | 0000       |

| FA20                        | T4CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T4CKI | R<3:0> |      | 0000       |

| FA24                        | T5CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CKI | R<3:0> |      | 0000       |

| FA28                        | IC1R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

| FA2C                        | IC2R             | 31:16     |       |       | _     | _     | _     | _     |      |      |      | _    |      |      |      | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IC3R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R             | 31:16     | _     | _     | _     |       | _     | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       | _     | _     |      | _    | _    | _    | _    | _    |      | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R             | 31:16     | _     | _     | _     |       | _     | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     |       | _     | _     |      | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

| FA48                        | OCFAR            | 31:16     |       |       | _     |       | _     |       |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA4C                        | OCFBR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16     |       |       | _     | _     | _     |       |      |      |      | _    |      |      | _    | _     | _      | _    | 0000       |

| FA50                        | UIKXK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| sss                         | Register<br>Name     |               |       |       |       |       |       |       |      | Ві   | ts   |      |      |      |           |           |          |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|-----------|-----------|----------|------|------------|

| Virtual Address<br>(BF80_#) |                      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3      | 18/2      | 17/1     | 16/0 | All Resets |

| FB00                        | RPA0R                | 31:16<br>15:0 | _     |       | _     |       |       |       | _    |      |      | _    | _    | _    | -         | —<br>RPA0 | -        | _    | 0000       |

|                             |                      | 31:16         |       |       |       |       |       |       |      |      |      |      |      | _    | _         | _         | _        | _    | 0000       |

| FB04                        | RPA1R                | 15:0          | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    |           | RPA1      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     |       | _     |       | _     | _     | _    | _    |      | _    | _    | _    |           | _         |          | _    | 0000       |

| FB08                        | RPA2R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPA2      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _         | _         | _        | _    | 0000       |

| FB0C                        | RPA3R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPA3      | <3:0>    |      | 0000       |

| ED40                        | DDA 4D               | 31:16         | _     |       | _     |       | _     |       | _    | _    | 1    | _    | _    | _    | -         | _         | _        | _    | 0000       |

| FB10                        | FB10 RPA4R           | 15:0          | _     |       | _     | _     | _     |       | _    | _    | _    | _    | _    | _    |           | RPA4      | <3:0>    |      | 0000       |

| FB20                        | RPA8R <sup>(1)</sup> | 31:16         | _     | -     | _     | -     | _     | -     | _    | _    | 1    | _    | _    | _    | -         | _         | _        | _    | 0000       |

| 1 020                       | IN AOIN.             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPA8      | <3:0>    |      | 0000       |

| FB24                        | RPA9R <sup>(1)</sup> | 31:16         | _     |       | _     |       | _     |       | _    | _    |      | _    | _    | _    | -         | _         | _        | _    | 0000       |

|                             |                      | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPA9      | <3:0>    |      | 0000       |

| FB2C                        | RPB0R                | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _         |           |          | _    | 0000       |

|                             |                      | 15:0          |       |       | _     |       |       |       |      |      |      |      |      |      |           | RPB0      |          |      | 0000       |

| FB30                        | RPB1R                | 31:16<br>15:0 |       |       | _     |       |       |       |      |      |      |      |      |      |           | RPB1      | -2:0>    | _    | 0000       |

|                             |                      | 31:16         |       |       | _     |       |       |       |      |      |      | _    | _    | _    | _         | — KFB1    | <u> </u> | _    | 0000       |

| FB34                        | RPB2R                | 15:0          | _     |       |       |       |       |       |      |      |      | _    | _    |      |           | RPB2      |          | _    | 0000       |

|                             |                      | 31:16         | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _         | _         | _        | l _  | 0000       |

| FB38                        | RPB3R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPB3      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _         | _         | _        | _    | 0000       |

| FB3C                        | RPB4R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | RPB4      | <3:0>    |      | 0000       |

| ED 40                       | DDDCD                | 31:16         | _     |       | _     | -     | _     |       | _    | _    | 1    | _    | _    | _    | -         | _         | _        | _    | 0000       |

| FB40                        | RPB5R                | 15:0          | _     |       | _     |       | _     | -     | _    | _    |      | _    | _    | _    |           | RPB5      | <3:0>    |      | 0000       |

| FB44                        | RPB6R <sup>(2)</sup> | 31:16         | -     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _         | _         | _        | _    | 0000       |

| 1 044                       | INF DOIN, 7          | 15:0          | _     | 1     | _     | 1     | -     | 1     | -    | -    | 1    | _    | _    | _    | RPB6<3:0> |           |          |      | 0000       |

| FB48                        | RPB7R                | 31:16         | _     |       | _     |       | _     |       | _    | _    |      | _    | _    | _    | _         | _         | _        | _    | 0000       |

| . 2 .0                      | KPB/K                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |           | RPB7      | <3:0>    |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register is only available on 44-pin devices. Note 1:

This register is only available on PIC32MX1XX devices. 2:

This register is only available on 36-pin and 44-pin devices.

#### REGISTER 13-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 Unimplemented: Read as '0'

bit 1 **TCS**: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

#### REGISTER 17-1: SPIXCON: SPI CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | )>                    |

| 22.40        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | _                  | _                 | _                 | _                 | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | _                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FRMEN: Framed SPI Support bit

1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

bit 30 FRMSYNC: Frame Sync Pulse Direction Control on SSx pin bit (Framed SPI mode only)

1 = Frame sync pulse input (Slave mode)

0 = Frame sync pulse output (Master mode)

bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

1 = Frame pulse is active-high

0 = Frame pulse is active-low

bit 28 MSSEN: Master Mode Slave Select Enable bit

1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

0 = Slave select SPI support is disabled.

bit 27 FRMSYPW: Frame Sync Pulse Width bit

1 = Frame sync pulse is one character wide

0 = Frame sync pulse is one clock wide

bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

111 = Reserved; do not use

110 = Reserved; do not use

101 = Generate a frame sync pulse on every 32 data characters

100 = Generate a frame sync pulse on every 16 data characters

011 = Generate a frame sync pulse on every 8 data characters

010 = Generate a frame sync pulse on every 4 data characters

001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

1 = REFCLK is used by the Baud Rate Generator

0 = PBCLK is used by the Baud Rate Generator

bit 22-18 Unimplemented: Read as '0'

Note 1: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit can only be written when the ON bit = 0.

3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

**4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### REGISTER 17-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 DISSDI: Disable SDI bit

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 13.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended