Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128d-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 External Oscillator Pins

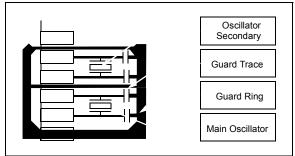

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

# 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |  |  |  |  |

|---------------------------|-----------|-----------------|--|--|--|--|

| Peripheral                | Base      | Offset<br>Start |  |  |  |  |

| Watchdog Timer            |           | 0x0000          |  |  |  |  |

| RTCC                      |           | 0x0200          |  |  |  |  |

| Timer1-5                  |           | 0x0600          |  |  |  |  |

| Input Capture 1-5         |           | 0x2000          |  |  |  |  |

| Output Compare 1-5        |           | 0x3000          |  |  |  |  |

| IC1 and IC2               |           | 0x5000          |  |  |  |  |

| SPI1 and SPI2             |           | 0x5800          |  |  |  |  |

| UART1 and UART2           |           | 0x6000          |  |  |  |  |

| PMP                       |           | 0x7000          |  |  |  |  |

| ADC                       | 0xBF80    | 0x9000          |  |  |  |  |

| CVREF                     |           | 0x9800          |  |  |  |  |

| Comparator                |           | 0xA000          |  |  |  |  |

| CTMU                      |           | 0xA200          |  |  |  |  |

| Oscillator                |           | 0xF000          |  |  |  |  |

| Device and Revision ID    |           | 0xF220          |  |  |  |  |

| Peripheral Module Disable |           | 0xF240          |  |  |  |  |

| Flash Controller          |           | 0xF400          |  |  |  |  |

| Reset                     |           | 0xF600          |  |  |  |  |

| PPS                       |           | 0xFA04          |  |  |  |  |

| Interrupts                |           | 0x1000          |  |  |  |  |

| Bus Matrix                |           | 0x2000          |  |  |  |  |

| DMA                       | 0xBF88    | 0x3000          |  |  |  |  |

| USB                       |           | 0x5050          |  |  |  |  |

| PORTA-PORTC               |           | 0x6000          |  |  |  |  |

| Configuration             | 0xBFC0    | 0x0BF0          |  |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |  |  |  |  |  |

| 7.0          | U-0 U-0           |                   | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | _                 | —                 |                      | —                     | NVMOP<3:0>             |                   |                  |                  |  |  |  |  |  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |  |  |  |  |  |

### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |

|--------------|-------------------|----------------------|-------------------|-------------------|---------------------|-----------------------|------------------|------------------|--|--|--|--|--|--|--|--|

| 24.24        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y               | R/W-0                 | R/W-0            | R/W-1            |  |  |  |  |  |  |  |  |

| 31:24        | —                 | —                    | Р                 | LLODIV<2:0        | 0> FRCDIV<2:0>      |                       |                  |                  |  |  |  |  |  |  |  |  |

| 00.40        | U-0               | R-0                  | R-1 R/W-y         |                   | R/W-y               | R/W-y                 | R/W-y            |                  |  |  |  |  |  |  |  |  |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI              | /<1:0> PLLMULT<2:0> |                       |                  |                  |  |  |  |  |  |  |  |  |

| 45.0         | U-0               | R-0                  | R-0 R-0           |                   | U-0                 | R/W-y R/W-y           |                  | R/W-y            |  |  |  |  |  |  |  |  |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                   | NOSC<2:0>             |                  |                  |  |  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R-0                  | R-0 R/W-0         |                   | R/W-0               | R/W-0                 | R/W-y            | R/W-0            |  |  |  |  |  |  |  |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                  | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |  |  |  |  |  |  |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | onfiguration bits on POR |                                    |  |  |  |  |  |

|-------------------|-----------------------|--------------------------|------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi     | U = Unimplemented bit, read as '0' |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown                 |  |  |  |  |  |

### bit 31-30 **Unimplemented:** Read as '0'

### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP

| ess                         |                                 |           |             |             |            |             |             |            |            | Bi          | its     |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------------|-------------|------------|-------------|-------------|------------|------------|-------------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15       | 30/14       | 29/13      | 28/12       | 27/11       | 26/10      | 25/9       | 24/8        | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                        | DCH0CON                         | 31:16     | _           | _           | _          | —           | _           |            | _          | —           | _       | _      | _      | —      | _       | _      |        | -      | 0000       |

| 3000                        | DCHUCON                         | 15:0      | CHBUSY      | _           | —          | —           | —           |            | —          | CHCHNS      | CHEN    | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16     | _           | _           | —          |             |             | _          | —          | —           |         | •      |        | CHAIR  | Q<7:0>  |        |        |        | 00FF       |

| 3070                        | DOINCON                         | 15:0      |             |             |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | _      |        | FF00       |

| 3080                        | DCH0INT                         | 31:16     | —           | _           | —          | —           | —           | _          | —          | —           | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5000                        | DCHOINT                         | 15:0      | _           | _           | —          | —           | —           | _          | —          | —           | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16     |             |             |            |             |             |            |            | СНАЗА       | <31.0>  |        |        |        |         |        |        |        | 0000       |

| 0000                        | Donooon                         | 15:0      |             | CHSSA<31:0> |            |             |             |            |            |             |         |        |        |        |         |        |        |        |            |

| 3040                        | DCH0DSA                         | 31:16     | CHDSA<31:0> |             |            |             |             |            |            |             |         |        |        |        |         | 0000   |        |        |            |

| 3070                        | DOI 10DOA                       | 15:0      | 0000        |             |            |             |             |            |            |             |         |        |        |        | 0000    |        |        |        |            |

| 30B0 DCH0SSIZ 31:16         |                                 |           |             |             |            |             |             |            |            | —           | —       | —      | —      | 0000   |         |        |        |        |            |

| 0000                        | 15:0 CHSSIZ<15:0>               |           |             |             |            |             |             |            |            |             |         | 0000   |        |        |         |        |        |        |            |

|                             |                                 |           |             |             |            |             |             |            |            | —           | —       | 0000   |        |        |         |        |        |        |            |

| 0000                        | DOMODOL                         | 15:0      |             |             |            |             |             |            |            | CHDSIZ      | Z<15:0> | -      |        |        |         |        |        |        | 0000       |

| 3000                        | DCH0SPTR                        | 31:16     | —           | —           | —          | —           |             | _          | —          | —           | —       | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                        | Donioor IIX                     | 15:0      |             |             |            |             |             |            |            | CHSPTI      | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 30E0                        | DCH0DPTR                        | 31:16     | _           | _           | —          | —           |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| OOLO                        |                                 | 15:0      |             |             |            |             |             |            |            | CHDPT       | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 30E0                        | DCH0CSIZ                        | 31:16     | _           | _           | —          | —           |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 001 0                       | DOI100012                       | 15:0      |             |             |            |             |             |            |            | CHCSIZ      | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16     | _           | _           | —          | —           |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0100                        | Donioor IIX                     | 15:0      |             |             |            |             |             |            |            | CHCPT       | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16     |             | _           | —          |             |             |            | —          | —           | —       | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0110                        | DOITODAT                        | 15:0      | —           | —           | —          |             |             |            | —          | —           |         |        |        | CHPDA  | \T<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16     |             | _           | —          |             |             |            | —          | —           | —       | —      | —      |        | —       | —      |        | —      | 0000       |

| 0120                        | Donnoon                         | 15:0      | CHBUSY      | —           | —          |             |             |            | —          | CHCHNS      | CHEN    | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16     | —           | _           | —          | —           | —           | -          | —          | —           |         |        |        | CHAIR  | Q<7:0>  |        |        |        | OOFF       |

| 5150                        | DOITILOON                       | 15:0      |             |             |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | _      | FF00       |

| 3140                        | DCH1INT                         | 31:16     | _           | _           | —          |             |             | _          | —          | —           | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5140                        | DOLLING                         | 15:0      | _           | _           | _          | _           | —           | _          | _          | —           | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16     |             |             |            |             |             |            |            | CHSSA       | <31.0>  |        |        |        |         |        |        |        | 0000       |

| 5150                        | DOITIOGA                        | 15:0      |             |             |            |             |             |            |            | 0100        |         |        |        |        |         |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16     |             |             |            |             |             |            |            | CHDSA       | 1<31.0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DONIDSA                         | 15:0      |             |             |            |             |             |            |            |             | ~~~~    |        |        |        |         |        |        |        | 0000       |

| Leger                       | od∙ v=u                         | nknown    | value on R  | leset: — =  | unimplemer | nted read a | s '0' Reset | values are | shown in h | nexadecimal |         |        |        |        |         |        |        |        |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

# REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

# Legend:

| =0901141          |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

| TABL                        | E 11-7:              | PEI       | RIPHER |       | SELEC |       | PUT RE | GISTER | MAP ( | CONTIN | IUED) |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|--------|-------|-------|-------|--------|--------|-------|--------|-------|------|------|------|------|------|--------|------|------------|

| SS                          |                      |           |        |       |       |       |        |        |       | В      | its   |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10  | 25/9  | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16     | _      | -     | —     | -     | _      | -      | _     | _      | -     | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0      | _      |       | —     |       | —      |        | _     | —      |       |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16     | —      | —     | —     | —     | —      | —      | _     | —      | —     | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0      | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | —    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16     | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | —    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0      | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16     | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        |                      | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        |                      | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0      | —      | —     | —     | —     | —      | —      | -     |        | —     | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16     | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 31:16     |        | —     | —     | —     | —      | —      | _     |        | —     | _    | —    | —    | _    | _    | —      | _    | 0000       |

| FB80                        | KPUSK"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 31:16     |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 31:16     |        | —     |       | —     | —      | —      | _     |        | —     |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | RPU/R <sup>(1)</sup> | 15:0      | _      | _     | —     | _     | _      | —      | —     | _      | —     |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

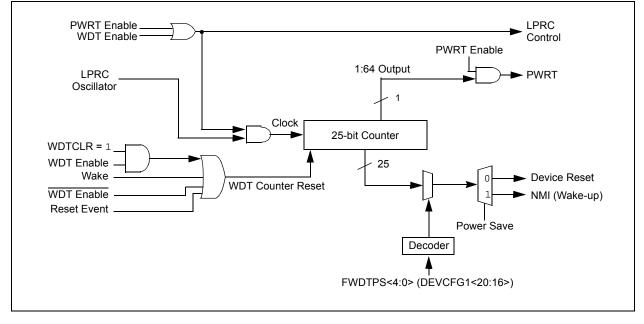

# 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

## FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | —                 | _                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTPS<4:0         | >                 |                   | WDTWINEN         | WDTCLR           |

### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                          |                    |  |

|-------------------|-----------------------------------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, I | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

|              | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 23:16        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

|              | MCLKSEL <sup>(2)</sup> | —                  |                   | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15:8         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

|              | ON <sup>(1)</sup>      | —                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

|              | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

### REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- $\ensuremath{\mathtt{l}}$  = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

- 111 = Reserved; do not use

- 110 = Reserved; do not use

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

- 1 = REFCLK is used by the Baud Rate Generator

- 0 = PBCLK is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

NOTES:

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 31.0** "**50 MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# **Absolute Maximum Ratings**

### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

3: See the "Pin Diagrams" section for the 5V tolerant pins.

| DC CHA                                | RACTERIS               | TICS    | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                             |                                                 |  |  |  |

|---------------------------------------|------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units                                                                                                                                                                                                                                                                    | Conditions                  |                                                 |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |                                                                                                                                                                                                                                                                          |                             |                                                 |  |  |  |

| DC40k                                 | 44                     | 70      | μA                                                                                                                                                                                                                                                                       | -40°C                       |                                                 |  |  |  |

| DC40I                                 | 44                     | 70      | μA                                                                                                                                                                                                                                                                       | +25°C                       | Base Power-Down Current                         |  |  |  |

| DC40n                                 | 168                    | 259     | μA                                                                                                                                                                                                                                                                       | +85°C                       |                                                 |  |  |  |

| DC40m                                 | 335                    | 536     | μA                                                                                                                                                                                                                                                                       | +105°C                      |                                                 |  |  |  |

| Module                                | Differential           | Current |                                                                                                                                                                                                                                                                          |                             |                                                 |  |  |  |

| DC41e                                 | 5                      | 20      | μA                                                                                                                                                                                                                                                                       | 3.6V                        | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |

| DC42e                                 | 23                     | 50      | μA                                                                                                                                                                                                                                                                       | 3.6V                        | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |

| DC43d                                 | 1000                   | 1100    | μA                                                                                                                                                                                                                                                                       | 3.6V ADC: △IADC (Notes 3,4) |                                                 |  |  |  |

## TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

# TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                                    | (unless o    | d Operating<br>otherwise st<br>g temperature | ated)<br>e -40°C | ≤ Ta ≤ +8 | <b>3V to 3.6V</b><br>35°C for Industrial<br>105°C for V-temp |

|--------------------|----------------------|----------------------------------------------------|--------------|----------------------------------------------|------------------|-----------|--------------------------------------------------------------|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>                     | Min.         | Typical <sup>(2)</sup>                       | Max.             | Units     | Conditions                                                   |

| SP51               | TssH2doZ             | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4) | 5            | _                                            | 25               | ns        | _                                                            |

| SP52               | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                              | Тѕск +<br>20 | —                                            | _                | ns        | —                                                            |

| SP60               | TssL2doV             | SDOx Data Output Valid after<br>SSx Edge           | —            | —                                            | 25               | ns        |                                                              |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns.

**4:** Assumes 50 pF load on all SPIx pins.

| TABLE 30-32: | <b>I2Cx BUS DATA</b> | TIMING REQUIREMENTS | (MASTER MODE) | (CONTINUED) |

|--------------|----------------------|---------------------|---------------|-------------|

|              |                      |                     |               |             |

| АС СНА        | RACTER  | ISTICS                             |                        | Standard Operation<br>(unless otherwise<br>Operating temperation | e stated)<br>iture -40 | )°C ≤ Ta ≤ | ₩ to 3.6₩<br>+85°C for Industrial<br>+105°C for V-temp |              |     |   |    |                  |

|---------------|---------|------------------------------------|------------------------|------------------------------------------------------------------|------------------------|------------|--------------------------------------------------------|--------------|-----|---|----|------------------|

| Param.<br>No. | Symbol  | Characteristics                    |                        | Min. <sup>(1)</sup>                                              | Max.                   | Units      | Conditions                                             |              |     |   |    |                  |

| IM40          | TAA:SCL | TAA:SCL Output Valid<br>from Clock | 100 kHz mode           | —                                                                | 3500                   | ns         | —                                                      |              |     |   |    |                  |

|               |         |                                    | 400 kHz mode           | —                                                                | 1000                   | ns         | —                                                      |              |     |   |    |                  |

|               |         | 1 MHz mode<br>(Note 2)             | —                      | 350                                                              | ns                     | —          |                                                        |              |     |   |    |                  |

| IM45          | TBF:SDA | Bus Free Time                      | 100 kHz mode           | 4.7                                                              | _                      | μS         | The amount of time the                                 |              |     |   |    |                  |

|               |         |                                    |                        |                                                                  |                        |            |                                                        | 400 kHz mode | 1.3 | — | μS | bus must be free |

|               |         |                                    | 1 MHz mode<br>(Note 2) | 0.5                                                              | —                      | μS         | before a new<br>transmission can start                 |              |     |   |    |                  |

| IM50          | Св      | Bus Capacitive Loading             |                        | —                                                                | 400                    | pF         | —                                                      |              |     |   |    |                  |

| IM51          | Tpgd    | Pulse Gobbler D                    | elay                   | 52                                                               | 312                    | ns         | See Note 3                                             |              |     |   |    |                  |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

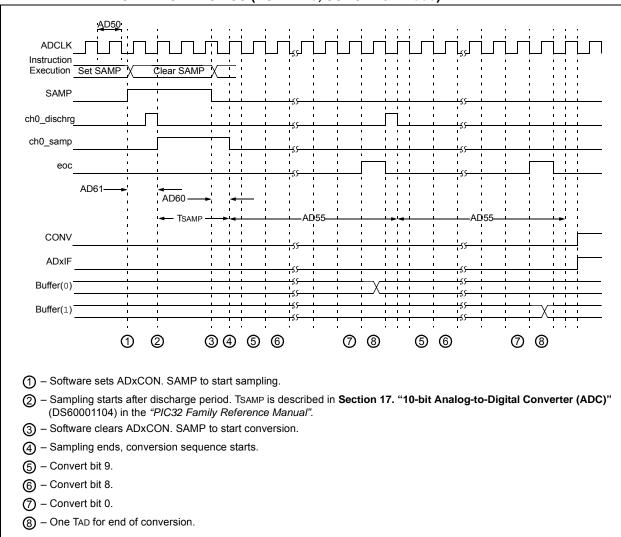

### FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

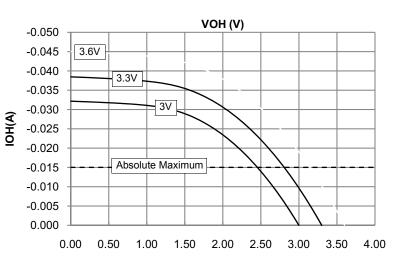

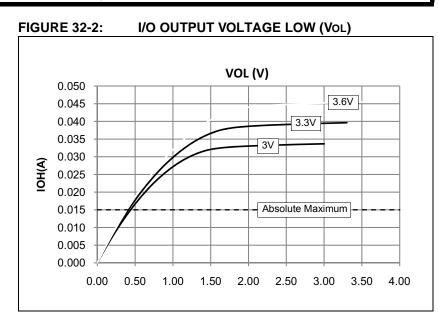

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

FIGURE 32-1: I/O OUTPUT VOLTAGE HIGH (VOH)

# APPENDIX A: REVISION HISTORY

# Revision A (May 2011)

This is the initial released version of this document.

# **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX130F064C

- PIC32MX130F064D

- PIC32MX150F128B

- PIC32MX150F128CPIC32MX150F128D

- PIC32MX250F128C

PIC32MX250F128D

PIC32MX230F064B

PIC32MX230F064C

PIC32MX230F064D

PIC32MX250F128B

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

| Section                                                                    | Update Description                                                                                                                                                        |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |

| and Graphics Interfaces, USB, and Advanced Analog"                         | Added the SPDIP package reference (see Table 1, Table 2, and " <b>Pin Diagrams</b> ").                                                                                    |

|                                                                            | Added the new devices to the applicable pin diagrams.                                                                                                                     |

|                                                                            | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |

| 1.0 "Device Overview"                                                      | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |

|                                                                            | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"          | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |

## TABLE A-1: MAJOR SECTION UPDATES