Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

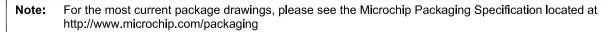

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

## 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

### TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

### 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

| Pin # | Full Pin Name                        | Pi | in # | Full Pin Name                                  |

|-------|--------------------------------------|----|------|------------------------------------------------|

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 | 1  | 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   | 2  | 20   | RPC9/CTED7/RC9                                 |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   | 2  | 21   | Vss                                            |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   | 2  | 22   | VCAP                                           |

| 5     | Vdd                                  | 2  | 23   | Vdd                                            |

| 6     | Vss                                  | 2  | 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 7     | OSC1/CLKI/RPA2/RA2                   | 2  | 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              | 2  | 26   | AN12/PMD0/RB12                                 |

| 9     | SOSCI/RPB4/RB4                       | 2  | 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       | 2  | 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 11    | RPC3/RC3                             | 2  | 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 12    | Vss                                  | 3  | 30   | AVss                                           |

| 13    | Vdd                                  | 3  | 31   | AVdd                                           |

| 14    | Vdd                                  | з  | 32   | MCLR                                           |

| 15    | PGED3/RPB5/PMD7/RB5                  | 3  | 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 16    | PGEC3/RPB6/PMD6/RB6                  | 3  | 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         | 3  | 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        | 3  | 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

### TABLE 8: **PIN NAMES FOR 36-PIN USB DEVICES**

## 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016C

|       | PIC32MX220F032C<br>PIC32MX230F064C<br>PIC32MX250F128C |       |                                                  |

|-------|-------------------------------------------------------|-------|--------------------------------------------------|

|       |                                                       |       | 36                                               |

|       |                                                       |       | 1                                                |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name                                    |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2             | 19    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3               | 20    | RPC9/CTED7/RC9                                   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0                    | 21    | Vss                                              |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1                    | 22    | VCAP                                             |

| 5     | VDD                                                   | 23    | VDD                                              |

| 6     | Vss                                                   | 24    | PGED2/RPB10/D+/CTED11/RB10                       |

| 7     | OSC1/CLKI/RPA2/RA2                                    | 25    | PGEC2/RPB11/D-/RB11                              |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3                               | 26    | VUSB3V3                                          |

| 9     | SOSCI/RPB4/RB4                                        | 27    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                        | 28    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 11    | AN12/RPC3/RC3                                         | 29    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 12    | Vss                                                   | 30    | AVss                                             |

| 13    | Vdd                                                   | 31    | AVdd                                             |

| 14    | VDD                                                   | 32    | MCLR                                             |

| 15    | TMS/RPB5/USBID/RB5                                    | 33    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 16    | VBUS                                                  | 34    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7                          | 35    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 18    | TCK/RP88/SCL1/CTED10/PM04/RB8                         | 36    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin 1: Select" for restrictions.

Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information. 2:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 3:

4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

|          |                        | Pin Nu                            | mber <sup>(1)</sup> | -                               |             |                |                                           |

|----------|------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                  | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                   | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                   | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                  | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                     | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                     | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                   | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                     | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                  | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                   | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                   | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                   | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                  | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                  | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                  | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                  | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                  | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                  | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                  | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                  | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                  | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                     |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                     |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe        | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

###

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

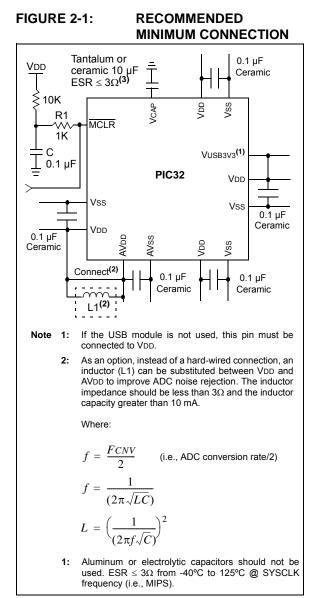

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

### 2.3 Capacitor on Internal Voltage Regulator (VCAP)

### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **30.0 "Electrical Characteristics"** for additional information on CEFC specifications.

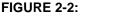

### 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# EXAMPLE OF MCLR PIN CONNECTIONS

**3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

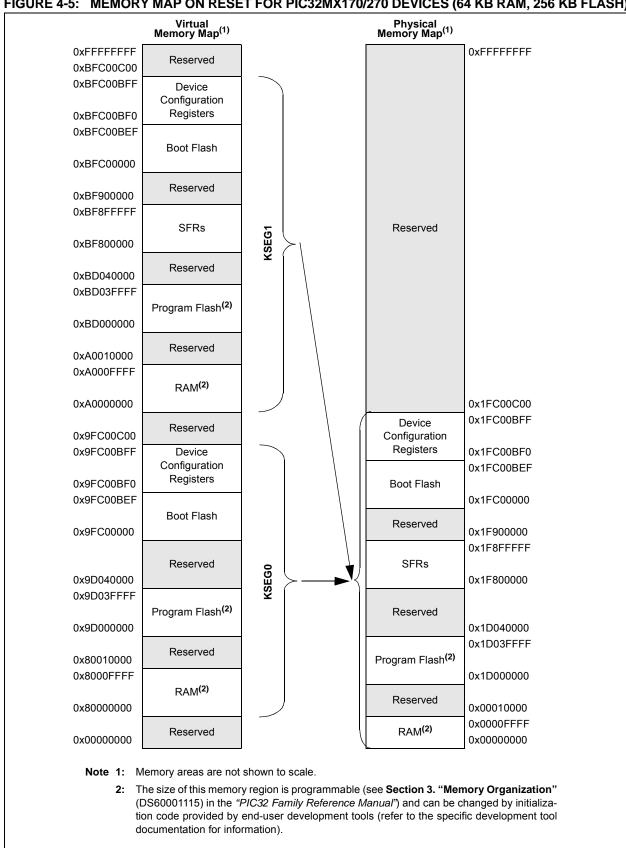

### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | —                 | —                 | —                 |                   | IP03<2:0>         | IS03              | IS03<1:0>        |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | —                 |                   |                   | IP02<2:0>         | IS02<1:0>         |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | _                 | —                 |                   |                   | IP01<2:0>         |                   | IS01·            | <1:0>            |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | _                 | _                 | _                 |                   | IP00<2:0>         | IS00<1:0>         |                  |                  |  |

### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

### Legend:

| Logonal           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-26 IP03<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 25-24 IS03<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 23-21 Unimplemented: Read as '0' bit 20-18 IP02<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 17-16 IS02<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 15-13 Unimplemented: Read as '0' bit 12-10 IP01<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- **Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

| REGIOTE      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |

### REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

### **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                          |                              |                    |  |

|-------------------|--------------------------|------------------------------|--------------------|--|

| R = Readable bit  | U = Unimplemented bit, r | implemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared         | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | _                       | _                       | _                 | —                    | —                 | —                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | STALLIF           | ALIACHIE'               | INE SOMEIFY /           | IDLEIF            |                      | JOFIE             |                       | DETACHIF <sup>(6)</sup> |

### REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settal | ole bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

| bit 7       | <b>STALLIF:</b> STALL Handshake Interrupt bit<br>1 = In Host mode a STALL handshake was received during the handshake phase of the transaction<br>In Device mode a STALL handshake was transmitted during the handshake phase of the transaction<br>0 = STALL handshake has not been sent                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6       | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup><br>1 = Peripheral attachment was detected by the USB module<br>0 = Peripheral attachment was not detected                                                                                                                                                                                                                                                                               |

| bit 5       | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup><br>1 = K-State is observed on the D+ or D- pin for 2.5 μs<br>0 = K-State is not observed                                                                                                                                                                                                                                                                                                    |

| bit 4       | IDLEIF: Idle Detect Interrupt bit<br>1 = Idle condition detected (constant Idle state of 3 ms or more)<br>0 = No Idle condition detected                                                                                                                                                                                                                                                                                                         |

| bit 3       | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup><br>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information<br>0 = Processing of current token not complete                                                                                                                                                                                                             |

| bit 2       | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host<br>0 = SOF token was not received nor threshold reached                                                                                                                                                                                                                                                               |

| bit 1       | <b>UERRIF</b> : USB Error Condition Interrupt bit <sup>(4)</sup><br>1 = Unmasked error condition has occurred<br>0 = Unmasked error condition has not occurred                                                                                                                                                                                                                                                                                   |

| bit 0       | <pre>URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup> 1 = Valid USB Reset has occurred 0 = No USB Reset has occurred DETACHIF: USB Detach Interrupt bit (Host mode)<sup>(6)</sup> 1 = Peripheral detachment was detected by the USB module 0 = Peripheral detachment was not detected</pre>                                                                                                                                           |

| 3<br>2<br>5 | <ul> <li>This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for 2.5 µs, and the current bus state is not SE0.</li> <li>When not in Suspend mode, this interrupt should be disabled.</li> <li>Clearing this bit will cause the STAT FIFO to advance.</li> <li>Only error conditions enabled through the U1EIE register will set this bit.</li> <li>Device mode.</li> <li>Host mode.</li> </ul> |

| TABL                        | E 11-6:                       | PEF       | RIPHER | AL PIN | SELEC | T INPU | T REGI | STER M | AP (CC | NTINU | ED)  |      |      |      |             |       |          |      |            |

|-----------------------------|-------------------------------|-----------|--------|--------|-------|--------|--------|--------|--------|-------|------|------|------|------|-------------|-------|----------|------|------------|

| sse                         |                               |           |        | Bits   |       |        |        |        |        |       |      |      |      |      |             |       |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name<br>Bit Range | Bit Range | 31/15  | 30/14  | 29/13 | 28/12  | 27/11  | 26/10  | 25/9   | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3        | 18/2  | 17/1     | 16/0 | All Resets |

|                             |                               | 31:16     | _      | —      | -     | -      | —      | —      | —      | —     | —    | —    | —    | -    | -           | -     | —        | —    | 0000       |

| FA54                        | U1CTSR                        | 15:0      | _      | _      | _     | _      | _      | _      | _      | _     | _    | _    | _    | _    |             | U1CTS | R<3:0>   |      | 0000       |

| FAGO                        |                               | 31:16     | _      | _      | _     | _      | _      | _      | _      | _     | _    | _    | _    | _    | _           | _     | _        | _    | 0000       |

| FA58                        | U2RXR                         | 15:0      | _      | _      | _     | _      | _      | _      | _      | _     | _    | _    | _    | _    | U2RXR<3:0>  |       |          |      | 0000       |

|                             |                               | 31:16     | _      | _      | _     | —      | _      | _      | _      | _     |      | —    |      | —    | —           | —     |          |      | 0000       |

| FA5C                        | U2CTSR                        | 15:0      | —      | —      | _     | —      | —      | —      | _      | _     |      | —    |      | —    | U2CTSR<3:0> |       |          |      | 0000       |

| FA84                        | SDI1R                         | 31:16     | —      | —      | —     | _      | _      | —      | _      | _     |      | _    |      | _    | _           | _     |          |      | 0000       |

| FA64                        | SDIIR                         | 15:0      | —      | —      | —     | _      | _      | —      | _      | _     |      | _    |      | _    |             | SDI1F | R<3:0>   |      | 0000       |

| FA88                        | SS1R                          | 31:16     | —      | —      | —     | —      | —      | —      | —      | —     | —    | —    | —    | —    | —           | —     | —        | -    | 0000       |

| FA00                        | 33 IK                         | 15:0      | —      | —      | —     | —      | —      | —      | —      | —     | —    | —    | —    | —    |             | SS1R  | <3:0>    |      | 0000       |

| FA90                        | SDI2R                         | 31:16     | —      | —      | —     | —      | —      | —      | —      | —     | —    | —    | —    | —    | —           | —     | —        | -    | 0000       |

| FA90                        | SDIZK                         | 15:0      | —      | —      | —     | —      | —      | —      | —      | —     | —    | —    | —    | —    |             | SDI2F | R<3:0>   |      | 0000       |

| FA94                        | SS2R                          | 31:16     | _      | _      |       | _      | _      | _      | _      | _     | _    | _    | _    | _    | _           | —     |          | _    | 0000       |

| 17,34                       | 552N                          | 15:0      | _      | _      |       | _      | _      | _      | _      | _     | _    | _    | _    | _    |             | SS2R  | <3:0>    |      | 0000       |

| FARS                        | REFCLKIR                      | 31:16     | _      | _      |       | _      | _      | _      | _      | _     | _    | _    | _    | _    | _           | —     |          | _    | 0000       |

| 1 ADO                       |                               | 15:0      | —      | —      | _     | —      | —      | —      | —      | —     | —    | —    | —    | —    |             | REFCL | (IR<3:0> |      | 0000       |

### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      | Bits      |       |       |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | _    | 0000       |

| FB8C                        | RPCOR                | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | —    | 0000       |

| FB90                        | KPC9R <sup>w</sup>   | 15:0      |       | —     | —     | —     | _     | -     | —    | —    | _    | _    | —    |      |      | RPC9 | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup> 11111111 = Alarm will trigger 256 times

> 00000000 = Alarm will trigger one time The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

NOTES:

### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

|               |         |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)                                                                                                                      |                        |            |       |                                                   |  |  |  |  |  |

|---------------|---------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|--|--|--|--|

|               | ARACTER |                                                         | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |       |                                                   |  |  |  |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                                                                                                                                                                                       | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |  |  |  |  |

|               | VIL     | Input Low Voltage                                       |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                                                                                                                                                                                        | —                      | 0.15 Vdd   | V     |                                                   |  |  |  |  |  |

|               |         | I/O Pins                                                | Vss                                                                                                                                                                                        | —                      | 0.2 Vdd    | V     |                                                   |  |  |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss                                                                                                                                                                                        | _                      | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |  |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss                                                                                                                                                                                        | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |  |  |  |

|               | VIH     | Input High Voltage                                      |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                   | _                      | Vdd        | V     | (Note 4,6)                                        |  |  |  |  |  |

|               |         | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                            | —                      | 5.5        | V     | (Note 4,6)                                        |  |  |  |  |  |

|               |         | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                                                                                                                                                   | —                      | 5.5        | V     |                                                   |  |  |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD                                                                                                                                                                                   | _                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1                                                                                                                                                                                        | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |  |  |  |

| DI30          | ICNPU   | Change Notification<br>Pull-up Current                  | _                                                                                                                                                                                          | —                      | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _                                                                                                                                                                                          | —                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |  |  |  |

|               | lı∟     | Input Leakage Current<br>(Note 3)                       |                                                                                                                                                                                            |                        |            |       |                                                   |  |  |  |  |  |

| DI50          |         | I/O Ports                                               | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |  |  |  |

| DI51          |         | Analog Input Pins                                       | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | —                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |  |  |  |  |

| DI56          |         | OSC1                                                    | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |  |  |  |  |

### TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

### TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS                  |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                |  |  |  |  |

|---------------|---------|-------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Charact                 | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Max. | Units | Conditions                     |  |  |  |  |

| IM10          | TLO:SCL | Clock Low Time          | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | —    | μs    | —                              |  |  |  |  |

|               |         |                         | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    | —                              |  |  |  |  |

|               |         |                         | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μs    | _                              |  |  |  |  |

| IM11          | THI:SCL | Clock High Time         | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    | —                              |  |  |  |  |

|               |         |                         | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | —    | μS    | —                              |  |  |  |  |

|               |         |                         | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | —    | μs    | —                              |  |  |  |  |

| IM20          | TF:SCL  | SDAx and SCLx           | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                     | 300  | ns    | CB is specified to be          |  |  |  |  |

|               |         | Fall Time               | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | from 10 to 400 pF              |  |  |  |  |

|               |         |                         | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                     | 100  | ns    |                                |  |  |  |  |

| IM21          | TR:SCL  | SDAx and SCLx           | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                     | 1000 | ns    | CB is specified to be          |  |  |  |  |

|               |         | Rise Time               | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | from 10 to 400 pF              |  |  |  |  |

|               |         |                         | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                     | 300  | ns    |                                |  |  |  |  |

| IM25 TSU:DAT  | TSU:DAT | Data Input              | 100 kHz mode                  | 250                                                                                                                                                                                                                                                                                   | _    | ns    | —                              |  |  |  |  |

|               |         | Setup Time              | 400 kHz mode                  | 100                                                                                                                                                                                                                                                                                   | —    | ns    | -                              |  |  |  |  |

|               |         |                         | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                                                                                   | _    | ns    |                                |  |  |  |  |

| IM26          | THD:DAT | Data Input<br>Hold Time | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                     | _    | μS    | —                              |  |  |  |  |

|               |         |                         | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                     | 0.9  | μs    |                                |  |  |  |  |

|               |         |                         | 1 MHz mode<br>(Note 2)        | 0                                                                                                                                                                                                                                                                                     | 0.3  | μs    |                                |  |  |  |  |

| IM30          | TSU:STA | Start Condition         | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                       | _    | μS    | Only relevant for              |  |  |  |  |