Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128d-v-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

#### TABLE 3-2: COPROCESSOR 0 REGISTERS

**Note 1:** Registers used in exception processing.

**2:** Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 31:24        | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R R               |                   | R                 | R                 | R R               |                   | R                | R                |  |  |  |  |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 15:8         | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |  |  |

#### **BMXDRMSZ: DATA RAM SIZE REGISTER REGISTER 4-5:**

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00001000 = Device has 4 KB RAM 0x00002000 = Device has 8 KB RAM 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

#### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                       | —                 | _                 | _                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0                     | U-0               | U-0               | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |  |

| 23:16        | _                 | — — — — BMXPUPBA<19:16> |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                         |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0                     | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                         |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

#### bit 10-0 BMXPUPBA<10:0>: Read-Only bits This value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

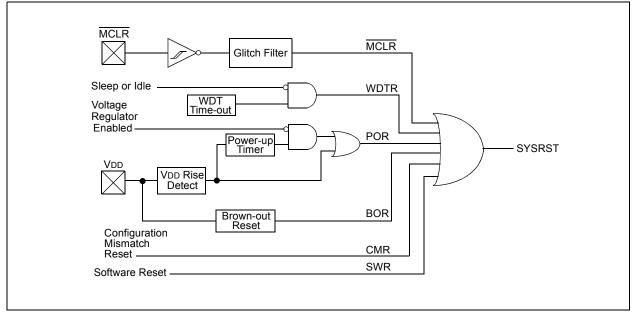

#### 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

#### FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|----------------------------------|-----------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.04        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31:24        | _                                | _         | _                 | _                 | _                 |                   | -                  | —                  |

| 22:16        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | U-0                | U-0                |

| 23:16        | _                                | _         | _                 | _                 | _                 |                   | -                  | —                  |

| 45.0         | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         |                                  | _         | _                 | -                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS                        | R/W-0, HS | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR                             | SWR       | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-10 Unimplemented: Read as '0'

| bit 9 | CMR: Configuration Mismatch Reset Flag bit             |

|-------|--------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred          |

|       | 0 = Configuration mismatch Reset has not occurred      |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit            |

|       | 1 = Regulator is enabled and is on during Sleep mode   |

|       | 0 = Regulator is disabled and is off during Sleep mode |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit               |

|       | 1 = Master Clear (pin) Reset has occurred              |

|       | 0 = Master Clear (pin) Reset has not occurred          |

| bit 6 | SWR: Software Reset Flag bit                           |

|       | 1 = Software Reset was executed                        |

|       | 0 = Software Reset as not executed                     |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                 |

|       | 1 = WDT Time-out has occurred                          |

|       | 0 = WDT Time-out has not occurred                      |

| bit 3 | SLEEP: Wake From Sleep Flag bit                        |

|       | 1 = Device was in Sleep mode                           |

|       | 0 = Device was not in Sleep mode                       |

| bit 2 | IDLE: Wake From Idle Flag bit                          |

|       | 1 = Device was in Idle mode                            |

|       | 0 = Device was not in Idle mode                        |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>           |

|       | 1 = Brown-out Reset has occurred                       |

|       | 0 = Brown-out Reset has not occurred                   |

| bit 0 | POR: Power-on Reset Flag bit <sup>(1)</sup>            |

|       | 1 = Power-on Reset has occurred                        |

|       | 0 = Power-on Reset has not occurred                    |

|       |                                                        |

**Note 1:** User software must clear this bit to view next detection.

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS01<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-2 | IP00<2:0>: Interrupt Priority bits                                                                                    |

|         | 111 = Interrupt priority is 7                                                                                         |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | 010 = Interrupt priority is 2                                                                                         |

|         | 001 = Interrupt priority is 1                                                                                         |

|         | 000 = Interrupt is disabled                                                                                           |

| bit 1-0 | IS00<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

#### 9.1 DMA Control Registers

#### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | Ċ,        | Bits  |       |       |         |         |       |      |          |           |      |      |      |      |      | s         |      |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|-----------|------|------|------|------|------|-----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | _     | _     | -     | —       | —       | _     | —    | —        | —         | -    | -    | _    | -    | -    | —         | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | —     | _     | SUSPEND | DMABUSY | —     | _    | —        | _         | —    | —    | —    | —    | —    | —         | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | _    | —    | —         | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | RDWR | DI   | MACH<2:0> | .(2) | 0000      |

| 3020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D-31:05   |      |      |      |      |      |           |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      |       |       |       |         |         |       |      | DIVIAADL | vix~51.02 |      |      |      |      |      |           |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         | Bits                            |           |       |               |       |       |                                 |       |      |        |          |      |      |            |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|-------|---------------------------------|-------|------|--------|----------|------|------|------------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11                           | 26/10 | 25/9 | 24/8   | 23/7     | 22/6 | 21/5 | 20/4       | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _             | BYTO  | <1:0> | :0> WBO BITO                    |       |      |        |          |      | _    | —          | _    | 0000 |      |      |            |

| 3030                        | DURUUUN                         | 15:0      | —     | _             | —     |       | PLEN<4:0> CRCEN CRCAPP CRCTYP C |       |      |        |          |      |      | CRCCH<2:0> |      | 0000 |      |      |            |

| 2040                        | DCRCDATA                        | 31:16     |       |               |       |       |                                 |       |      |        | TA<31:0> |      |      |            |      |      |      |      | 0000       |

| 3040                        | DURUDAIA                        | 15:0      |       |               |       |       |                                 |       |      | DURUDA | IA~51.02 |      |      |            |      |      |      |      | 0000       |

| 3050                        | DCRCXOR                         | 31:16     |       | DCRCXOR<31:0> |       |       |                                 |       |      |        |          |      | 0000 |            |      |      |      |      |            |

| 3050                        | DUNUAUR                         | 15:0      |       |               |       |       |                                 |       |      | DORUAU | N-51.02  |      |      |            |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legend:                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | -                 | _                 |                   | -                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |  |

#### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                       |                    |  |  |

|-------------------|------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | it U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          | Bits                      |           |       |       |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|---------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name          | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup>      | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | —    | 0000       |

| FB8C                        | RPCoR                     | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup>      | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     |      | 0000       |

| FB90                        | FB90 RPC9R <sup>(3)</sup> | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPC  | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | _                 | —                 | _                 | _                 |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

#### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

### 13.2 Timer Control Registers

## TABLE 13-1: TIMER2-TIMER5 REGISTER MAP

|                             | - 15                            |           |                     |       |       |       |       |       |      |          |        |      |            |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|---------------------|-------|-------|-------|-------|-------|------|----------|--------|------|------------|------|------|------|----------|------|------------|

| ess                         |                                 |           |                     |       |       |       |       |       |      | Bi       | its    |      |            |      |      |      |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15               | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7   | 22/6 | 21/5       | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     | _                   | _     | —     | _     | —     | —     | —    | —        | —      | -    | —          | _    | —    | _    | _        | -    | 0000       |

| 0000                        | 12001                           | 15:0      | ON                  |       | SIDL  | —     | —     | —     | _    | _        | TGATE  | -    | TCKPS<2:0> | >    | T32  | —    | TCS      | —    | 0000       |

| 0810                        | TMR2                            | 31:16     | —                   | —     | —     | —     | —     | —     | _    | —        | —      | —    | —          | —    |      | —    | —        | _    | 0000       |

| 0010                        |                                 | 15:0      |                     |       |       |       |       |       |      |          |        |      |            |      |      |      |          |      |            |

| 0820                        | PR2                             | 31:16     | —                   | —     | —     | —     | —     | —     | —    | —        | —      | _    | —          | —    | —    | —    | —        | _    | 0000       |

| 0020                        |                                 | 15:0      |                     |       |       |       |       |       |      | PR2<     | 15:0>  |      |            |      |      |      |          |      | FFFF       |

| 0040                        | T3CON                           | 31:16     | —                   | —     | —     | _     | —     | —     | —    | —        | —      | -    | —          | —    | —    | _    | —        | —    | 0000       |

| 0/100                       | 10001                           | 15:0      | ON                  | —     | SIDL  | _     | —     | —     | —    | —        | TGATE  |      | TCKPS<2:0> | >    | —    | _    | TCS      | —    | 0000       |

| 0A10                        | TMR3                            | 31:16     |                     | _     | _     | —     | _     | —     |      | —        |        | —    | —          | _    | —    | _    | _        |      | 0000       |

| 0,110                       | -                               | 15:0      |                     |       |       |       |       |       |      | TMR3     | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0A20                        | PR3                             | 31:16     | —                   | —     | —     | —     | —     | —     | _    | —        | —      |      | —          | _    |      | —    | —        |      | 0000       |

|                             | _                               | 15:0      |                     |       |       |       |       |       |      | PR3<     | :15:0> |      |            |      |      |      |          |      | FFFF       |

| 0C00                        | T4CON                           | 31:16     | _                   | _     | —     | —     | —     | —     | —    | _        | —      | —    | —          | —    | —    | —    | _        | —    | 0000       |

|                             |                                 | 15:0      | ON                  | —     | SIDL  | —     | —     |       | _    | —        | TGATE  | -    | TCKPS<2:0> | >    | T32  | —    | TCS      |      | 0000       |

| 0C10                        | TMR4                            | 31:16     | _                   | —     | —     | —     | —     | —     | _    | —        | —      | —    | —          | —    | —    | —    | —        | —    | 0000       |

|                             |                                 | 15:0      |                     |       |       |       |       |       |      | TMR4     |        |      |            |      |      |      |          |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _                   | —     | —     | —     | —     | —     | _    | -        | —      | _    | —          | _    | —    | _    | —        |      | 0000       |

|                             |                                 | 15:0      |                     |       |       |       |       |       |      |          | :15:0> |      |            |      |      |      |          |      | FFFF       |

| 0E00                        | T5CON                           | 31:16     | -                   | _     | -     | _     |       | —     |      | _        |        |      |            |      |      |      | —<br>T00 |      | 0000       |

|                             |                                 | 15:0      | ON                  |       | SIDL  | _     |       |       | _    | _        | TGATE  |      | TCKPS<2:0> |      | _    | _    | TCS      | _    | 0000       |

| 0E10                        | TMR5                            | 31:16     | —                   | —     | —     | _     | —     | —     | —    |          |        | _    | —          | _    | —    | _    | —        | _    | 0000       |

| <u> </u>                    |                                 | 15:0      |                     |       |       |       |       |       |      | TMR5     | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0E20                        | PR5                             | 31:16     |                     | —     | —     | —     | —     | —     | _    |          |        | _    | —          | _    | —    | —    | —        |      | 0000       |

|                             |                                 |           | 15:0 PR5<15:0> FFFF |       |       |       |       |       |      | F.F.F.F. |        |      |            |      |      |      |          |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

NOTES:

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| DC CHARACT                                                         | ERISTICS               |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                   |                 |          |  |  |  |  |  |

|--------------------------------------------------------------------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------|--|--|--|--|--|

| Parameter<br>No.                                                   | Typical <sup>(2)</sup> | Max. | Units                                                                                                                                                                                              | Units Conditions  |                 |          |  |  |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Notes 1, 4) |                        |      |                                                                                                                                                                                                    |                   |                 |          |  |  |  |  |  |

| DC30a                                                              | 1                      | 1.5  | mA                                                                                                                                                                                                 |                   | 4 MHz (Note 3)  |          |  |  |  |  |  |

| DC31a                                                              | 2                      | 3    | mA                                                                                                                                                                                                 |                   | 10 MHz          |          |  |  |  |  |  |

| DC32a                                                              | 4                      | 6    | mA                                                                                                                                                                                                 |                   | 20 MHz (Note 3) |          |  |  |  |  |  |

| DC33a                                                              | 5.5                    | 8    | mA                                                                                                                                                                                                 |                   | 30 MHz (Note 3) |          |  |  |  |  |  |

| DC34a                                                              | 7.5                    | 11   | mA                                                                                                                                                                                                 |                   | 40 MHz          |          |  |  |  |  |  |

| DC37a                                                              | 100                    | _    | μA                                                                                                                                                                                                 | -40°C LPRC (31 kH |                 |          |  |  |  |  |  |

| DC37b                                                              | 250                    | _    | μA                                                                                                                                                                                                 | +25°C 3.3V (N     |                 | (Note 3) |  |  |  |  |  |

| DC37c                                                              | 380                    |      | μA                                                                                                                                                                                                 | +85°C             |                 |          |  |  |  |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

OSC2/CLKO is configured as an I/O input pin

- UCD DLL as sillator is dischard if the LLCD readule is implemented

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1  $\,$

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

|               |         |                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                        |            |       |                                                   |  |  |  |  |

|---------------|---------|---------------------------------------------------------|-----------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|--|--|--|

|               | ARACTER |                                                         | Operating tempe                                                       |                        |            |       | C for Industrial<br>C for V-temp                  |  |  |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                                                                  | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |  |  |  |

|               | VIL     | Input Low Voltage                                       |                                                                       |                        |            |       |                                                   |  |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                                                                   | —                      | 0.15 Vdd   | V     |                                                   |  |  |  |  |

|               |         | I/O Pins                                                | Vss                                                                   | —                      | 0.2 Vdd    | V     |                                                   |  |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss                                                                   | _                      | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss                                                                   | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |  |  |

|               | VIH     | Input High Voltage                                      |                                                                       |                        |            |       |                                                   |  |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                              | —                      | Vdd        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                       | —                      | 5.5        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                                                              | —                      | 5.5        | V     |                                                   |  |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD                                                              | _                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1                                                                   | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |  |  |

| DI30          | ICNPU   | Change Notification<br>Pull-up Current                  | _                                                                     | —                      | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _                                                                     | —                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |  |  |

|               | lı∟     | Input Leakage Current<br>(Note 3)                       |                                                                       |                        |            |       |                                                   |  |  |  |  |

| DI50          |         | I/O Ports                                               | _                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |  |  |

| DI51          |         | Analog Input Pins                                       | _                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | —                                                                     | _                      | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |  |  |  |

| DI56          |         | OSC1                                                    | _                                                                     | _                      | <u>+</u> 1 | μA    | $VSS \le VPIN \le VDD,$<br>XT and HS modes        |  |  |  |  |

#### TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

| DC CHARACTERISTICS |        |                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                                                             |  |  |

|--------------------|--------|---------------------|------------------------------------------------------|------|------|-------|-------------------------------------------------------------|--|--|

| Param.             | Symbol | Characteristic      | Min.                                                 | Тур. | Max. | Units | Conditions                                                  |  |  |

| DO10               | Vol    | Output Low Voltage  | _                                                    | _    | 0.4  | V     | $\text{IOL} \leq 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |  |

|                    |        | Output High Voltage | 1.5 <b>(1)</b>                                       | _    | _    |       | IOH $\geq$ -14 mA, VDD = 3.3V                               |  |  |

| 0000               | Vон    | I/O Pins            | 2.0 <sup>(1)</sup>                                   | _    | _    | v     | IOH $\geq$ -12 mA, VDD = 3.3V                               |  |  |

| DO20               | VOH    |                     | 2.4                                                  | _    | _    | v     | IOH $\geq$ -10 mA, VDD = 3.3V                               |  |  |

|                    |        |                     | 3.0(1)                                               | —    | —    |       | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$         |  |  |

#### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                           | (unles              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                      |   |  |  |  |  |

|--------------------|--------|-----------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|---|--|--|--|--|

| Param.<br>No.      | Symbol | Characteristics                                           | Min. <sup>(1)</sup> | Typical                                                                                                                                                                                                                                                                             | Max. | ax. Units Conditions |   |  |  |  |  |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low <sup>(2)</sup> | 2.0                 |                                                                                                                                                                                                                                                                                     | 2.3  | V                    | _ |  |  |  |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

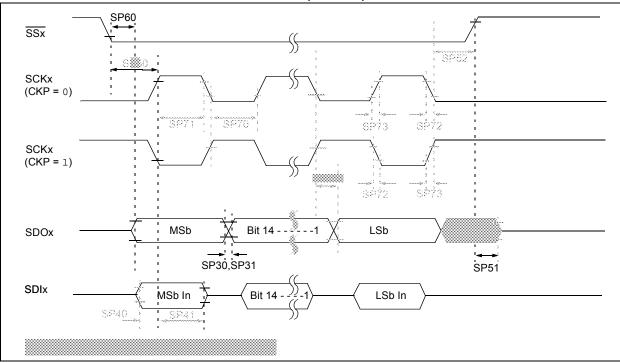

#### FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS