#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f128dt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | rals                               |                    |                     |     |     | <u> </u>                                 |      | ls)                          |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|-----|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l²C | PMP | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F064B | 28   | 64+3                               | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F064C | 36   | 64+3                               | 16               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Υ    | VTLA                            |

| PIC32MX130F064D | 44   | 64+3                               | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX150F128B | 28   | 128+3                              | 32               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX150F128C | 36   | 128+3                              | 32               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2   | Y   | 4/0                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX150F128D | 44   | 128+3                              | 32               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F256B | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F256D | 44   | 256+3                              | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX170F256B | 28   | 256+3                              | 64               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX170F256D | 44   | 256+3                              | 64               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2   | Y   | 4/0                                      | Y    | 13                           | Y    | 35       | Y    | VTLA,<br>TQFP,<br>QFN           |

### TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

### TABLE 3-2: COPROCESSOR 0 REGISTERS

**Note 1:** Registers used in exception processing.

**2:** Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2                                                                                                    | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0                                                                                                                  | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                                                                                                                    | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                                                                                  | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | 26/18/10/2         25/17/9/1         24/16/8/0           U-0         U-0         U-0           —         —         — |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                                                                | R-0              | R-0              |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                                                                                                                      |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0                                                                                                                  | R-0              | R-0              |  |

| 7:0          | BMXDUDBA<7:0>     |                   |                   |                   |                   |                                                                                                                      |                  |                  |  |

### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

## Legend:

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

### bit 9-0 BMXDUDBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R R R R R R R R   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 15:8         |                   |                   |                   | BMXPF             | /ISZ<15:8>        |                   |                  |                  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |

| 7:0          | BMXPFMSZ<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00004000 = Device has 16 KB Flash 0x00008000 = Device has 32 KB Flash 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash

### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R R R R R R R R   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 31:24        |                   |                   |                   | BMXBOO            | TSZ<31:24>        |                   |                  |                  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          | BMXBOOTSZ<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00000C00 = Device has 3 KB boot Flash

### 7.1 Interrupt Control Registers

### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                                 | â             |        |        |        |         |             |         |             | Bits    |        |          |          |           |                      |         |           |        |               |

|-----------------------------|---------------------------------|---------------|--------|--------|--------|---------|-------------|---------|-------------|---------|--------|----------|----------|-----------|----------------------|---------|-----------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14  | 29/13  | 28/12   | 27/11       | 26/10   | 25/9        | 24/8    | 23/7   | 22/6     | 21/5     | 20/4      | 19/3                 | 18/2    | 17/1      | 16/0   | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _      | _      | —      | _       |             |         | _           |         |        |          | _        | _         |                      | —       |           |        | 0000          |

| 1000                        | INTCOM                          | 15:0          | —      | _      | —      | MVEC    | -           |         | TPC<2:0>    |         | -      | —        | _        | INT4EP    | INT3EP               | INT2EP  | INT1EP    | INT0EP | 0000          |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —      |        | —      | _       | _           | _       | —           | —       |        | _        | _        | _         |                      |         | —         | —      | 0000          |

| 1010                        | INTOTAL                         | 15:0          | —      | _      | —      | —       | _           |         | SRIPL<2:0>  |         | _      | _        |          |           | VEC<5:0              | )>      |           |        | 0000          |

| 1020                        | IPTMR                           | 31:16<br>15:0 |        |        |        |         |             |         |             | IPTMR<3 | 1:0>   |          |          |           |                      |         |           |        | 0000          |

| 4000                        | 1500                            | 31:16         | FCEIF  | RTCCIF | FSCMIF | AD1IF   | OC5IF       | IC5IF   | IC5EIF      | T5IF    | INT4IF | OC4IF    | IC4IF    | IC4EIF    | T4IF                 | INT3IF  | OC3IF     | IC3IF  | 0000          |

| 1030                        | IFS0                            | 15:0          | IC3EIF | T3IF   | INT2IF | OC2IF   | IC2IF       | IC2EIF  | T2IF        | INT1IF  | OC1IF  | IC1IF    | IC1EIF   | T1IF      | INT0IF               | CS1IF   | CS0IF     | CTIF   | 0000          |

| 1010                        | 1504                            | 31:16         | DMA3IF | DMA2IF | DMA1IF | DMA0IF  | CTMUIF      | I2C2MIF | I2C2SIF     | I2C2BIF | U2TXIF | U2RXIF   | U2EIF    | SPI2TXIF  | SPI2RXIF             | SPI2EIF | PMPEIF    | PMPIF  | 0000          |

| 1040                        | IFS1                            | 15:0          | CNCIF  | CNBIF  | CNAIF  | I2C1MIF | I2C1SIF     | I2C1BIF | U1TXIF      | U1RXIF  | U1EIF  | SPI1TXIF | SPI1RXIF | SPI1EIF   | USBIF <sup>(2)</sup> | CMP3IF  | CMP2IF    | CMP1IF | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE  | RTCCIE | FSCMIE | AD1IE   | OC5IE       | IC5IE   | IC5EIE      | T5IE    | INT4IE | OC4IE    | IC4IE    | IC4EIE    | T4IE                 | INT3IE  | OC3IE     | IC3IE  | 0000          |

| 1060                        | IECU                            | 15:0          | IC3EIE | T3IE   | INT2IE | OC2IE   | IC2IE       | IC2EIE  | T2IE        | INT1IE  | OC1IE  | IC1IE    | IC1EIE   | T1IE      | INT0IE               | CS1IE   | CS0IE     | CTIE   | 0000          |

| 1070                        | IEC1                            | 31:16         | DMA3IE | DMA2IE | DMA1IE | DMA0IE  | CTMUIE      | I2C2MIE | I2C2SIE     | I2C2BIE | U2TXIE | U2RXIE   | U2EIE    | SPI2TXIE  | SPI2RXIE             | SPI2EIE | PMPEIE    | PMPIE  | 0000          |

| 1070                        | ILC I                           | 15:0          | CNCIE  | CNBIE  | CNAIE  | I2C1MIE | I2C1SIE     | I2C1BIE | U1TXIE      | U1RXIE  | U1EIE  | SPI1TXIE | SPI1RXIE | SPI1EIE   | USBIE <sup>(2)</sup> | CMP3IE  | CMP2IE    | CMP1IE | 0000          |

| 1090                        | IPC0                            | 31:16         | —      | _      | —      |         | INT0IP<2:0> |         | INT0IS<1:0> |         | -      | —        | _        | С         | S1IP<2:0>            |         | CS1IS<1:0 |        | 0000          |

| 1030                        | 11 00                           | 15:0          | —      | —      | —      |         | CS0IP<2:0>  |         | CS0IS       | <1:0>   | _      | —        | —        | (         | CTIP<2:0>            |         | CTIS      | <1:0>  | 0000          |

| 10A0                        | IPC1                            | 31:16         | —      |        | —      |         | INT1IP<2:0> |         | INT1IS      | <1:0>   | _      | —        | _        | 0         | C1IP<2:0>            |         | OC1IS     | S<1:0> | 0000          |

| 10,10                       |                                 | 15:0          | —      | —      | —      |         | IC1IP<2:0>  |         | IC1IS•      | <1:0>   | _      |          | —        | ٦         | Γ1IP<2:0>            |         | T1IS      | <1:0>  | 0000          |

| 10B0                        | IPC2                            | 31:16         | _      | —      | —      |         | INT2IP<2:0> |         | INT2IS      | <1:0>   | _      | —        | _        | 0         | C2IP<2:0>            |         | OC2IS     | 6<1:0> | 0000          |

| 1000                        | 11 02                           | 15:0          | —      |        | —      |         | IC2IP<2:0>  |         | IC2IS<      | <1:0>   | _      | —        | _        | 1         | [21P<2:0>            |         | T2IS      | <1:0>  | 0000          |

| 10C0                        | IPC3                            | 31:16         | —      | —      | —      |         | INT3IP<2:0> |         | INT3IS      | <1:0>   | —      |          | —        | 0         | C3IP<2:0>            |         | OC3IS     | 6<1:0> | 0000          |

| 1000                        | 1 00                            | 15:0          | —      | —      | —      |         | IC3IP<2:0>  |         | IC3IS<      | <1:0>   | —      |          | —        |           | [3IP<2:0>            |         | T3IS-     |        | 0000          |

| 10D0                        | IPC4                            | 31:16         | —      |        | —      |         | INT4IP<2:0> |         | INT4IS      | <1:0>   | _      | —        | _        | 0         | C4IP<2:0>            |         | OC4IS     | S<1:0> | 0000          |

| 1020                        |                                 | 15:0          | —      | —      | —      |         | IC4IP<2:0>  |         | IC4IS<      | <1:0>   |        | —        | _        | 1         | [4IP<2:0>            |         | T4IS      | <1:0>  | 0000          |

| 10E0                        | IPC5                            | 31:16         | —      | —      | —      |         | AD1IP<2:0>  |         | AD1IS       | -       | _      | —        | _        | 0         | C5IP<2:0>            |         | OC5IS     | S<1:0> | 0000          |

| 1020                        |                                 | 15:0          | —      | _      | —      |         | IC5IP<2:0>  |         | IC5IS<      |         | -      | —        | —        | T5IP<2:0> |                      | T5IS    |           | 0000   |               |

| 10F0                        | IPC6                            | 31:16         | —      | —      | —      |         | CMP1IP<2:0> |         | CMP1IS      |         |        | _        | —        | F         | CEIP<2:0>            |         | FCEIS     | 6<1:0> | 0000          |

| 101 0                       | " 00                            | 15:0          | —      | —      | —      | F       | RTCCIP<2:0> |         | RTCCIS      | 6<1:0>  | —      |          | _        | FS        | CMIP<2:0>            | >       | FSCMI     | S<1:0> | 0000          |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       |       |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------|-------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0                     | U-0   | U-0   | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                       | —     | —     |                   | _                | —                |  |  |  |  |

| 00.40        | U-0               | R-0               | U-0                     | U-0   | U-0   | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | _                       | —     | —     | _                 | —                | —                |  |  |  |  |

| 45.0         | U-0               | R-0               | U-0                     | U-0   | U-0   | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | _                       | —     | _     | _                 | _                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0 | R/W-0 | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | —                 | _                 | TUN<5:0> <sup>(1)</sup> |       |       |                   |                  |                  |  |  |  |  |

### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

### Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| REGISTE      | REGISTER 9-8: DCHXECON: DMA CHANNEL 'X' EVENT CONTROL REGISTER |                            |                   |                   |                   |                   |                  |                  |  |

|--------------|----------------------------------------------------------------|----------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                                              | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0                                                            | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                                                              | —                          | —                 | _                 | —                 | _                 | —                | —                |  |

| 22:40        | R/W-1                                                          | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 23:16        |                                                                | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |

| 15:0         | R/W-1                                                          | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup>                                     |                            |                   |                   |                   |                   |                  |                  |  |

| 7:0          | S-0                                                            | S-0                        | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |

| 7.0          | CFORCE                                                         | CABORT                     | PATEN             | SIRQEN            | AIRQEN            |                   |                  |                  |  |

#### CISTER 0-8. CIETED

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-24 Unimplemented: Read as '0'

bit

bit

bit

bit

bit

bit

| : 31-24 | Unimplemented: Read as '0'                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-16   | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                      |

|         | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                 |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag |

| 15-8    | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                      |

|         | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                            |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | •                                                                                                                                                                |

|         | 00000001 = Interrupt 1 will initiate a DMA transfer                                                                                                              |

| _       | 0000000 = Interrupt 0 will initiate a DMA transfer                                                                                                               |

| :7      | CFORCE: DMA Forced Transfer bit                                                                                                                                  |

|         | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                               |

| 6       | CABORT: DMA Abort Transfer bit                                                                                                                                   |

|         | 1 = A DMA transfer is aborted when this bit is written to a '1'                                                                                                  |

|         | 0 = This bit always reads '0'                                                                                                                                    |

| 5       | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                    |

|         | 1 = Abort transfer and clear CHEN on pattern match                                                                                                               |

|         | 0 = Pattern match is disabled                                                                                                                                    |

| : 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                             |

|         | 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs                                                                                           |

|         |                                                                                                                                                                  |

- - 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

### Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

### Legend:

|                             | 0                 |                  |                           |                    |  |  |

|-----------------------------|-------------------|------------------|---------------------------|--------------------|--|--|

| R = Readable bit W = Writab |                   | W = Writable bit | U = Unimplemented bit, re | bit, read as '0'   |  |  |

|                             | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                          |                    |  |  |

|-------------------|-----------------------------------------------|------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | e bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared                     | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

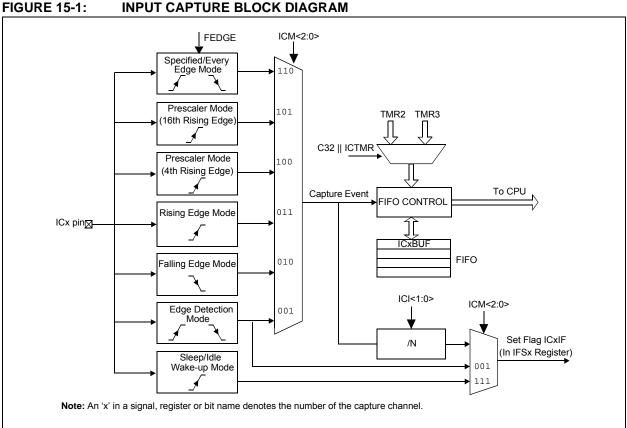

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

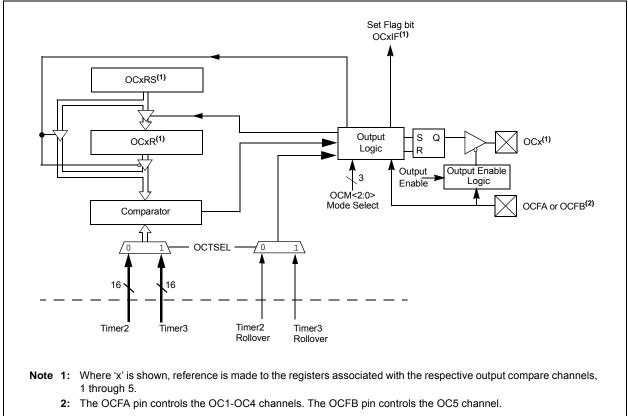

### 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

### 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

| Legend:           | HC = Cleared in Hardware                            |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $l^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2C$  module; all  $I^2C$  pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | —                 | —                 | _                 | _                 |                   | —                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |  |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |  |

| 7:0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | BUFS              |                   |                   | SMP               | BUFM              | ALTS              |                  |                  |  |

### REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVdd               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

#### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

#### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

#### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|--|

|              | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   |                   | DEVID<            | 27:24> <sup>(1)</sup> |                  |  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                   |                   |                       |                  |  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                   |                   |                       |                  |  |  |

| 7:0          | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |  |

|              | DEVID<7:0>(1)               |                   |                     |                   |                   |                   |                       |                  |  |  |

### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| TABLE 30-0.                                                        |                        |      |                                                                                                                                                                                                                                                                                       |                |                 |          |  |  |

|--------------------------------------------------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|----------|--|--|

| DC CHARACT                                                         | ERISTICS               |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                |                 |          |  |  |

| Parameter<br>No.                                                   | Typical <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                                                                                                                                                      |                |                 |          |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Notes 1, 4) |                        |      |                                                                                                                                                                                                                                                                                       |                |                 |          |  |  |

| DC30a                                                              | 1                      | 1.5  | mA                                                                                                                                                                                                                                                                                    | 4 MHz (Note 3) |                 |          |  |  |

| DC31a                                                              | 2                      | 3    | mA                                                                                                                                                                                                                                                                                    | 10 MHz         |                 |          |  |  |

| DC32a                                                              | 4                      | 6    | mA                                                                                                                                                                                                                                                                                    |                | 20 MHz (Note 3) |          |  |  |

| DC33a                                                              | 5.5                    | 8    | mA                                                                                                                                                                                                                                                                                    |                | 30 MHz (Note 3) |          |  |  |

| DC34a                                                              | 7.5                    | 11   | mA                                                                                                                                                                                                                                                                                    |                | 40 MHz          |          |  |  |

| DC37a                                                              | 100                    | _    | μA                                                                                                                                                                                                                                                                                    | -40°C LPRC (31 |                 |          |  |  |

| DC37b                                                              | 250                    | _    | μA                                                                                                                                                                                                                                                                                    | +25°C          | 3.3V            | (Note 3) |  |  |

| DC37c                                                              | 380                    |      | μA                                                                                                                                                                                                                                                                                    | +85°C          | 1               |          |  |  |

### TABLE 30-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)