#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

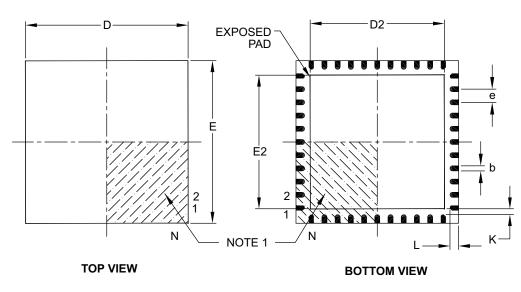

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256b-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                        | Pin Nu                                | mber <sup>(1)</sup>                    |                                        |             |                |                                                                         |

|----------|----------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC     | 36-pin<br>VTLA                         | 44-pin<br>QFN/<br>TQFP/<br>VTLA        | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | <sub>11</sub> (3)                      | 14 <sup>(3)</sup>                     | 15 <b>(3)</b>                          | 41 <sup>(3)</sup>                      | I           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                                     | 2                                     | 33                                     | 19                                     | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                                     | 3                                     | 34                                     | 20                                     | I           | ST             | 7                                                                       |

| CTED3    | 13                                     | 16                                    | 17                                     | 43                                     | I           | ST             | 7                                                                       |

| CTED4    | 15                                     | 18                                    | 19                                     | 1                                      | I           | ST             | 7                                                                       |

| CTED5    | 22                                     | 25                                    | 28                                     | 14                                     | I           | ST             | 7                                                                       |

| CTED6    | 23                                     | 26                                    | 29                                     | 15                                     | I           | ST             | 7                                                                       |

| CTED7    | _                                      | _                                     | 20                                     | 5                                      | I           | ST             | 7                                                                       |

| CTED8    | _                                      |                                       | _                                      | 13                                     | I           | ST             | 7                                                                       |

| CTED9    | 9                                      | 12                                    | 10                                     | 34                                     | I           | ST             | 7                                                                       |

| CTED10   | 14                                     | 17                                    | 18                                     | 44                                     | I           | ST             | 7                                                                       |

| CTED11   | 18                                     | 21                                    | 24                                     | 8                                      | I           | ST             | 7                                                                       |

| CTED12   | 2                                      | 5                                     | 36                                     | 22                                     | I           | ST             | 7                                                                       |

| CTED13   | 3                                      | 6                                     | 1                                      | 23                                     | I           | ST             | 7                                                                       |

| CTPLS    | 21                                     | 24                                    | 27                                     | 11                                     | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                                      | 4                                     | 35                                     | 21                                     | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 1        |

| PGEC1    | 2                                      | 5                                     | 36                                     | 22                                     | Ι           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                                     | 21                                    | 24                                     | 8                                      | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 2        |

| PGEC2    | 19                                     | 22                                    | 25                                     | 9                                      | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup><br>27 <sup>(3)</sup> | 14 <sup>(2)</sup><br>2 <sup>(3)</sup> | 15 <sup>(2)</sup><br>33 <sup>(3)</sup> | 41 <sup>(2)</sup><br>19 <sup>(3)</sup> | I/O         | ST             | Data I/O pin for Programming/Debuggin<br>Communication Channel 3        |

|          | 12 <b>(2)</b>                          | 15 <b>(2)</b>                         | 16 <b>(2)</b>                          | 42 <sup>(2)</sup>                      |             | OT             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup>                      | 3 <b>(3)</b>                          | 34 <sup>(3)</sup>                      | 20 <sup>(3)</sup>                      |             | ST             | Debugging Communication Channel 3                                       |

| PGED4    | —                                      | —                                     | 3                                      | 12                                     | I/O         | ST             | Data I/O pin for Programming/Debuggir<br>Communication Channel 4        |

| PGEC4    | —                                      | —                                     | 4                                      | 13                                     | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer PPS = Peripheral Pin Select

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**2:** Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

— = N/A

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

#### TABLE 3-2: COPROCESSOR 0 REGISTERS

**Note 1:** Registers used in exception processing.

**2:** Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | —                 | _                 |                      | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                    | —                | -                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0            | R/W-0            |

| 15:8         | —                 | _                 |                   | _                 | _                 | S                    | RIPL<2:0>(1)     |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

#### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D''               | Dir              | Dit              |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   |                   |                   | IPTMF             | <31:24>           |                   |                  |                  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |  |  |  |

| 10.0         |                   |                   |                   | IPTM              | R<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7.0          | IPTMR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5390                        | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

|              |                   |                   | COB BOILTE        | DECON             |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | -                 | —                 | -                 | —                 | —                | —                |

| 22:16        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 |                   | —                 | -                 |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

#### REGISTER 10-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

| REGIOT       |                   | UIDDIF5. U        | OD DOI 1 E        |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   | _                 | _                 | —                | —                |

| 23:16        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   |                   |                   | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 |                   |                   |                   | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

#### REGISTER 10-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRU<31:24>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### 13.2 Timer Control Registers

#### TABLE 13-1: TIMER2-TIMER5 REGISTER MAP

|                             | - 15                            |           |       |                 |       |       |             |       |      |      |        |      |            |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|-------|-----------------|-------|-------|-------------|-------|------|------|--------|------|------------|------|------|------|----------|------|------------|

| ess                         |                                 |           |       |                 |       |       |             |       |      | Bi   | its    |      |            |      |      |      |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11       | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5       | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     | _     | _               | —     | _     | —           | —     | —    | —    | —      | -    | —          | _    | —    | _    | _        | -    | 0000       |

| 0000                        | 12001                           | 15:0      | ON    |                 | SIDL  | —     | —           | —     | _    | _    | TGATE  | -    | TCKPS<2:0> | >    | T32  | —    | TCS      | —    | 0000       |

| 0810                        | TMR2                            | 31:16     | —     | —               | —     | —     | —           | —     | _    | —    | —      | —    | —          | —    |      | —    | —        | _    | 0000       |

| 0010                        |                                 | 15:0      |       | TMR2<15:0> 0000 |       |       |             |       |      |      |        |      |            |      |      |      |          |      |            |

| 0820                        | PR2                             | 31:16     | —     |                 |       |       |             |       |      |      |        |      |            |      |      |      |          |      |            |

| 0020                        |                                 | 15:0      |       | PR2<15:0> FFFF  |       |       |             |       |      |      |        |      |            |      |      |      |          |      |            |

| 0040                        | T3CON                           | 31:16     | —     | —               | —     | _     | —           | —     | —    | —    | —      | -    | —          | —    | —    | _    | —        | —    | 0000       |

| 0/100                       | 10001                           | 15:0      | ON    | —               | SIDL  | _     | —           | —     | —    | —    | TGATE  |      | TCKPS<2:0> | >    | —    | _    | TCS      | —    | 0000       |

| 0A10                        | TMR3                            | 31:16     |       | _               | _     | —     | _           | —     |      | —    |        | —    | —          | _    | —    | _    | _        |      | 0000       |

| 0,110                       | -                               | 15:0      |       |                 |       |       |             |       |      | TMR3 | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0A20                        | PR3                             | 31:16     | —     | —               | —     | —     | —           | —     | _    | —    | —      | _    | —          | _    |      | —    | —        |      | 0000       |

|                             | _                               | 15:0      |       |                 |       |       |             |       |      | PR3< | :15:0> |      |            |      |      |      |          |      | FFFF       |

| 0C00                        | T4CON                           | 31:16     | _     | _               | —     | —     | —           | —     | —    | _    | —      | —    | —          | —    | —    | —    | _        | —    | 0000       |

|                             |                                 | 15:0      | ON    | —               | SIDL  | —     | —           |       | _    | —    | TGATE  | -    | TCKPS<2:0  | >    | T32  | —    | TCS      |      | 0000       |

| 0C10                        | TMR4                            | 31:16     | _     | —               | —     | —     | —           | —     | _    | —    | —      | —    | —          | —    | —    | —    | —        | —    | 0000       |

|                             |                                 | 15:0      |       |                 |       |       |             |       |      | TMR4 |        |      |            |      |      |      |          |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _     | —               | —     | —     | —           | —     | _    | -    | —      | _    | —          | _    | —    | _    | —        |      | 0000       |

|                             |                                 | 15:0      |       |                 |       |       |             |       |      |      | :15:0> |      |            |      |      |      |          |      | FFFF       |

| 0E00                        | T5CON                           | 31:16     | -     | _               | -     | _     |             | —     |      | _    |        |      |            |      |      |      | —<br>T00 |      | 0000       |

|                             |                                 | 15:0      | ON    |                 | SIDL  | _     |             |       | _    | _    | TGATE  |      | TCKPS<2:0> |      | _    | _    | TCS      | _    | 0000       |

| 0E10                        | TMR5                            | 31:16     | —     | —               | —     | _     | —           | —     | —    |      |        | _    | —          | —    | —    | _    | —        | _    | 0000       |

| <u> </u>                    |                                 | 15:0      |       |                 |       |       |             |       |      | TMR5 | <15:0> |      |            |      |      |      |          |      | 0000       |

| 0E20                        | PR5                             | 31:16     |       |                 |       |       |             |       |      |      |        |      |            |      |      |      |          |      |            |

|                             |                                 | 15:0      |       |                 |       |       | d a stal Da |       |      |      | 15:02  |      |            |      |      |      |          |      | FFFF       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

|                             |                   |       |       | 0                 |                   |                   |                  |                  |  |

|-----------------------------|-------------------|-------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit Bit<br>Range 31/23/15/7 |                   |       |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24                       | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24                       | —                 | —     | _     | —                 | —                 | —                 | _                | _                |  |

| 22:40                       | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16                       |                   | —     | _     | _                 | _                 | _                 | _                | _                |  |

| 45.0                        | R/W-0             | U-0   | R/W-0 | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8                        | 0N <sup>(1)</sup> | —     | SIDL  | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |

| 7:0                         | R/W-0             | R/W-0 | R/W-0 | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |

| 7:0                         | GCEN              | STREN | ACKDT | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |

| Legend:           | HC = Cleared in Hardware |                          |                    |  |  |  |

|-------------------|--------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2C$  module; all  $I^2C$  pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 | _                 | -                 | —                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | -                |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | red                      |                                |  |  |

|-------------------|----------------------|--------------------------|--------------------------------|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r | Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared     | C = Clearable bit              |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

#### bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> C module is busy |  |

|-------------------------------------------------------------------------------------------------|--|

| 0 = No collision                                                                                |  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

#### bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

#### bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

### **REGISTER 18-2:** I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| bit 4 | <b>P:</b> Stop bit<br>1 = Indicates that a Stop bit has been detected last                                                                                      |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                              |

| bit 3 | S: Start bit                                                                                                                                                    |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                      |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                              |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                               |

|       | 1 = Read – indicates data transfer is output from slave                                                                                                         |

|       | <ul> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                             |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                                           |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                                      |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                                            |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                            |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                                       |

0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

| Bit<br>Range |     |            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----|------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0 | U-0        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _   | _          | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0 | U-0        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -   | _          | _                 | _                 | -                 | _                 | -                | —                |

| 45.0         | R-0 | R/W-0, HSC | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF | IBOV       | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1 | R/W-0, HSC | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE | OBUF       | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 20-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HSC = Set by Hardware; Cleared by Software |                          |                    |  |  |  |

|-------------------|--------------------------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                           | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set                           | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

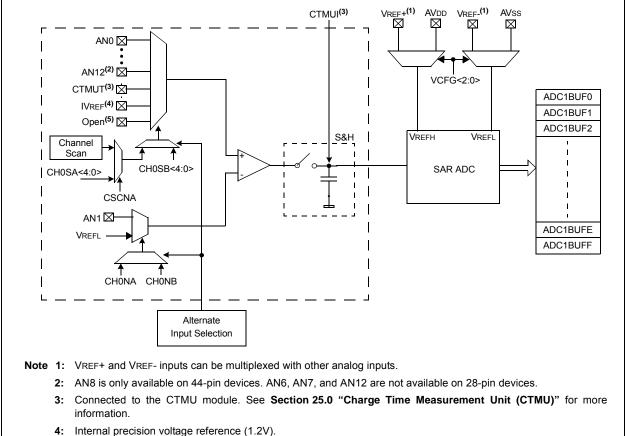

#### 22.0 **10-BIT ANALOG-TO-DIGITAL** CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

**FIGURE 22-1:**

- Up to 13 analog input pins

- External voltage reference input pins

- · One unipolar, differential Sample and Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### 5: This selection is only used with CTMU capacitive and time measurement.

ADC1 MODULE BLOCK DIAGRAM

#### 22.1 **ADC Control Registers**

#### TABLE 22-1: ADC REGISTER MAP

| $ \frac{5}{900} = \frac{1}{150} = 1$ | ess                      |                        |           |        |           |        |        |        |        |          | Bi          | ts       |           |       |         |         |       |        |       |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|-----------|--------|-----------|--------|--------|--------|--------|----------|-------------|----------|-----------|-------|---------|---------|-------|--------|-------|------------|

| 900         ADICONI(***)         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Virtual Addr<br>(BF80_#) |                        | Bit Range | 31/15  | 30/14     | 29/13  | 28/12  | 27/11  | 26/10  | 25/9     | 24/8        | 23/7     | 22/6      | 21/5  | 20/4    | 19/3    | 18/2  | 17/1   | 16/0  | All Resets |

| 150         ON         -         SIDL         -         -         ONM         SIRC20>         CRRSM         -         AM         SMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | AD1CON1(1)             | 31:16     | _      | —         | _      |        | _      |        | _        | —           |          |           | —     | —       | —       | —     | _      | —     | 0000       |

| 9010         ADICONUN         15.0         VCFG<2.0>         OFFCAL         —         CSCNA         —         —         BUFS         —         SMPI<3:0>         BUFM         A           9020         ADICON301         31:16         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         DC         ADC         ADC         AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9000                     | ADICONIC               | 15:0      | ON     | _         | SIDL   | —      | _      | -      | ORM<2:0> | >           |          | SSRC<2:0> | >     | CLRASAM | _       | ASAM  | SAMP   | DONE  | 0000       |

| Image: constraint of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9010                     |                        |           |        | —         |        |        | —      | —      | _        | —           | —        | _         |       | —       | —       | —     | _      |       | 0000       |

| 9020       ADICON3       15:0       ADRC       -       -       -       CHOSR       ADCS<7:0>       CHOSR       ADCS<7:0>         9040       ADICHS(1)       11:6       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>0010</td> <td></td> <td></td> <td>,</td> <td>VCFG&lt;2:0&gt;</td> <td></td> <td>OFFCAL</td> <td>—</td> <td>CSCNA</td> <td>—</td> <td>—</td> <td>BUFS</td> <td>—</td> <td></td> <td>SMPI</td> <td>&lt;3:0&gt;</td> <td></td> <td>BUFM</td> <td>ALTS</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0010                     |                        |           | ,      | VCFG<2:0> |        | OFFCAL | —      | CSCNA  | —        | —           | BUFS     | —         |       | SMPI    | <3:0>   |       | BUFM   | ALTS  | 0000       |

| Image: Normal and the state of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9020                     | AD1CON3 <sup>(1)</sup> |           | —      | —         | —      |        | —      | —      |          | —           | —        | —         | —     |         | —       | —     | —      | —     | 0000       |

| 9040         AD1CHSIVI<br>15.0         Image: Constraint of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0020                     |                        |           | -      | —         | —      |        | Ś      |        |          |             |          |           |       | ADCS    | \$<7:0> |       |        |       | 0000       |

| Image: 100 mining of the second of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9040                     | AD1CHS <sup>(1)</sup>  |           | CH0NB  | _         |        | —      |        | CH0SE  | 3<3:0>   |             | CH0NA    | _         | _     |         |         | CH0S/ | 4<3:0> |       | 0000       |

| 9050         AD1CSSL®         15.0         CSSL15         CSSL14         CSSL13         CSSL12         CSSL11         CSSL10         CSSL8         CSSL7         CSSL6         CSSL6         CSSL4         CSSL3         CSSL2         CSSL1         CSSL1         CSSL3         CSSL3         CSSL3         CSSL3         CSSL3         CSSL1         CSSL1         CSSL1         CSSL1         CSSL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |                        |           | _      | _         |        | —      | —      | —      | _        | —           | —        | _         | _     |         | —       | _     |        | —     | 0000       |

| International conduction         Status         Cost 13         Cost 13         Cost 13         Cost 13         Cost 13         Cost 13         Cost 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9050                     | AD1CSSL <sup>(1)</sup> |           |        | —         | —      | —      | _      | —      |          | —           | _        |           |       | —       | —       |       |        | —     | 0000       |