#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 19                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                          |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256b-v-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### **Pin Diagrams**

#### TABLE 3: **PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES**

| 28                                                    | -PIN SOIC, SPDIP, SSOP (TOP VIEW) <sup>(1,2,3</sup>                                                                                                                                                                                                                                                                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |                                                                                                                           |                                                                                            |                                                                             |                                                         |          |         |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------|----------|---------|

|                                                       | 1<br>SSOI<br>PIC32MX110F016B<br>PIC32MX120F032B<br>PIC32MX130F064B<br>PIC32MX130F256B                                                                                                                                                                                                                                                                    | 28<br>ס                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  | 1<br>SC                                                                                                                   | JIC                                                                                        | 28                                                                          | 1                                                       | SPDIP    | 28      |

|                                                       | PIC32MX150F128B<br>PIC32MX170F256B                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |                                                                                                                           |                                                                                            |                                                                             |                                                         |          |         |

| Din #                                                 | Full Bin Name                                                                                                                                                                                                                                                                                                                                            | p;                                                                                                                                                                                                                                                                                                                                                                                                                                        | . #                                                                              |                                                                                                                           |                                                                                            | Eull Bin                                                                    | Nama                                                    |          |         |

| Pin #                                                 | Full Pin Name                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                           | n #                                                                              |                                                                                                                           |                                                                                            | Full Pin                                                                    | Name                                                    |          |         |

| 1                                                     | MCLR                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 F                                                                              | PGEC3/RPB                                                                                                                 |                                                                                            | RB6                                                                         |                                                         |          |         |

| 1<br>2                                                | MCLR<br>VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 F<br>6 T                                                                       | DI/RPB7/C                                                                                                                 | TED3/PN                                                                                    | RB6<br>ID5/INT0/F                                                           | RB7                                                     |          |         |

| 1<br>2<br>3                                           | MCLR<br>VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0<br>VREF-/CVREF-/AN1/RPA1/CTED2/RA1                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 F<br>6 7<br>7 7                                                                | TDI/RPB7/C<br>TCK/RPB8/S                                                                                                  | TED3/PM<br>SCL1/CTE                                                                        | RB6<br>ID5/INT0/F<br>ED10/PMD                                               | RB7<br>04/RB8                                           |          |         |

| 1<br>2<br>3<br>4                                      | MCLR<br>VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0<br>VREF-/CVREF-/AN1/RPA1/CTED2/RA1<br>PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 F<br>6 1<br>7 1<br>8 1                                                         | IDI/RPB7/C<br>ICK/RPB8/S<br>IDO/RPB9/S                                                                                    | TED3/PM<br>SCL1/CTE                                                                        | RB6<br>ID5/INT0/F<br>ED10/PMD                                               | RB7<br>04/RB8                                           |          |         |

| 1<br>2<br>3<br>4<br>5                                 | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 F<br>6 7<br>7 7<br>8 7<br>9 \                                                  | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/ss                                                                             | TED3/PM<br>SCL1/CTE                                                                        | RB6<br>ID5/INT0/F<br>ED10/PMD                                               | RB7<br>04/RB8                                           |          |         |

| 1<br>2<br>3<br>4                                      | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 F<br>6 7<br>7 7<br>8 7<br>9 \<br>0 \                                           | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/ss<br>/cap                                                                     | TED3/PM<br>SCL1/CTE<br>SDA1/CTI                                                            | RB6<br>ID5/INT0/F<br>ED10/PME<br>ED4/PMD                                    | RB7<br>04/RB8<br>3/RB9                                  |          |         |

| 1<br>2<br>3<br>4<br>5<br>6                            | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INB/C3IND/RPB1/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2     AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3                                                                                              | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>2<br>2                                                                                                                                                                                                                                                                                                                                                                                                 | 5 F<br>6 1<br>7 7<br>8 1<br>9 \<br>0 \<br>1 F                                    | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/SS<br>/CAP<br>PGED2/RPB                                                        | TED3/PM<br>SCL1/CTE<br>SDA1/CTI                                                            | RB6<br>1D5/INT0/f<br>ED10/PME<br>ED4/PMD2<br>011/PMD2/                      | RB7<br>)4/RB8<br>3/RB9<br>/RB10                         |          |         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                       | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2                                                                                                                                           | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2                                                                                                                                                                                                                                                                                                                                                                                       | 5 F<br>6 7<br>7 1<br>8 7<br>9 \<br>0 \<br>1 F<br>2 F                             | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/ss<br>/cap                                                                     | TED3/PM<br>SCL1/CTE<br>SDA1/CTI<br>10/CTED                                                 | RB6<br>1D5/INT0/f<br>ED10/PME<br>ED4/PMD2<br>011/PMD2/                      | RB7<br>)4/RB8<br>3/RB9<br>/RB10                         |          |         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                  | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2     AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3     Vss                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 F<br>6 7<br>7 7<br>8 7<br>9 \<br>0 \<br>1 F<br>2 F<br>3 4                      | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/SS<br>/CAP<br>PGED2/RPB<br>PGEC2/TMS                                           | TED3/PM<br>SCL1/CTE<br>SDA1/CTI<br>10/CTED<br>S/RPB11/F<br>/RB12                           | RB6<br>ID5/INT0/I<br>ED10/PME<br>ED4/PMD2<br>011/PMD2<br>PMD1/RB            | RB7<br>)4/RB8<br>3/RB9<br>/RB10<br>11                   |          |         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9             | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2     AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3     Vss     OSC1/CLKI/RPA2/RA2                                                                     | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                                                                                                                                                                                                                                                                                                                                          | 5 F<br>6 7<br>7 7<br>8 7<br>9 \<br>0 \<br>1 F<br>2 F<br>3 4<br>4 /               | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/SS<br>/CAP<br>PGED2/RPB<br>PGEC2/TMS<br>PGEC2/TMS                              | TED3/PM<br>SCL1/CTE<br>SDA1/CTI<br>SDA1/CTE<br>SDA1/CTED<br>S/RPB11/F<br>/RB12<br>S/CTPLS/ | RB6<br>ID5/INT0/I<br>ED10/PME<br>ED4/PMD2<br>011/PMD2<br>PMD1/RB<br>PMRD/RE | RB7<br>)4/RB8<br>3/RB9<br>/RB10<br>11<br>313            | CTED5/PM |         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10       | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INB/C3IND/RPB0/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2     AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3     Vss     OSC1/CLKI/RPA2/RA2     OSC2/CLKO/RPA3/PMA0/RA3 | 1       1       1       1       1       1       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2                                                                                                                                                                                                                                 | 5 F<br>6 1<br>7 1<br>8 1<br>9 \<br>0 \<br>1 F<br>2 F<br>3 /<br>4 /<br>5 (        | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/ss<br>/cap<br>PGED2/RPB<br>PGEC2/TMS<br>AN12/PMD0<br>AN11/RPB13                | TED3/PM<br>SCL1/CTE<br>SDA1/CTI<br>SDA1/CTI<br>S/RPB11/f<br>/RB12<br>3/CTPLS/<br>N10/C3IN  | RB6<br>ID5/INT0/I<br>ED10/PME<br>ED4/PMD2<br>PMD1/RB<br>PMRD/RE<br>PMRD/RE  | RB7<br>)4/RB8<br>3/RB9<br>/RB10<br>11<br>313<br>/SCK1/( |          | WR/RB14 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | MCLR     VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0     VREF-/CVREF-/AN1/RPA1/CTED2/RA1     PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0     PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1     AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2     AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3     Vss     OSC1/CLKI/RPA2/RA2     OSC2/CLKO/RPA3/PMA0/RA3     SOSCI/RPB4/RB4                      | 1       1       1       1       1       1       1       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       1       1       1       1       1       2       2       2       2       2       2 | 5 F<br>6 7<br>7 7<br>8 7<br>9 \<br>0 \<br>1 F<br>2 F<br>3 4<br>4 4<br>5 (<br>6 4 | TDI/RPB7/C<br>TCK/RPB8/S<br>TDO/RPB9/S<br>/SS<br>/CAP<br>PGED2/RPB<br>PGEC2/TMS<br>AN12/PMD0.<br>AN11/RPB13<br>CVREFOUT/A | TED3/PM<br>SCL1/CTE<br>SDA1/CTI<br>SDA1/CTI<br>S/RPB11/f<br>/RB12<br>3/CTPLS/<br>N10/C3IN  | RB6<br>ID5/INT0/I<br>ED10/PME<br>ED4/PMD2<br>PMD1/RB<br>PMRD/RE<br>PMRD/RE  | RB7<br>)4/RB8<br>3/RB9<br>/RB10<br>11<br>313<br>/SCK1/( |          | WR/RB14 |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

Shaded pins are 5V tolerant. 3:

#### TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

# 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

| Pin # | Full Pin Name                        | Pi | in # | Full Pin Name                                  |

|-------|--------------------------------------|----|------|------------------------------------------------|

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 | 1  | 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   | 2  | 20   | RPC9/CTED7/RC9                                 |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   | 2  | 21   | Vss                                            |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   | 2  | 22   | VCAP                                           |

| 5     | Vdd                                  | 2  | 23   | Vdd                                            |

| 6     | Vss                                  | 2  | 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 7     | OSC1/CLKI/RPA2/RA2                   | 2  | 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              | 2  | 26   | AN12/PMD0/RB12                                 |

| 9     | SOSCI/RPB4/RB4                       | 2  | 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       | 2  | 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 11    | RPC3/RC3                             | 2  | 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 12    | Vss                                  | 3  | 30   | AVss                                           |

| 13    | Vdd                                  | 3  | 31   | AVdd                                           |

| 14    | Vdd                                  | 3  | 32   | MCLR                                           |

| 15    | PGED3/RPB5/PMD7/RB5                  | 3  | 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 16    | PGEC3/RPB6/PMD6/RB6                  | 3  | 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         | 3  | 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        | 3  | 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

|          |                        | Pin Nu                            | mber <sup>(1)</sup> | -                               |             |                |                                           |

|----------|------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                  | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                   | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                   | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                  | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                     | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                     | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                   | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                     | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                  | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                   | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                   | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                   | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                  | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                  | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                  | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                  | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                  | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                  | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                  | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                  | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                  | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                     |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                     |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe        | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

####

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

#### TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | ¢,        |       |       |       |       |             |       |             | Bits   |             |      |             |             |             |        |             |                  |               |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|-------------|--------|-------------|------|-------------|-------------|-------------|--------|-------------|------------------|---------------|--|--------------|---|--------|-------------|--|-------------|--|---------------|--|-------------|--|-------------|--|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9        | 24/8   | 23/7        | 22/6 | 21/5        | 20/4        | 19/3        | 18/2   | 17/1        | 16/0             | All<br>Resets |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

| 1100                        | 1007                            | 31:16     | _     | —     | —     |       | SPI1IP<2:0> |       | SPI1IS      | S<1:0> | -           | —    | —           | US          | SBIP<2:0>(2 | :)     | USBIS       | <1:0> <b>(2)</b> | 0000          |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

| 1100                        | IPC7                            | 15:0      | _     | -     | —     | (     | CMP3IP<2:0> |       | CMP3IS<1:0> |        | _           | _    | _           | CMP2IP<2:0> |             | •      | CMP2IS<1:   |                  | 0000          |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

| 1110                        | IPC8                            | 31:16     | _     | _     | —     |       | PMPIP<2:0>  |       | PMPIS       | S<1:0> | _           | —    | _           | (           | CNIP<2:0>   |        | CNIS        | <1:0>            | 0000          |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

| 1110                        | IPCo                            | 15:0      |       | —     | _     |       | I2C1IP<2:0> |       | I2C1IS<1:0> |        |             |      | _           | U1IP<2:0>   |             |        | 2:0> U1IS<1 |                  | 0000          |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

| 1120                        | IPC9                            | 31:16     |       | —     | _     | (     | CTMUIP<2:0  | >     | CTMU        | S<1:0> | —           | —    | I2C2IP<2:0> |             |             | 12C218 | 6<1:0>      | 0000             |               |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

| 1120                        | IFC9                            | 15:0      | -     | —     | _     |       | U2IP<2:0>   |       | U2IS<1:0>   |        | U2IS<1:0>   |      | U2IS<1:0>   |             | U2IS<1:0>   |        | U2IS<1:0>   |                  | SPI2IP<2:0>   |  | 0> SPI2IS<1: |   | S<1:0> | 0000        |  |             |  |               |  |             |  |             |  |      |

| 1130                        | IPC10                           | 31:16     | —     | _     | —     | [     | DMA3IP<2:0> |       | DMA3IS<1:0> |        | DMA3IS<1:0> |      | DMA3IS<1:0> |             | DMA3IS<1:0> |        | DMA3IS<1:0> |                  | DMA3IS<1:0>   |  | _            | — | _      | DMA2IP<2:0> |  | DMA2IP<2:0> |  | - DMA2IP<2:0> |  | DMA2IP<2:0> |  | DMA2IS<1:0> |  | 0000 |

| 1130                        | IFC IU                          | 15:0      | _     | _     | _     | [     | DMA1IP<2:0> |       |             | S<1:0> | _           | _    | _           | DI          | VA0IP<2:0   | •      | DMA0I       | S<1:0>           | 0000          |  |              |   |        |             |  |             |  |               |  |             |  |             |  |      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS01<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-2 | IP00<2:0>: Interrupt Priority bits                                                                                    |

|         | 111 = Interrupt priority is 7                                                                                         |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | •                                                                                                                     |

|         | 010 = Interrupt priority is 2                                                                                         |

|         | 001 = Interrupt priority is 1                                                                                         |

|         | 000 = Interrupt is disabled                                                                                           |

| bit 1-0 | IS00<1:0>: Interrupt Subpriority bits                                                                                 |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

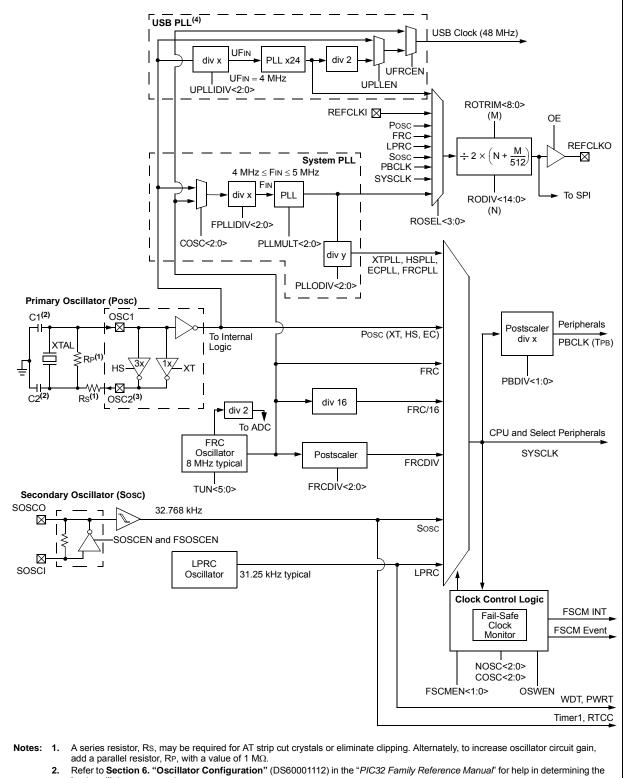

#### FIGURE 8-1: OSCILLATOR DIAGRAM

Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determinin best oscillator components.

3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

4. The USB PLL is only available on PIC32MX2XX devices.

#### TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 |                        |        |       |       |       |        |       |      | Bi                   | ts      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|------------------------|--------|-------|-------|-------|--------|-------|------|----------------------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range              | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8                 | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16                  | —      | _     | —     | _     |        | _     | _    | _                    | _       |        | -      | _      | -      | —      | _      | _      | 0000       |

| 5170                        | DOITIOOIZ                       | 15:0                   |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3180                        | DCH1DSIZ                        | 31:16                  | _      | _     | —     | —     | —      | —     | _    | -                    | —       | —      | _      |        | _      | —      | _      | —      | 0000       |

| 5100                        | DOITIDOIZ                       | 15:0                   |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16                  | _      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | _      | _      | 0000       |

| 0100                        |                                 | 15:0                   |        |       |       |       |        |       |      | CHSPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16                  | —      | —     | —     | —     | —      | —     | —    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

| 017.00                      |                                 | 15:0                   |        |       |       |       |        |       |      |                      |         |        |        |        |        | 0000   |        |        |            |

| 31B0                        | DCH1CSIZ                        | 31:16                  |        |       |       |       |        |       |      |                      |         |        |        |        | 0000   |        |        |        |            |

| 0.20                        |                                 | 15:0                   |        |       |       |       |        |       |      | CHCSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16                  | _      | _     | _     | —     | —      | —     | _    | _                    | —       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.00                        |                                 | 15:0                   |        |       |       |       |        |       |      | CHCPTI               | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16                  | —      | _     | —     | —     | —      | —     | —    | _                    | _       | —      | —      |        | —      | —      | —      |        | 0000       |

| 0.20                        |                                 | 15:0                   | —      | _     | —     | —     | —      | —     | —    | _                    |         |        |        | CHPDA  |        |        |        |        | 0000       |

| 31F0                        | DCH2CON                         | 31:16                  | —      | _     | —     | —     | —      | —     | —    | _                    |         |        | —      | _      | _      | —      | —      |        | 0000       |

| 0.20                        |                                 |                        | CHBUSY | _     | _     | —     | _      | _     |      | CHCHNS               | CHEN    | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | <1:0>  | 0000       |

| 31F0                        | DCH2ECON                        | 31:16                  | _      | _     | —     | —     | —      | —     | _    | _                    |         |        |        | CHAIR  |        |        |        |        | 00FF       |

|                             |                                 | 15:0                   |        |       |       | CHSIR | Q<7:0> |       |      |                      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      | —      | —      | FF00       |

| 3200                        | DCH2INT                         | 31:16                  | —      | —     | —     | —     | —      | —     | _    | —                    | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0                   | _      | _     |       | —     | —      | —     |      |                      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16                  |        |       |       |       |        |       |      | CHSSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0                   |        |       |       |       |        |       |      |                      |         |        |        |        |        |        |        |        | 0000       |

| 3220                        |                                 | 31:16                  |        |       |       |       |        |       |      | CHDSA                | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0                   |        |       |       |       |        |       |      | 1                    |         |        |        |        |        |        |        |        | 0000       |

| 3230                        | DCH2SSIZ                        | 31:16                  |        | —     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0                   |        |       |       |       |        |       |      | CHSSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3240                        | DCH2DSIZ                        | 31:16                  |        |       | —     | _     | —      | _     | _    | <u> </u>             | —       | —      | —      | —      | —      | —      | _      | —      | 0000       |

|                             |                                 | 15:0                   |        |       |       |       |        |       |      | CHDSIZ               | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3250                        | DCH2SPTR                        | SPTRI                  |        |       |       |       |        |       |      |                      |         |        | 0000   |        |        |        |        |        |            |

|                             |                                 | 15:0 CHSP1R<15:0> 00   |        |       |       |       |        |       |      |                      |         |        | 0000   |        |        |        |        |        |            |

| 3260                        | DCH2DPTR                        | 31:16                  |        |       | —     | _     | —      | _     | _    | —                    | —       | —      | —      | —      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0 CHDPTR<15:0> 0000 |        |       |       |       |        |       |      |                      |         |        |        |        |        |        |        |        |            |

| 3270                        | DCH2CSIZ                        | 31:16                  |        | _     | —     | —     | —      | —     | —    |                      | —       | —      | —      | —      | —      | —      | _      |        | 0000       |

|                             |                                 | 15:0                   |        |       |       |       |        |       |      | CHCSI2<br>exadecimal |         |        |        |        |        |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 51.24        |                   |                   | —                 | —                 | —                 | —                 | —                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23.10        | -                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         | _                 | —                 | _                 | _                 | —                 | _                 | _                     | —                                                |

|              | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       |                                               |

- 1 = STALL interrupt is enabled

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 = ATTACH interrupt is enabled 0 = ATTACH interrupt is disabled

- bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

#### DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

# 12.2 Timer1 Control Registers

### TABLE 12-1: TIMER1 REGISTER MAP

| ess                       |                                 | 0         | © Bits |       |       |       |       |       |      |      |        |      |       |        |      | s     |      |      |            |

|---------------------------|---------------------------------|-----------|--------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | _      | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON     | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —      | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      |        |       |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000       |

| 0620                      | PR1                             | 31:16     | —      | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                             | 15:0      |        |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# 14.1 Watchdog Timer Control Registers

# TABLE 14-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                       |                                 | 6         | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |      | s    |      |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                      | WDTCON                          | 31:16     | _     | —     | _     | —     | _     |       | _    | _    | -    | _    | —    | _    | _    | —    | -    | —    | 0000       |

| 0000                      | WDICON                          | 15:0      | ON    |       |       |       |       |       |      |      |      |      |      |      |      | 0000 |      |      |            |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        | —                 | —                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          |                   | —                 | _                 |                   | _                 | -                 | —                | —                |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

NOTES:

## 26.0 POWER-SAVING FEATURES

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

### 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

#### 26.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 26-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| TABLE 26-1: | PERIPHERAL MODULE DISABLE BITS AND LOCATIONS |  |

|-------------|----------------------------------------------|--|

|             |                                              |  |

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМU                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| I2C1                         | I2C1MD                       | PMD5<16>                       |

| I2C2                         | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

2: The module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

| TABLE 30-0.                                                        |                        |      |                                                      |                 |                 |               |  |  |  |

|--------------------------------------------------------------------|------------------------|------|------------------------------------------------------|-----------------|-----------------|---------------|--|--|--|

| DC CHARACT                                                         | ERISTICS               |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                 |                 |               |  |  |  |