#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 19                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256bt-50i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 9: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

## 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

44

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

#### 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

#### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGERMULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming™ (ICSP™)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.04        | U-0                | U-0                |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | -                  | —                  |

| 22:16        | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 |                   | -                  | —                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         |                   | _                 | _                 | -                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-10 Unimplemented: Read as '0'

| bit 9 | CMR: Configuration Mismatch Reset Flag bit             |

|-------|--------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred          |

|       | 0 = Configuration mismatch Reset has not occurred      |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit            |

|       | 1 = Regulator is enabled and is on during Sleep mode   |

|       | 0 = Regulator is disabled and is off during Sleep mode |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit               |

|       | 1 = Master Clear (pin) Reset has occurred              |

|       | 0 = Master Clear (pin) Reset has not occurred          |

| bit 6 | SWR: Software Reset Flag bit                           |

|       | 1 = Software Reset was executed                        |

|       | 0 = Software Reset as not executed                     |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                 |

|       | 1 = WDT Time-out has occurred                          |

|       | 0 = WDT Time-out has not occurred                      |

| bit 3 | SLEEP: Wake From Sleep Flag bit                        |

|       | 1 = Device was in Sleep mode                           |

|       | 0 = Device was not in Sleep mode                       |

| bit 2 | IDLE: Wake From Idle Flag bit                          |

|       | 1 = Device was in Idle mode                            |

|       | 0 = Device was not in Idle mode                        |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>           |

|       | 1 = Brown-out Reset has occurred                       |

|       | 0 = Brown-out Reset has not occurred                   |

| bit 0 | POR: Power-on Reset Flag bit <sup>(1)</sup>            |

|       | 1 = Power-on Reset has occurred                        |

|       | 0 = Power-on Reset has not occurred                    |

|       |                                                        |

**Note 1:** User software must clear this bit to view next detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |

| 31:24        | _                 | _                 | _                       | —                 | _                 |                   | _                         | —                |  |

| 23:16        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |

| 23.10        | —                 | —                 | —                       | —                 | —                 | —                 | —                         | -                |  |

| 45.0         | U-0               | U-0               | U-0                     | U-0               | U-0               | R/W-0             | R/W-0                     | R/W-0            |  |

| 15:8         |                   | _                 |                         | _                 | _                 | S                 | SRIPL<2:0> <sup>(1)</sup> |                  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |

| 7:0          | _                 | _                 | VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                           |                  |  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

#### Legend:

| Legena.                         |                  |                                    |                    |  |  |

|---------------------------------|------------------|------------------------------------|--------------------|--|--|

| = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D''               | Dir              | Dit              |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | IPTMR<7:0>        |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   | ROTRIM<8:1>       |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

#### Legend:

| Logona.           |                         |                      |                    |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | le bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   |                   |                   | DCRCDAT           | 4<31:24>          |                   |                  |                  |  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   | DCRCDATA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | DCRCXOR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | _                 | —                 | -                 | —                 | -                 | —                 | —                | —                |  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | -                 | _                 |                   | —                 | -                 |                   |                  | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         | _                 | —                 | _                 | —                 | -                 | —                 | —                | —                |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   | BDTPTRH<23:16>    |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 10-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

| REGIOT       | dister 10-13. UTBDTF3. USB BUTTER DESCRIPTOR TABLE FAGE 3 REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|--------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 31:24        | U-0                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                                                                  | —                 |                   |                   | _                 | _                 | —                | —                |  |  |  |  |

| 23:16        | U-0                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | _                                                                  |                   |                   |                   |                   |                   | _                | _                |  |  |  |  |

| 15:8         | U-0                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | —                                                                  | _                 |                   |                   |                   | -                 | —                | —                |  |  |  |  |

| 7:0          | R/W-0                                                              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | BDTPTRU<31:24>                                                     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 10-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRU<31:24>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                           |                      |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |       |      |            |

|------------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|-------|------|------------|

| Virtual Address<br>(BF80_#)  | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0 | All Resets |

| 5000                         | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —     | —     | —    | 0000       |

| FB8C                         | RPCoR                | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8  | <3:0> |      | 0000       |

| 5000                         | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —     | —     |      | 0000       |

| FB90 RPC9R <sup>(3)</sup> 15 | 15:0                 | —         | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    |      | RPC  | <3:0> |       | 0000 |            |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

## 18.1 I2C Control Registers

# TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |              |            |           |              |              |              |              | Bi         | ts        |                  |                |              |           |          |           |          |            |

|-----------------------------|---------------------------------|---------------|--------------|------------|-----------|--------------|--------------|--------------|--------------|------------|-----------|------------------|----------------|--------------|-----------|----------|-----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14      | 29/13     | 28/12        | 27/11        | 26/10        | 25/9         | 24/8       | 23/7      | 22/6             | 21/5           | 20/4         | 19/3      | 18/2     | 17/1      | 16/0     | All Resets |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON      |            | —<br>SIDL | —<br>SCLREL  | —<br>STRICT  | —<br>A10M    | —<br>DISSLW  | —<br>SMEN  | —<br>GCEN | —<br>STREN       | —<br>ACKDT     | —<br>ACKEN   | —<br>RCEN | —<br>PEN | —<br>RSEN | —<br>SEN | 0000       |

|                             | 100 10717                       | 31:16         | _            | _          | _         | _            | _            | _            | _            | _          | _         | _                | _              | _            | _         | _        | _         | _        | 0000       |

| 5010                        | I2C1STAT                        | 15:0          | ACKSTAT      | TRSTAT     | _         | _            | _            | BCL          | GCSTAT       | ADD10      | IWCOL     | I2COV            | D_A            | Р            | S         | R_W      | RBF       | TBF      | 0000       |

| 5000                        | I2C1ADD                         | 31:16         | _            | _          | _         | —            | —            | -            | —            | _          | —         | _                | _              | _            | -         | _        | _         | _        | 0000       |

| 5020                        | IZCIADD                         | 15:0          | _            | —          | _         | —            | —            | _            |              |            |           |                  | Address        | Register     |           |          |           |          | 0000       |

| 5030                        | I2C1MSK                         | 31:16         | _            | _          |           | -            | -            |              | —            | _          | _         | _                | -              | _            |           | _        | _         | _        | 0000       |

| 5050                        | 120 11031                       | 15:0          | _            | —          |           | -            | -            |              |              |            |           |                  | Address Ma     | ask Register | ſ         |          |           |          | 0000       |

| 5040                        | I2C1BRG                         | 31:16         | _            | —          | _         |              | _            | —            | —            | —          | _         | —                | _              | —            | —         | —        | —         | —        | 0000       |

| 0040                        | 1201BIXO                        | 15:0          | —            | —          | _         | —            |              |              |              |            | Bau       | id Rate Ger      | erator Reg     | ister        |           |          |           |          | 0000       |

| 5050                        | I2C1TRN                         | 31:16         | —            | —          | —         | —            | —            | —            | —            | —          | —         | —                | —              | —            | —         |          | —         | —        | 0000       |

|                             |                                 | 15:0          | _            | —          | _         | —            | —            | _            | —            | _          |           |                  |                | Transmit     | Register  |          |           |          | 0000       |

| 5060                        | I2C1RCV                         | 31:16         | _            | _          |           |              |              |              |              | _          | _         | —                |                | —            | —         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | _            | —          |           |              | —            |              | —            | _          |           |                  |                | Receive      |           |          |           |          | 0000       |

| 5100                        | I2C2CON                         | 31:16         | _            | —          | _         | —            | —            | _            | —            | _          | —         | —                | _              | —            | _         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | ON           | _          | SIDL      | SCLREL       | STRICT       | A10M         | DISSLW       | SMEN       | GCEN      | STREN            | ACKDT          | ACKEN        | RCEN      | PEN      | RSEN      | SEN      | 1000       |

| 5110                        | I2C2STAT                        | 31:16         | -            | -          |           |              |              | -            | —            | -          |           | —                | —              | -            | _         | _        | -         | -        | 0000       |

|                             |                                 |               | ACKSTAT      | TRSTAT     |           | —            | —            | BCL          | GCSTAT       | ADD10      | IWCOL     | I2COV            | D_A            | Р            | S         | R_W      | RBF       | TBF      | 0000       |

| 5120                        | I2C2ADD                         | 31:16         | _            | _          | —         | _            | _            | _            | _            | _          | _         | _                |                | —            | _         | _        |           | _        | 0000       |

|                             |                                 | 15:0<br>31:16 |              |            |           | —            |              |              |              |            |           |                  | Address        | Register     |           |          |           |          | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _            |            | _         |              |              |              | _            | _          | _         | _                | <br>Addross Mr | ask Register | -         | _        | _         | _        | 0000       |

|                             |                                 | 31:16         | _            | _          |           |              | _            | _            |              |            |           |                  |                |              |           |          |           | _        | 0000       |

| 5140                        | I2C2BRG                         | 15:0          | _            |            |           | _            |              |              |              |            | Bai       | I<br>Id Rate Ger | erator Reg     | ister        |           |          |           |          | 0000       |

|                             |                                 | 31:16         | _            | _          | _         |              | _            | _            | _            | _          |           | _                | _              | _            | _         |          | _         | _        | 0000       |

| 5150                        | I2C2TRN                         | 15:0          | _            | _          | _         | _            | _            | _            | _            | _          |           |                  |                | Transmit     | Register  |          |           |          | 0000       |

|                             |                                 | 31:16         | _            | _          | _         | _            | _            | _            | _            | _          | _         | _                | _              | _            | _         |          | _         | _        | 0000       |

| 5160                        | I2C2RCV                         | 15:0          | _            | _          | _         | _            | _            | _            | _            | _          |           |                  |                | Receive      | Register  |          |           |          | 0000       |

| Legen                       | d: x=u                          | nknow         | n value on l | Reset; — = | unimpleme | nted, read a | as '0'. Rese | t values are | e shown in h | exadecimal |           |                  |                |              | •         |          |           |          |            |

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0                   | U-0                | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                       | _                  | -                 | _                 | -                 | -                 | _                | _                |  |  |

| 23:16        | U-0                   | U-0                | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:10        | —                     | —                  |                   | _                 |                   | _                 | _                | _                |  |  |

|              | U-0                   | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                       | CS1 <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |  |

|              | ADDR14 <sup>(2)</sup> |                    |                   |                   |                   |                   | ADDR<10:8>       |                  |  |  |

| 7:0          | R/W-0                 | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | ADDR<7:0>             |                    |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 14 **CS1:** Chip Select 1 bit<sup>(1)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Destination Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

|              |                          |                      |                    | OOMINGE IN              |                   |                   |                  |                  |  |  |  |

|--------------|--------------------------|----------------------|--------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                        | -                    | —                  | —                       | _                 | —                 | _                | _                |  |  |  |

| 22:16        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                        | -                    | —                  | —                       | _                 | —                 | _                | —                |  |  |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> |                   | AMASK             | <3:0> <b>(2)</b> |                  |  |  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                         |                   |                   |                  |                  |  |  |  |

| 1.0          | ARPT<7:0>/²/             |                      |                    |                         |                   |                   |                  |                  |  |  |  |

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

#### bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved; do not use

- 1011 = Reserved; do not use

- 11xx = Reserved; do not use

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

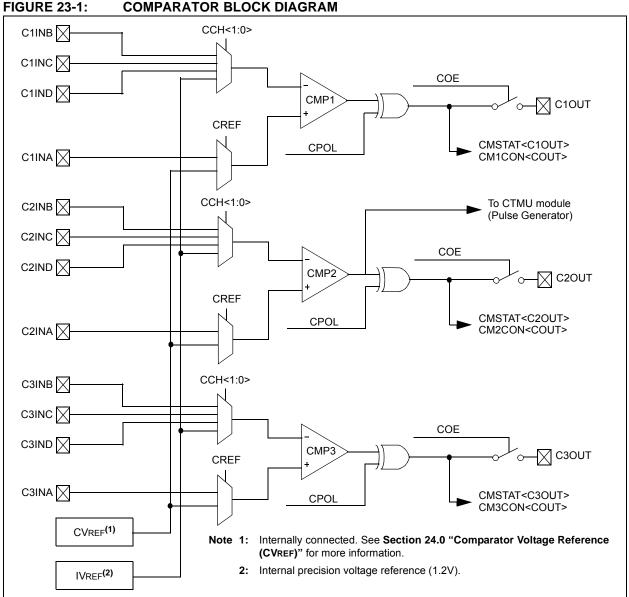

#### 23.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains three comparators that can be configured in a variety of ways.

Following are some of the key features of this module:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 23-1.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

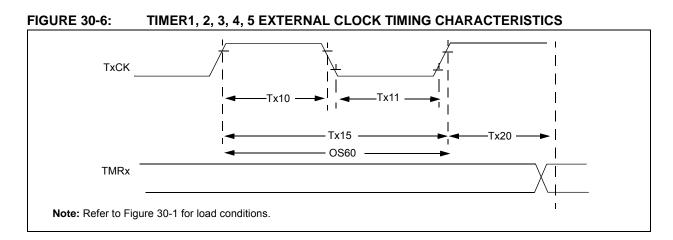

#### TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS <sup>(1)</sup> (unl |           |                                                              |                           | indard Operating Conditions: 2.3V to 3.6V<br>iless otherwise stated)<br>erating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                            |         |      |       |                               |

|----------------------------------------|-----------|--------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|------|-------|-------------------------------|

| Param.<br>No.                          | Symbol    | Characteristics <sup>(2)</sup>                               |                           |                                                                                                                                                                                                         | Min.                                       | Typical | Max. | Units | Conditions                    |

| TA10                                   | T⊤xH      | TxCK<br>High Time                                            | Synchronow with presca    |                                                                                                                                                                                                         | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —       | —    | ns    | Must also meet parameter TA15 |

|                                        |           |                                                              | Asynchrono<br>with presca |                                                                                                                                                                                                         | 10                                         | —       | _    | ns    | —                             |

| TA11                                   | T⊤xL      | TxCK<br>Low Time                                             | Synchronor<br>with presca |                                                                                                                                                                                                         | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns          | —       | —    | ns    | Must also meet parameter TA15 |

|                                        |           |                                                              | Asynchrono<br>with presca |                                                                                                                                                                                                         | 10                                         | _       | _    | ns    | —                             |

| TA15                                   | ΤτχΡ      | TxCK<br>Input Period                                         | Synchrono<br>with presca  |                                                                                                                                                                                                         | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns | -       | _    | ns    | VDD > 2.7V                    |

|                                        |           |                                                              |                           |                                                                                                                                                                                                         | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns | -       | —    | ns    | VDD < 2.7V                    |

|                                        |           |                                                              | Asynchrono<br>with presca |                                                                                                                                                                                                         | 20                                         | -       | —    | ns    | VDD > 2.7V<br>(Note 3)        |

|                                        |           |                                                              |                           |                                                                                                                                                                                                         | 50                                         | -       | _    | ns    | VDD < 2.7V<br>(Note 3)        |

| OS60                                   | FT1       | SOSC1/T1C<br>Input Freque<br>(oscillator en<br>the TCS (T10  | ncy Range<br>abled by set |                                                                                                                                                                                                         | 32                                         | —       | 100  | kHz   | -                             |

| TA20                                   | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                           | К                                                                                                                                                                                                       |                                            | —       | 1    | Трв   | —                             |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

#### TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHARACTERISTICS |                              |                               | Standard Op<br>(unless othe<br>Operating te | rwise st | <b>ated)</b><br>re -40° | ons: 2.3V to 3.6V<br>$^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                            |

|--------------------|------------------------------|-------------------------------|---------------------------------------------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Param.<br>No.      | Symbol                       | Charact                       | eristics                                    | Min.     | Max.                    | Units                                                                                                                      | Conditions                 |

| IS34               | THD:STO                      | Stop Condition                | 100 kHz mode                                | 4000     | _                       | ns                                                                                                                         | —                          |

|                    | Hold Time                    | Hold Time                     | 400 kHz mode                                | 600      | —                       | ns                                                                                                                         |                            |

|                    |                              |                               | 1 MHz mode<br>(Note 1)                      | 250      |                         | ns                                                                                                                         |                            |

| IS40               | S40 TAA:SCL Output Valid fro | Output Valid from             | 100 kHz mode                                | 0        | 3500                    | ns                                                                                                                         | —                          |

|                    |                              | Clock                         | 400 kHz mode                                | 0        | 1000                    | ns                                                                                                                         |                            |

|                    |                              | 1 MHz mode<br><b>(Note 1)</b> | 0                                           | 350      | ns                      |                                                                                                                            |                            |

| IS45               | TBF:SDA                      | Bus Free Time                 | 100 kHz mode                                | 4.7      | —                       | μs                                                                                                                         | The amount of time the bus |

|                    |                              |                               | 400 kHz mode                                | 1.3      | —                       | μs                                                                                                                         | must be free before a new  |

|                    |                              | 1 MHz mode<br>(Note 1)        | 0.5                                         | —        | μS                      | transmission can start                                                                                                     |                            |

| IS50               | Св                           | Bus Capacitive Lo             | ading                                       |          | 400                     | pF                                                                                                                         | —                          |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| AC CHARAG                         | S <sup>(2)</sup> | (unless of            | Operating<br>herwise state<br>temperature |                 |                            |

|-----------------------------------|------------------|-----------------------|-------------------------------------------|-----------------|----------------------------|

| ADC Speed                         | TAD Min.         | Sampling<br>Time Min. | Rs Max.                                   | Vdd             | ADC Channels Configuration |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns            | 132 ns                | 500Ω                                      | 3.0V to<br>3.6V | ANX CHX ADC                |

| Up to 400 ksps                    | 200 ns           | 200 ns                | 5.0 kΩ                                    | 2.5V to<br>3.6V | ANX CHX<br>ANX OF VREF-    |

#### TABLE 30-35:10-BIT CONVERSION RATE PARAMETERS

**Note 1:** External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

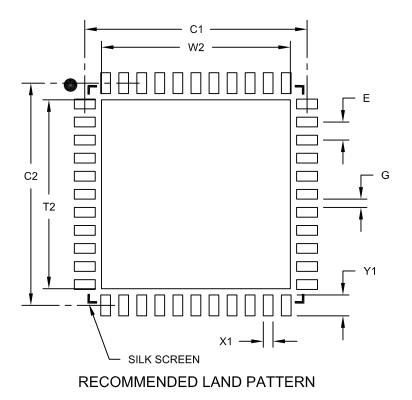

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |    | MILLIM | ETERS    |      |

|----------------------------|----|--------|----------|------|

| Dimension Limits           |    | MIN    | NOM      | MAX  |

| Contact Pitch              | E  |        | 0.65 BSC |      |

| Optional Center Pad Width  | W2 |        |          | 6.80 |

| Optional Center Pad Length | T2 |        |          | 6.80 |

| Contact Pad Spacing        | C1 |        | 8.00     |      |

| Contact Pad Spacing        | C2 |        | 8.00     |      |

| Contact Pad Width (X44)    | X1 |        |          | 0.35 |

| Contact Pad Length (X44)   | Y1 |        |          | 0.80 |

| Distance Between Pads      | G  | 0.25   |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

| TABLE A-1: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section                           | Update Description                                                                                                                                    |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29.0 "Electrical Characteristics" | Updated the Absolute Maximum Ratings (removed Voltage on VCORE with respect to Vss).                                                                  |

|                                   | Added the SPDIP specification to the Thermal Packaging Characteristics (see Table 29-2).                                                              |

|                                   | Updated the Typical values for parameters DC20-DC24 in the Operating Current (IDD) specification (see Table 29-5).                                    |

|                                   | Updated the Typical values for parameters DC30a-DC34a in the Idle Current (IIDLE) specification (see Table 29-6).                                     |

|                                   | Updated the Typical values for parameters DC40i and DC40n and removed parameter DC40m in the Power-down Current (IPD) specification (see Table 29-7). |

|                                   | Removed parameter D320 (VCORE) from the Internal Voltage Regulator Specifications and updated the Comments (see Table 29-13).                         |

|                                   | Updated the Minimum, Typical, and Maximum values for parameter F20b in the Internal FRC Accuracy specification (see Table 29-17).                     |

|                                   | Removed parameter SY01 (TPWRT) and removed all Conditions from Resets Timing (see Table 29-20).                                                       |

|                                   | Updated all parameters in the CTMU Specifications (see Table 29-39).                                                                                  |

| 31.0 "Packaging Information"      | Added the 28-lead SPDIP package diagram information (see <b>31.1</b> "Package Marking Information" and <b>31.2</b> "Package Details").                |

| "Product Identification System"   | Added the SPDIP (SP) package definition.                                                                                                              |

## Revision C (November 2011)

All major changes are referenced by their respective section in Table A-2.

| TABLE A-2: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                             | Update Description                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio<br>and Graphics Interfaces, USB, and<br>Advanced Analog" | Revised the source/sink on I/O pins (see "Input/Output" on page 1).<br>Added the SPDIP package to the PIC32MX220F032B device in the<br>PIC32MX2XX USB Family Features (see Table 2). |

| 4.0 "Memory Organization"                                                                                                           | Removed ANSB6 from the ANSELB register and added the ODCB6, ODCB10, and ODCB11 bits in the PORTB Register Map (see Table 4-20).                                                      |

| 29.0 "Electrical Characteristics"                                                                                                   | Updated the minimum value for parameter OS50 in the PLL Clock Timing Specifications (see Table 29-16).                                                                               |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| (64 KB RAM, 256 KB Flash)                         | 42  |

|---------------------------------------------------|-----|

| Memory Organization                               | 37  |

| Microchip Internet Web Site                       | 341 |

| MPLAB ASM30 Assembler, Linker, Librarian          | 254 |

| MPLAB Integrated Development Environment Software | 253 |

| MPLAB PM3 Device Programmer                       | 255 |

| MPLAB REAL ICE In-Circuit Emulator System         | 255 |

| MPLINK Object Linker/MPLIB Object Librarian       | 254 |

|                                                   |     |

# 0

| Oscillator Configuration | 73  |

|--------------------------|-----|

| Output Compare           | 161 |

# Ρ

| -                                  |  |

|------------------------------------|--|

| Packaging                          |  |

| Details                            |  |

| Marking                            |  |

| Parallel Master Port (PMP)         |  |

| PIC32 Family USB Interface Diagram |  |

| Pinout I/O Descriptions (table)    |  |

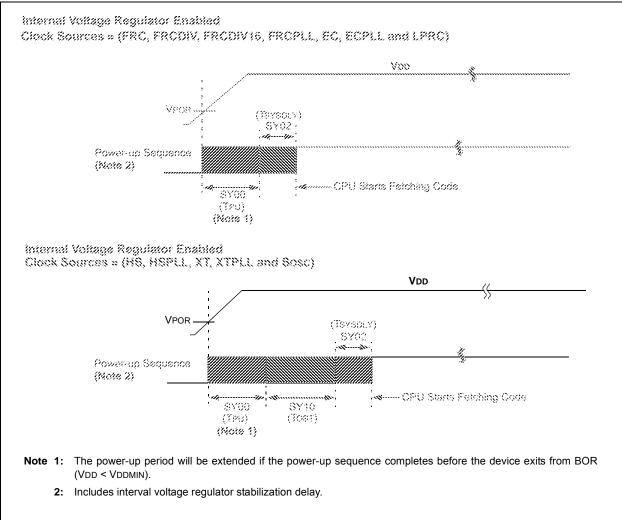

| Power-on Reset (POR)               |  |

| and On-Chip Voltage Regulator      |  |

| Power-Saving Features              |  |

| CPU Halted Methods                 |  |

| Operation                          |  |

| with CPU Running                   |  |

| -                                  |  |

#### R

| Real-Time Clock and Calendar (RTCC)            | .199 |

|------------------------------------------------|------|

| Register Maps                                  | 5–?? |

| Registers                                      |      |

| [pin name]R (Peripheral Pin Select Input)      |      |

| AD1CHS (ADC Input Select)                      | .217 |

| AD1CON1 (ADC Control 1)                        | 213  |

| AD1CON2 (ADC Control 2)                        | 215  |

| AD1CON3 (ADC Control 3)                        | 216  |

| AD1CSSL (ADC Input Scan Select)                | .218 |

| ALRMDATE (Alarm Date Value)                    | 208  |

| ALRMTIME (Alarm Time Value)                    | 207  |

| BMXBOOTSZ (Boot Flash (IFM) Size               | 51   |

| BMXCON (Bus Matrix Configuration)              | 46   |

| BMXDKPBA (Data RAM Kernel Program              |      |

| Base Address)                                  |      |

| BMXDRMSZ (Data RAM Size Register)              |      |

| BMXDUDBA (Data RAM User Data Base Address)     | 48   |

| BMXDUPBA (Data RAM User Program                |      |

| Base Address)                                  |      |

| BMXPFMSZ (Program Flash (PFM) Size)            | 51   |

| BMXPUPBA (Program Flash (PFM) User Program     |      |

| Base Address)                                  |      |

| CFGCON (Configuration Control)                 |      |

| CM1CON (Comparator 1 Control)                  |      |

| CMSTAT (Comparator Status Register)            |      |

| CNCONx (Change Notice Control for PORTx)       |      |

| CTMUCON (CTMU Control)                         |      |

| CVRCON (Comparator Voltage Reference Control). |      |

| DCHxCON (DMA Channel 'x' Control)              |      |

| DCHxCPTR (DMA Channel 'x' Cell Pointer)        |      |

| DCHxCSIZ (DMA Channel 'x' Cell-Size)           |      |

| DCHxDAT (DMA Channel 'x' Pattern Data)         |      |

| DCHxDPTR (Channel 'x' Destination Pointer)     | 99   |