#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256bt-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers provide 4 GB unified virtual memory address space. All memory regions, including program, data memory, Special Function Registers (SFRs), and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX 28/36/44-pin Family devices to execute from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/KSEG1) mode address space

- · Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

- Cacheable (KSEG0) and non-cacheable (KSEG1) address regions

## 4.1 PIC32MX1XX/2XX 28/36/44-pin Family Memory Layout

PIC32MX1XX/2XX 28/36/44-pin Family microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX 28/36/44-pin Family devices are illustrated in Figure 4-1 through Figure 4-6.

Table 4-1 provides SFR memory map details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     | NVMOP<3:0>             |                   |                  |                  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |

### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | —                 | —                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

|              | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

## REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

### bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | —                 |                   |                   |                   | _                 | _                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | _                 | —                 |                   |                   |                   | _                 | _                | —                |  |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |  |

|              | ENDPT<3:0>        |                   |                   |                   | DIR               | PPBI              |                  |                  |  |

## Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

## REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | CNT<7:0>          |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 10-16: U1SOF: USB SOF THRESHOLD REGISTER

## Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7-0 CNT<7:0>: SOF Threshold Value bits Typical values of the threshold are:

- 01001010 = 64-byte packet 00101010 = **32-byte packet**

- 00011010 = **16-byte packet**

- 00010010 = 8-byte packet

## REGISTER 10-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | -                 | -                 | -                 | -                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | -                 |                   |                   |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | -                 | -                 | -                 |                   |                   |                  | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          | BDTPTRL<15:9>     |                   |                   |                   |                   |                   |                  |                  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: Buffer Descriptor Table Base Address bits This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

| TABL                        | E 11-7:              | PEI       | RIPHER |       | SELEC |       | PUT RE | GISTER | MAP ( | CONTIN | IUED) |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|--------|-------|-------|-------|--------|--------|-------|--------|-------|------|------|------|------|------|--------|------|------------|

| SS                          |                      |           |        |       |       |       |        |        |       | В      | its   |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10  | 25/9  | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16     | _      | -     | —     | -     | _      | -      | _     | _      | -     | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0      | _      |       | —     |       | —      |        | _     | —      |       |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16     | —      | —     | —     | —     | —      | —      | _     | —      | —     | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0      | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | _    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16     | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | _    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0      | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16     | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        | KPD14K               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBIOR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0      | —      | —     | —     | —     | —      | —      | -     |        | —     | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16     | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 31:16     |        | —     | —     | —     | —      | —      | _     |        | —     | _    | —    | —    | _    | _    | —      | _    | 0000       |

| FB80                        | KPUSK"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 31:16     |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 31:16     |        | —     |       | —     | —      | —      | _     |        | —     |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | RPU/R <sup>(1)</sup> | 15:0      | _      | _     | —     | _     | _      | —      | —     | _      | —     |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

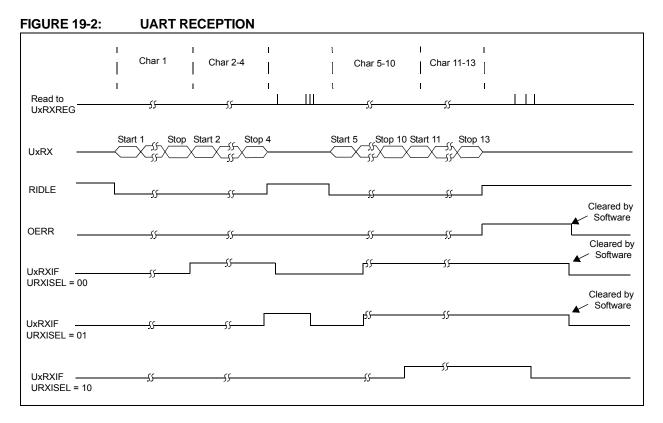

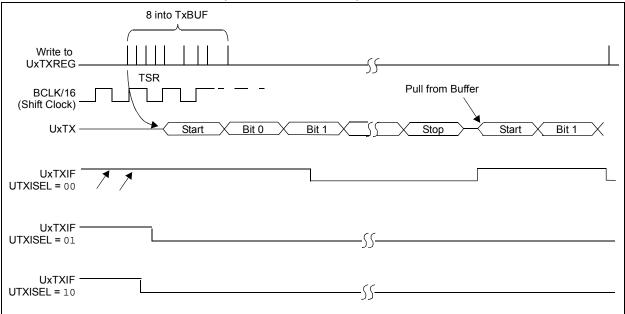

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

## REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

#### bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

|              | —                     |                   |                   | -                 | _                 |                   | _                | —                |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 23:16        | —                     |                   | —                 | -                 | —                 | FI                | PLLODIV<2:(      | )>               |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | _                 | —                 | UF                | PLLIDIV<2:0>     | .(1)             |

| 7:0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |

|              | —                     | F                 | PLLMUL<2:0>       |                   | _                 | F                 | PLLIDIV<2:0      | >                |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 27-3:**

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1'

- bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

- 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier

- 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|----------------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

| 04.04        | R                          | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 31:24        |                            | VER<              | 3:0> <sup>(1)</sup> |                   |                   | DEVID<            | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                          | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16>(1)            |                   |                     |                   |                   |                   |                       |                  |  |

| 45.0         | R                          | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup> |                   |                     |                   |                   |                   |                       |                  |  |

| 7.0          | R                          | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 7:0          |                            |                   |                     | DEVID             | <7:0>(1)          |                   |                       |                  |  |

## REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

| AC CHA        | AC CHARACTERISTICS |                                                                      |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |

|---------------|--------------------|----------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|

| Param.<br>No. | Symbol             | Characteristics <sup>(1)</sup>                                       | Min. | Тур.                                                                                                                                                                                                                                                                                | Max. | Units | Conditions |  |  |

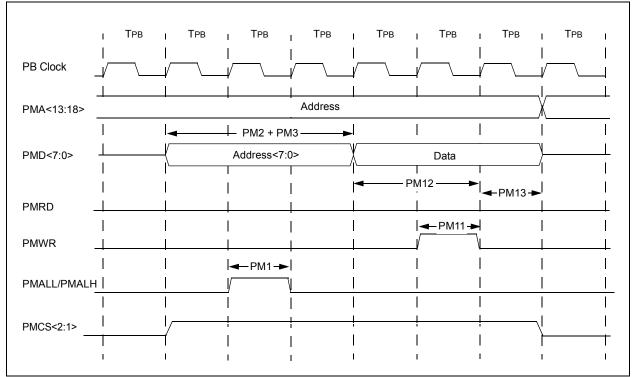

| PM1           | Tlat               | PMALL/PMALH Pulse Width                                              |      | 1 Трв                                                                                                                                                                                                                                                                               | _    | _     | _          |  |  |

| PM2           | TADSU              | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _    | 2 Трв                                                                                                                                                                                                                                                                               | _    | _     | _          |  |  |

| PM3           | Tadhold            | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —    | 1 Трв                                                                                                                                                                                                                                                                               | _    | —     | _          |  |  |

| PM4           | TAHOLD             | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5    | _                                                                                                                                                                                                                                                                                   | _    | ns    | _          |  |  |

| PM5           | Trd                | PMRD Pulse Width                                                     | _    | 1 Трв                                                                                                                                                                                                                                                                               | _    | _     | —          |  |  |

| PM6           | TDSU               | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15   | —                                                                                                                                                                                                                                                                                   | —    | ns    | _          |  |  |

| PM7           | TDHOLD             | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | —    | 80                                                                                                                                                                                                                                                                                  | —    | ns    |            |  |  |

### TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

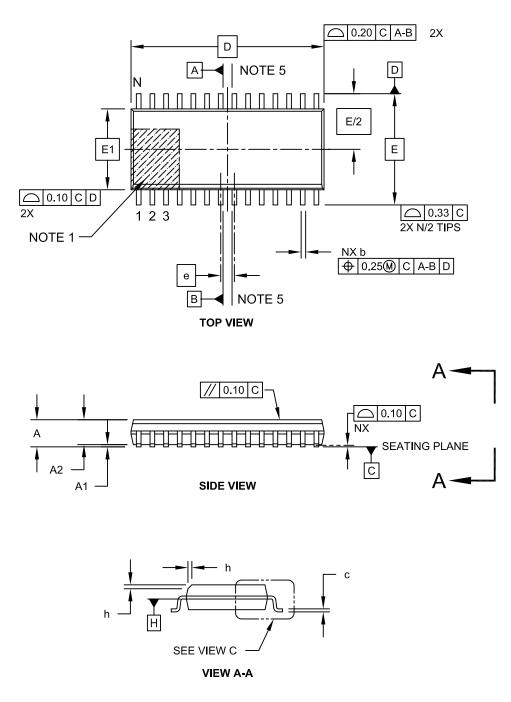

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

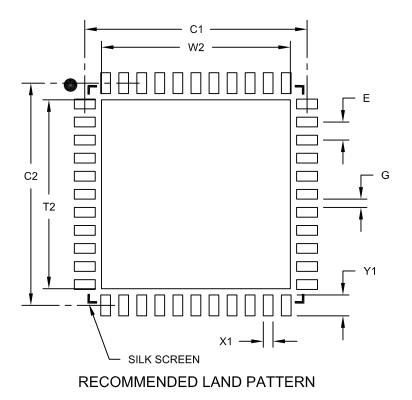

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimensior                  | MIN         | NOM  | MAX      |      |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 6.80 |

| Optional Center Pad Length | T2          |      |          | 6.80 |

| Contact Pad Spacing        | C1          |      | 8.00     |      |

| Contact Pad Spacing        | C2          |      | 8.00     |      |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |

| Contact Pad Length (X44)   | Y1          |      |          | 0.80 |

| Distance Between Pads      | G           | 0.25 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

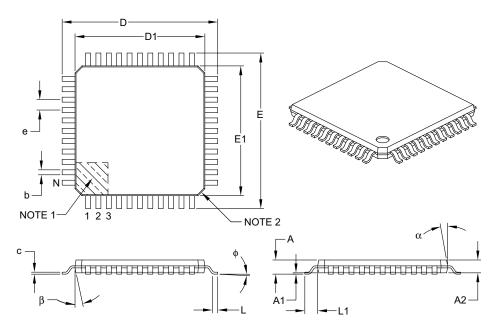

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        |      | MILLIMETERS |      |

|--------------------------|--------------|------|-------------|------|

| Dime                     | nsion Limits | MIN  | NOM         | MAX  |

| Number of Leads          | N            |      | 44          |      |

| Lead Pitch               | е            |      | 0.80 BSC    |      |

| Overall Height           | А            | _    | -           | 1.20 |

| Molded Package Thickness | A2           | 0.95 | 1.00        | 1.05 |

| Standoff                 | A1           | 0.05 | -           | 0.15 |

| Foot Length              | L            | 0.45 | 0.60        | 0.75 |

| Footprint                | L1           |      | 1.00 REF    |      |

| Foot Angle               | φ            | 0°   | 3.5°        | 7°   |

| Overall Width            | E            |      | 12.00 BSC   |      |

| Overall Length           | D            |      | 12.00 BSC   |      |

| Molded Package Width     | E1           |      | 10.00 BSC   |      |

| Molded Package Length    | D1           |      | 10.00 BSC   |      |

| Lead Thickness           | С            | 0.09 | -           | 0.20 |

| Lead Width               | b            | 0.30 | 0.37        | 0.45 |

| Mold Draft Angle Top     | α            | 11°  | 12°         | 13°  |

| Mold Draft Angle Bottom  | β            | 11°  | 12°         | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

## **Revision E (October 2012)**

All singular pin diagram occurrences of CVREF were changed to: CVREFOUT. In addition, minor text and formatting changes were incorporated throughout the document.

All major changes are referenced by their respective section in Table A-4.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                                | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>128 KB Flash and 32 KB SRAM)<br>with Audio and Graphics<br>Interfaces, USB, and Advanced<br>Analog" | <ul> <li>Updated the following feature sections:</li> <li>"Operating Conditions"</li> <li>"Communication Interfaces"</li> </ul>                                                                                                                                                                                                                                                                                                             |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | Removed Section 2.8 "Configuration of Analog and Digital Pins During ICSP Operations".                                                                                                                                                                                                                                                                                                                                                      |

| 3.0 "CPU"                                                                                                                              | Removed references to GPR shadow registers in <b>3.1 "Features"</b> and <b>3.2.1 "Execution Unit"</b> .                                                                                                                                                                                                                                                                                                                                     |

| 4.0 "Memory Organization"                                                                                                              | Updated the BRG bit range in the SPI1 and SPI2 Register Map (see Table 4-8).<br>Added the PWP<6> bit to the Device Configuration Word Summary<br>(see Table 4-17).                                                                                                                                                                                                                                                                          |

| 5.0 "Flash Program Memory"                                                                                                             | Added a note with Flash page size and row size information.                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.0 "Interrupt Controller"                                                                                                             | Updated the TPC<2:0> bit definitions (see Register 7-1).<br>Updated the IPTMR<31:0> bit definition (see Register 7-3).                                                                                                                                                                                                                                                                                                                      |

| 8.0 "Oscillator Configuration"                                                                                                         | Updated the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).<br>Updated the RODIV<14:0> bit definitions (see Register 8-3).                                                                                                                                                                                                                                                                                                            |

| 10.0 "USB On-The-Go (OTG)"                                                                                                             | Updated the Notes in the USB Interface Diagram (see Figure 10-1).                                                                                                                                                                                                                                                                                                                                                                           |

| 18.0 "Universal Asynchronous<br>Receiver Transmitter (UART)"                                                                           | Updated the baud rate range in the list of primary features.                                                                                                                                                                                                                                                                                                                                                                                |

| 26.0 "Special Features"                                                                                                                | Added the PWP<6> bit to the Device Configuration Word 0 (see Register 26-1).                                                                                                                                                                                                                                                                                                                                                                |

| 29.0 "Electrical Characteristics"                                                                                                      | <ul> <li>Added Note 1 to Operating MIPS vs. Voltage (see Table 29-1).</li> <li>Added Note 2 to DC Temperature and Voltage Specifications (see Table 29-4).</li> <li>Updated the Conditions for parameter DC25 in DC Characteristics: Operating Current (IDD) (see Table 29-5).</li> <li>Added Note 2 to Electrical Characteristics: BOR (see Table 29-10).</li> <li>Added Note 4 to Comparator Specifications (see Table 29-12).</li> </ul> |

|                                                                                                                                        | <ul> <li>Added Note 5 to ADC Module Specifications (see Table 29-32).</li> <li>Updated the 10-bit Conversion Rate Parameters and added Note 3 (see Table 29-33).</li> <li>Added Note 4 to the Analog-to-Digital Conversion Timing Requirements (see Table 29-34).</li> <li>Added Note 3 to CTMU Current Source Specifications (see Table 29-39).</li> </ul>                                                                                 |

| 30.0 "50 MHz Electrical<br>Characteristics"                                                                                            | New chapter with electrical characteristics for 50 MHz devices.                                                                                                                                                                                                                                                                                                                                                                             |

| 31.0 "Packaging Information"                                                                                                           | The 36-pin and 44-pin VTLA packages have been updated.                                                                                                                                                                                                                                                                                                                                                                                      |

## **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

## TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |

|                                                                                                                                   | Added Program Flash Size value for 256 KB Flash devices (see Register 4-5).                                                                          |

| 12.0 "Timer1"                                                                                                                     | The Timer1 block diagram was updated to include the 16-bit data bus (see Figure 12-1).                                                               |

| 13.0 "Timer2/3, Timer4/5"                                                                                                         | The Timer2-Timer5 block diagram (16-bit) was updated to include the 16-bit data bus (see Figure 13-1).                                               |

|                                                                                                                                   | The Timer2/3, Timer4/5 block diagram (32-bit) was updated to include the 32-<br>bit data bus (see Figure 13-1).                                      |

| 19.0 "Parallel Master Port (PMP)"                                                                                                 | The CSF<1:0> bit value definitions for '00' and '01' were updated (see Register 19-1).                                                               |

|                                                                                                                                   | Bit 14 in the Parallel Port Address register (PMADDR) was updated (see Register 19-3).                                                               |

| 20.0 "Real-Time Clock and                                                                                                         | The following registers were updated:                                                                                                                |

| Calendar (RTCC)"                                                                                                                  | RTCTIME (see Register 20-3)                                                                                                                          |

|                                                                                                                                   | RTCDATE (see Register 20-4)                                                                                                                          |

|                                                                                                                                   | ALRMTIME (see Register 20-5)                                                                                                                         |

|                                                                                                                                   | ALRMDATE (see Register 20-6)                                                                                                                         |

| 26.0 "Special Features"                                                                                                           | Updated the PWP bits (see Register 26-1).                                                                                                            |

| 29.0 "Electrical Characteristics"                                                                                                 | Added parameters DO50 and DO50a to the Capacitive Loading Requirements on Output Pins (see Table 29-14).                                             |

|                                                                                                                                   | Added Note 5 to the IDD DC Characteristics (see Table 29-5).                                                                                         |

|                                                                                                                                   | Added Note 4 to the IIDLE DC Characteristics (see Table 29-6).                                                                                       |

|                                                                                                                                   | Added Note 5 to the IPD DC Characteristics (see Table 29-7).                                                                                         |

|                                                                                                                                   | Updated the conditions for parameters USB321 (VOL) and USB322 (VOH) in the OTG Electrical Specifications (see Table 29-38).                          |

| Product Identification System                                                                                                     | Added 40 MHz speed information.                                                                                                                      |

NOTES: