Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256d-50i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

# 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

| Pin # | Full Pin Name                        | Pi | in # | Full Pin Name                                  |

|-------|--------------------------------------|----|------|------------------------------------------------|

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 | 1  | 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   | 2  | 20   | RPC9/CTED7/RC9                                 |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   | 2  | 21   | Vss                                            |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   | 2  | 22   | VCAP                                           |

| 5     | Vdd                                  | 2  | 23   | Vdd                                            |

| 6     | Vss                                  | 2  | 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 7     | OSC1/CLKI/RPA2/RA2                   | 2  | 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              | 2  | 26   | AN12/PMD0/RB12                                 |

| 9     | SOSCI/RPB4/RB4                       | 2  | 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       | 2  | 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 11    | RPC3/RC3                             | 2  | 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 12    | Vss                                  | 3  | 30   | AVss                                           |

| 13    | Vdd                                  | 3  | 31   | AVdd                                           |

| 14    | Vdd                                  | 3  | 32   | MCLR                                           |

| 15    | PGED3/RPB5/PMD7/RB5                  | 3  | 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 16    | PGEC3/RPB6/PMD6/RB6                  | 3  | 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         | 3  | 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        | 3  | 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

### TABLE 13: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

# 44-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | Vref-/CVref-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

44

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

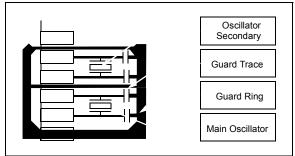

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

NOTES:

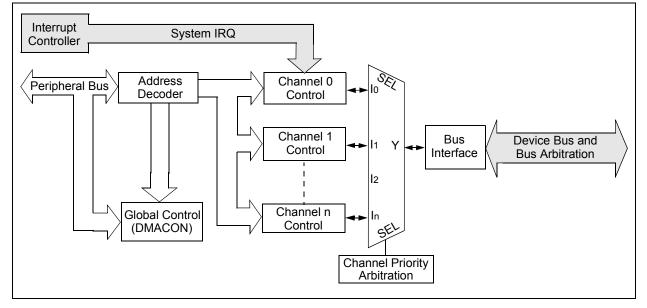

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

### FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | _                | _                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |

### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

1111111111111111 = 65,535 bytes transferred on an event

### REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

|              |                   |                   | •••••••••••       |                   |                   |                   | -                |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 1.0          | 7:0 CHCPTR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

#### **USB Control Registers** 10.1

### TABLE 10-1: USB REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit                    | s        |          |                  |          |          |                 |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------------------------|----------|----------|------------------|----------|----------|-----------------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6     | 21/5     | 20/4             | 19/3     | 18/2     | 17/1            | 16/0     | All Resets |

| 5040                        | (4)                             | 31:16     | _     | —     | —     | —     | —     | —     |      | _    | —                      | —        | —        | —                | —        | —        | _               | —        | 000        |

| 5040                        | UTUTUIK /                       | 15:0      |       | _     | _     | —     | _     | _     |      | _    | IDIF                   | T1MSECIF | LSTATEIF | ACTVIF           | SESVDIF  | SESENDIF | 1               | VBUSVDIF | 000        |

| 5050                        | <b>U10TGIE</b>                  | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —                      |          | —        | —                | —        | —        | _               | —        | 000        |

| 0000                        | OTOTOLE                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | IDIE                   | T1MSECIE | LSTATEIE | ACTVIE           | SESVDIE  | SESENDIE | _               | VBUSVDIE | 000        |

| 5060                        | U10TGSTAT <sup>(3)</sup>        | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | 0101001/11                      | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | ID                     |          | LSTATE   | —                | SESVD    | SESEND   | _               | VBUSVD   | 000        |

| 5070                        | U10TGCON                        | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0070                        | UTOTOOON                        | 15:0      | _     | —     | —     | —     | —     | —     | _    | —    | DPPULUP                | DMPULUP  | DPPULDWN | DMPULDWN         | VBUSON   | OTGEN    | VBUSCHG         | VBUSDIS  | 000        |

| 5080                        | U1PWRC                          | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 0000                        | on wite                         | 15:0      | _     | —     | —     | —     | —     | —     | _    | —    | UACTPND <sup>(4)</sup> |          | —        | USLPGRD          | USBBUSY  | —        | USUSPEND        | USBPWR   | 000        |

|                             |                                 | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |                        |          | —        | —                |          | —        | _               |          | 000        |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF | RESUMEIF | IDLEIF           | TRNIF    | SOFIF    | UERRIF          | URSTIF   | 000        |

|                             |                                 | 04.40     |       |       |       |       |       |       |      |      |                        |          |          |                  |          |          |                 | DETACHIF | 000        |

| 5210                        | U1IE                            | 31:16     | _     | _     |       |       |       |       |      | _    | —                      | —        |          | —                | —        | —        | —               |          | 000        |

| 5210                        | OTIE                            | 15:0      | —     | —     |       | —     | —     | —     | —    | —    | STALLIE                | ATTACHIE | RESUMEIE | IDLEIE           | TRNIE    | SOFIE    | UERRIE          | DETACHIE | 000        |

|                             |                                 | 31:16     | _     | _     | _     | _     |       | _     |      |      | _                      | _        | _        | _                | _        | _        | _               |          | 000        |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                  | BMXEF    | DMAEF    | BTOEF            | DFN8EF   | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 000        |

|                             |                                 | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _                      |          | _        | _                | _        |          | _               |          | 000        |

| 5230                        | U1EIE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEE                  | BMXEE    | DMAEE    | BTOEE            | DFN8EE   | CRC16EE  | CRC5EE<br>EOFEE | PIDEE    | 000        |

|                             | (2)                             | 31:16     | _     | _     |       | _     | _     |       |      | _    |                        | _        |          | _                | _        |          | _               | _        | 000        |

| 5240                        | U1STAT <sup>(3)</sup>           | 15:0      | _     | _     | _     | _     | _     | _     |      | _    |                        |          | PT<3:0>  |                  | DIR      | PPBI     | _               | _        | 000        |

|                             |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    | _                      | _        |          |                  | _        | _        | _               | _        | 000        |

| 5250                        | U1CON                           |           |       |       |       |       |       |       |      |      |                        |          | PKTDIS   |                  |          |          |                 | USBEN    | 000        |

|                             |                                 | 15:0      |       | —     | —     | —     | —     | —     |      | —    | JSTATE                 | SE0      | TOKBUSY  | USBRST           | HOSTEN   | RESUME   | PPBRST          | SOFEN    | 000        |

| 5260                        | U1ADDR                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | —        | 000        |

| 5260                        | UTADDR                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | LSPDEN                 |          |          | DE               | VADDR<6: | 0>       |                 |          | 000        |

| 5070                        |                                 | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | _                      | _        | _        | _                | _        | _        | _               | _        | 000        |

| 5270                        | U1BDTP1                         | 15:0      | —     |       |       | _     |       |       |      | _    |                        |          | BC       | )<br>TPTRL<15:9> | >        |          |                 |          | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

2: This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | —         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | _     | _     | _     | —     | _     | —    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |       |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —     |       | _     |       |       | _    | _    | _     | —        | _     | —        | —      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | OIBDIF3                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTRI  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        | UTCNI UT                        | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | _     | —     | _     | —    | _    | —     | —        | _     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —     |       | —     | —     |       | —    | _    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     |       | —     | —     | —     | —    |      |       | —        | _     |          | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —     |       | —     | —     |       | —    | _    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | _     | _     | _     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | -     | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| INE OIOT     | LK 10-J.          |                   |                   |                   |                        |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   | —                 | _                      | _                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

### Legend:

| zogonai           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

# **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 51.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23.10        | -                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         | _                 | —                 | _                 | _                 | —                 | _                 | _                     | —                                                |

|              | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       |                                               |

- 1 = STALL interrupt is enabled

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 = ATTACH interrupt is enabled 0 = ATTACH interrupt is disabled

- bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

### DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

### TABLE 11-4: PORTB REGISTER MAP

| ess                                                                                                                                                                                                                                                            |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Addr<br>(BF88_#)                                                                                                                                                                                                                                       | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

|                                                                                                                                                                                                                                                                |                  | 31:16     | _             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            |              | —            | —            | —            | —            | 0000       |

| Section       Section         6100       ANSELE         61100       ANSELE         61100       TRISB         61200       PORTE         61301       LATB         61400       ODCB         61500       CNPUE         61600       CNPUE         61700       CNCON | ANGLED           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | —             | —             | —            | —            | _            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                                                                                                                                                                                                                                                           | TRISB            | 31:16     | -             | _             | _             | 1                            | _             | —             | —            | _            | -            | -                           | -            | -            | _            | _            | _            | _            | 0000       |

| 0110                                                                                                                                                                                                                                                           | TRIOD            | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                                                                                                                                                                                                                                                           |                  | 31:16     | _             | _             | _             |                              | _             | _             | _            | _            |              | _                           | -            |              |              |              |              |              | 0000       |

| 0120                                                                                                                                                                                                                                                           | FORTB            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                                                                                                                                                                                                                                                           |                  | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            | _            | _            | _            | 0000       |

| 0150                                                                                                                                                                                                                                                           | LAID             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| C1 4 0                                                                                                                                                                                                                                                         | 0000             | 31:16     |               | _             | —             | —                            | _             | _             | _            | —            | _            | —                           |              | —            | _            | _            | _            | —            | 0000       |

| 6140                                                                                                                                                                                                                                                           | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                                                                                                                                                                                                                                                           |                  | 31:16     | -             | —             | —             | -                            | _             | _             | _            | —            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0150                                                                                                                                                                                                                                                           | CNPUB            | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6(2)                   | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                                                                                                                                                                                                                                                           |                  | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            | _            | _            | _            | 0000       |

| 0100                                                                                                                                                                                                                                                           | CNPDB            | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                                                                                                                                                                                                                                                           |                  | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            | _            | _            | _            | 0000       |

| 0170                                                                                                                                                                                                                                                           | CINCOINE         | 15:0      | ON            | _             | SIDL          |                              | -             | _             | _            | _            |              | _                           |              |              | _            | _            | _            | _            | 0000       |

| C400                                                                                                                                                                                                                                                           |                  | 31:16     |               | —             | —             | -                            | —             | —             | —            | —            |              | _                           | Ι            | -            | —            | —            | —            | —            | 0000       |

| 6180                                                                                                                                                                                                                                                           | CNENB            | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6 <sup>(2)</sup>       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                                                                                                                                                                                                                                                                |                  | 31:16     | —             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            | _            | _            | _            | _            |              | 0000       |

| 6190                                                                                                                                                                                                                                                           | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

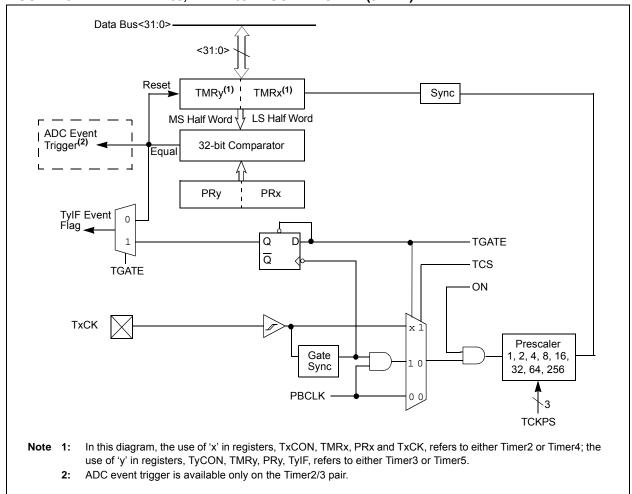

### FIGURE 13-2: TIMER2/3, TIMER4/5 BLOCK DIAGRAM (32-BIT)

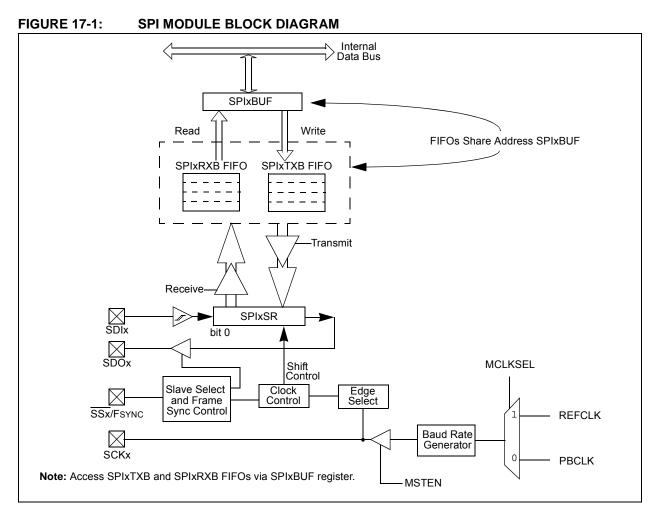

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- Master mode and Slave mode support

- Four clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | _                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

### Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### 23.1 Comparator Control Registers

### TABLE 23-1: COMPARATOR REGISTER MAP

| Bits                        |                                 |           |       |       |       |       |       |       |      |      |      |        |      |      |      |       |       |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Reset |

| 4000                        | CM1CON                          | 31:16     | _     | —     | _     | _     | -     | _     |      | -    | —    | _      | -    | —    | —    | —     | _     | _     | 0000      |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A010                        | CM2CON                          | 31:16     | —     | -     |       |       | -     |       | -    | -    | —    | —      | -    | _    | —    | —     |       | —     | 0000      |

| AUTO                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | _     |       | _     |      | COUT | EVPO | L<1:0> |      | CREF | _    | _     | CCH   | <1:0> | 00C3      |

| A020                        | CM3CON                          | 31:16     | _     | _     | _     | _     |       | _     |      |      | _    | _      |      | _    | _    | _     | _     | _     | 0000      |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A060                        | CMSTAT                          | 31:16     | —     | _     | _     | _     | -     | _     | _    | -    | —    | _      | -    | _    | _    | —     | _     | —     | 0000      |

| 7000                        | CIVISTAI                        | 15:0      | _     | _     | SIDL  | _     |       | _     |      |      | -    | _      |      | _    |      | C3OUT | C2OUT | C10UT | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | —                 | —                 | CCH              | <1:0>            |

### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

### REGISTER 27-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

- Note 1: This bit is only available on PIC32MX2XX devices.

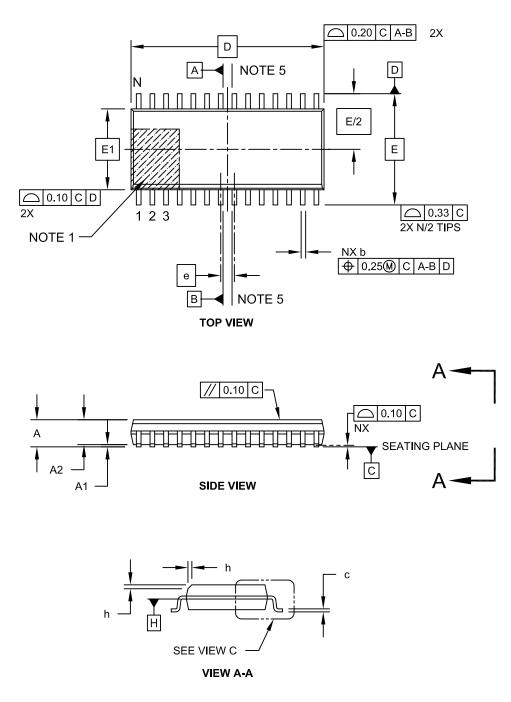

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

# **Revision E (October 2012)**

All singular pin diagram occurrences of CVREF were changed to: CVREFOUT. In addition, minor text and formatting changes were incorporated throughout the document.

All major changes are referenced by their respective section in Table A-4.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                                | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>128 KB Flash and 32 KB SRAM)<br>with Audio and Graphics<br>Interfaces, USB, and Advanced<br>Analog" | <ul> <li>Updated the following feature sections:</li> <li>"Operating Conditions"</li> <li>"Communication Interfaces"</li> </ul>                                                                                                                                                                                                                                                                                                             |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | Removed Section 2.8 "Configuration of Analog and Digital Pins During ICSP Operations".                                                                                                                                                                                                                                                                                                                                                      |

| 3.0 "CPU"                                                                                                                              | Removed references to GPR shadow registers in <b>3.1 "Features"</b> and <b>3.2.1 "Execution Unit"</b> .                                                                                                                                                                                                                                                                                                                                     |

| 4.0 "Memory Organization"                                                                                                              | Updated the BRG bit range in the SPI1 and SPI2 Register Map (see Table 4-8).<br>Added the PWP<6> bit to the Device Configuration Word Summary<br>(see Table 4-17).                                                                                                                                                                                                                                                                          |

| 5.0 "Flash Program Memory"                                                                                                             | Added a note with Flash page size and row size information.                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.0 "Interrupt Controller"                                                                                                             | Updated the TPC<2:0> bit definitions (see Register 7-1).<br>Updated the IPTMR<31:0> bit definition (see Register 7-3).                                                                                                                                                                                                                                                                                                                      |