Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 33                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256d-50i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14 |       | Bit<br>29/21/13/5 |       |          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|--------------------------------|-------|-------------------|-------|----------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0                            | U-0   | U-0               | U-0   | U-0      | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | -                              | _     | _                 | _     | _        |                   | _                | _                |  |  |  |  |  |

| 00.40        | U-0                            | U-0   | U-0               | U-0   | U-0      | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | _                              | —     | —                 | _     | _        | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R/W-0                          | R/W-0 | R/W-0             | R/W-0 | R/W-0    | R/W-0             | R-0              | R-0              |  |  |  |  |  |

| 15:8         | BMXDKPBA<15:8>                 |       |                   |       |          |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0                            | R-0   | R-0               | R-0   | R-0      | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                                |       |                   | BMXDK | PBA<7:0> |                   |                  |                  |  |  |  |  |  |

### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

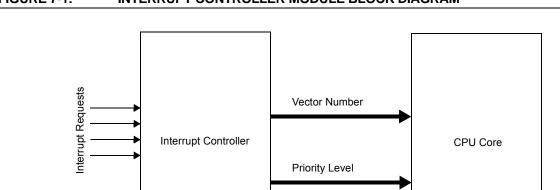

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

### FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

NOTES:

## 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- Low-Speed Host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

### REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         |                   | —                 | —                 | —                 | _                 | —                 |                  | —                |  |  |  |  |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |  |  |  |

| 7.0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |  |  |  |  |

### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | —                 |                   |                   |                   | _                 | _                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | _                 | —                 |                   |                   |                   | _                 | _                | —                |  |  |  |

| 7.0          | R-x               | R-x               | R-x R-x           |                   | R-x               | R-x               | U-0              | U-0              |  |  |  |

| 7:0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  |                  |  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                 | —                 | —                 |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

### bit 3-1 Unimplemented: Read as '0'

### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         |                   | _                 |                   | _                 | —                 |                   | -                | -                |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | LSPD              | RETRYDIS          |                   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |  |  |

### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

### Legend:

| 20901141          |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a Low-Speed device enabled

- 0 = Direct connection to a Low-Speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

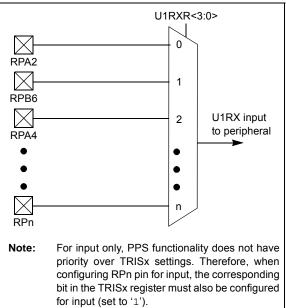

## 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

## TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —     | —     | —    | 0000       |

| FB8C                        | RPCort               | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8  | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —     | —     |      | 0000       |

| FB90 RPC9R <sup>(3)</sup>   | 15:0                 | —         | —     | —     | —     | —     | —     | —     | —    | _    | —    | —    | —    |      | RPC  | <3:0> |       | 0000 |            |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                    | _                 | -                 | —                | —                |

| 00.10        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                    | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                    | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

### REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

### bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in hardware only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

## **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | —                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        | —                 | —                 | —                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        | —                 | —                 | —                 |                   | Tک                | KBUFELM<4:0       | >                |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |

| 15:8         | —                 | —                 | —                 | FRMERR            | SPIBUSY           | —                 | _                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            |                   | SPITBF           | SPIRBF           |  |

### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit HS = Set in hardware |                                    |                    |

|-------------------|----------------------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit                       | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set                       | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 Трв

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 Трв

- 10 = Wait of 2 TPB

- 01 = Wait of 1 ТРВ

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              |                   |                   | SMP               | I<3:0>            |                   | BUFM             | ALTS             |

### REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVdd               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVdd               | AVss               |

### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

### bit 6 Unimplemented: Read as '0'

### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

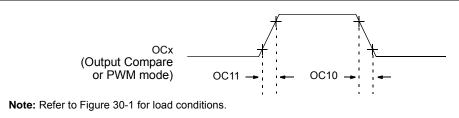

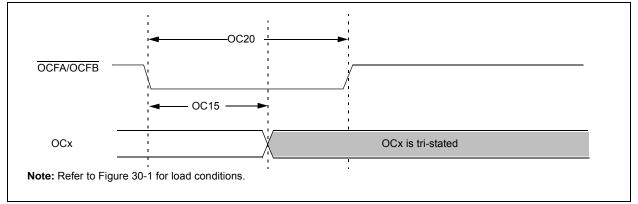

### FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

|               |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                                   |  |  |                    |  |  |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--------------------|--|--|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                        | Min. Typical <sup>(2)</sup> Max. Units Conditions |  |  |                    |  |  |

| OC10          | TccF   | OCx Output Fall Time                                                                                                                                                                                                                                                                  | — — ns See paramete                               |  |  | See parameter DO32 |  |  |

| OC11          | TccR   | OCx Output Rise Time                                                                                                                                                                                                                                                                  | — — — ns See parameter DO31                       |  |  |                    |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

### TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |                        |     |       |            |

|--------------------|--------|-------------------------------------------------------|-----|------------------------|-----|-------|------------|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup>                        | Min | Typical <sup>(2)</sup> | Max | Units | Conditions |

| OC15               | TFD    | Fault Input to PWM I/O Change                         | —   | —                      | 50  | ns    | _          |

| OC20               | TFLT   | Fault Input Pulse Width                               | 50  | —                      |     | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N         | MILLIMETERS |           |      |  |

|--------------------------|-----------|-------------|-----------|------|--|

| Dimension                | Limits    | MIN         | NOM       | MAX  |  |

| Number of Pins           | N         |             | 28        |      |  |

| Pitch                    | е         |             | 1.27 BSC  |      |  |

| Overall Height           | A         | -           | -         | 2.65 |  |

| Molded Package Thickness | A2        | 2.05        | -         | -    |  |

| Standoff §               | A1        | 0.10        | -         | 0.30 |  |

| Overall Width            | E         |             | 10.30 BSC |      |  |

| Molded Package Width     | E1        | 7.50 BSC    |           |      |  |

| Overall Length           | D         |             | 17.90 BSC |      |  |

| Chamfer (Optional)       | h         | 0.25        | -         | 0.75 |  |

| Foot Length              | L         | 0.40        | -         | 1.27 |  |

| Footprint                | L1        |             | 1.40 REF  |      |  |

| Lead Angle               | Θ         | 0°          | -         | -    |  |

| Foot Angle               | $\varphi$ | 0°          | -         | 8°   |  |

| Lead Thickness           | С         | 0.18        | -         | 0.33 |  |

| Lead Width               | b         | 0.31 - 0.51 |           |      |  |

| Mold Draft Angle Top     | α         | 5° - 15°    |           |      |  |

| Mold Draft Angle Bottom  | β         | 5°          | -         | 15°  |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

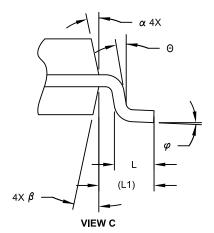

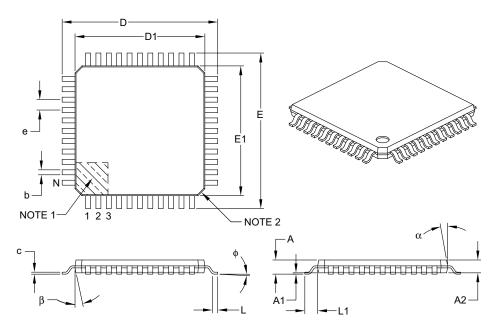

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        | MILLIMETERS |      |      |

|--------------------------|--------------|-------------|------|------|

| Dime                     | nsion Limits | MIN         | NOM  | MAX  |

| Number of Leads          | N            | 44          |      |      |

| Lead Pitch               | е            | 0.80 BSC    |      |      |

| Overall Height           | А            | _           | -    | 1.20 |

| Molded Package Thickness | A2           | 0.95        | 1.00 | 1.05 |

| Standoff                 | A1           | 0.05        | -    | 0.15 |

| Foot Length              | L            | 0.45        | 0.60 | 0.75 |

| Footprint                | L1           | 1.00 REF    |      |      |

| Foot Angle               | φ            | 0°          | 3.5° | 7°   |

| Overall Width            | E            | 12.00 BSC   |      |      |

| Overall Length           | D            | 12.00 BSC   |      |      |

| Molded Package Width     | E1           | 10.00 BSC   |      |      |

| Molded Package Length    | D1           | 10.00 BSC   |      |      |

| Lead Thickness           | С            | 0.09        | -    | 0.20 |

| Lead Width               | b            | 0.30        | 0.37 | 0.45 |

| Mold Draft Angle Top     | α            | 11°         | 12°  | 13°  |

| Mold Draft Angle Bottom  | β            | 11°         | 12°  | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

## INDEX

| 50 MHz Electrical Characteristics         | 301 |

|-------------------------------------------|-----|

| Α                                         |     |

| AC Characteristics                        | 269 |

| 10-Bit Conversion Rate Parameters         | 291 |

| ADC Specifications                        | 289 |

| Analog-to-Digital Conversion Requirements | 292 |

| EJTAG Timing Requirements                 | 300 |

| Internal FRC Accuracy                     |     |

| Internal RC Accuracy                      | 271 |

| OTG Electrical Specifications             | 298 |

| Parallel Master Port Read Requirements    | 297 |

| Parallel Master Port Write                | 298 |

| Parallel Master Port Write Requirements   | 298 |

| Parallel Slave Port Requirements          | 296 |

| PLL Clock Timing                          | 271 |

| Analog-to-Digital Converter (ADC)         | 209 |

| Assembler                                 |     |

| MPASM Assembler                           | 254 |

## В

| Block Diagrams                                     |  |

|----------------------------------------------------|--|

| ADC Module                                         |  |

| Comparator I/O Operating Modes                     |  |

| Comparator Voltage Reference                       |  |

| Connections for On-Chip Voltage Regulator          |  |

| Core and Peripheral Modules 19                     |  |

| CPU                                                |  |

| CTMU Configurations                                |  |

| Time Measurement 227                               |  |

| DMA                                                |  |

| I2C Circuit 174                                    |  |

| Input Capture 157                                  |  |

| Interrupt Controller63                             |  |

| JTAG Programming, Debugging and Trace Ports 250    |  |

| Output Compare Module161                           |  |

| PMP Pinout and Connections to External Devices 189 |  |

| Reset System59                                     |  |

| RTCC 199                                           |  |

| SPI Module165                                      |  |

| Timer1143                                          |  |

| Timer2/3/4/5 (16-Bit)147                           |  |

| Typical Multiplexed Port Structure 127             |  |

| UART                                               |  |

| WDT and Power-up Timer153                          |  |

| Brown-out Reset (BOR)                              |  |

| and On-Chip Voltage Regulator                      |  |

## С

| C Compilers<br>MPLAB C18254             |

|-----------------------------------------|

| Charge Time Measurement Unit. See CTMU. |

| Clock Diagram74                         |

| Comparator                              |

| Specifications                          |

| Comparator Module219                    |

| Comparator Voltage Reference (CVref223  |

| Configuration Bit                       |

| Configuring Analog Port Pins 128        |

| CPU                                     |

| Architecture Overview                   |

| Coprocessor 0 Registers35               |

| 6                                      |

|----------------------------------------|

| 6                                      |

| 3                                      |

| 1                                      |

| 1                                      |

| 1                                      |

| ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

## D

| DC and AC Characteristics              |          |

|----------------------------------------|----------|

| Graphs and Tables                      | 307      |

| DC Characteristics                     | 258      |

| I/O Pin Input Specifications           | 263, 264 |

| I/O Pin Output Specifications          | 265      |

| Idle Current (IIDLE)                   | 261      |

| Power-Down Current (IPD)               | 262      |

| Program Memory                         |          |

| Temperature and Voltage Specifications | 259      |

| DC Characteristics (50 MHz)            | 302      |

| Idle Current (IDLE)                    | 303      |

| Power-Down Current (IPD)               | 303      |

| Development Support                    | 253      |

| Direct Memory Access (DMA) Controller  | 83       |

|                                        |          |

## Е

| Electrical Characteristics          | 257  |

|-------------------------------------|------|

| AC                                  | 269  |

| Errata                              | . 16 |

| External Clock                      |      |

| Timer1 Timing Requirements          | 275  |

| Timer2, 3, 4, 5 Timing Requirements | 276  |

| Timing Requirements                 | 270  |

| External Clock (50 MHz)             |      |

| Timing Requirements                 | 304  |

|                                     |      |

## F

| Flash Program Memory | 53 |

|----------------------|----|

| RTSP Operation       | 53 |

## L

| I/O Ports                                 | 127 |

|-------------------------------------------|-----|

| Parallel I/O (PIO)                        | 128 |

| Write/Read Timing                         | 128 |

| Input Change Notification                 | 128 |

| Instruction Set                           | 251 |

| Inter-Integrated Circuit (I2C             | 173 |

| Internal Voltage Reference Specifications | 268 |

| Internet Address                          | 341 |

| Interrupt Controller                      | 63  |

| IRG Vector and Bit Location               | 64  |

## Μ

| Memory Maps                  |

|------------------------------|

| PIC32MX110/210 Devices       |

| (4 KB RAM, 16 KB Flash)      |

| PIC32MX120/220 Devices       |

| (8 KB RAM, 32 KB Flash) 39   |

| PIC32MX130/230               |

| (16 KB RAM, 256 KB Flash) 43 |

| PIC32MX130/230 Devices       |

| (16 KB RAM, 64 KB Flash) 40  |

| PIC32MX150/250 Devices       |

| (32 KB RAM, 128 KB Flash) 41 |

| PIC32MX170/270               |