Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 256КВ (256К х 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256d-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

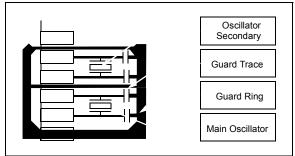

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

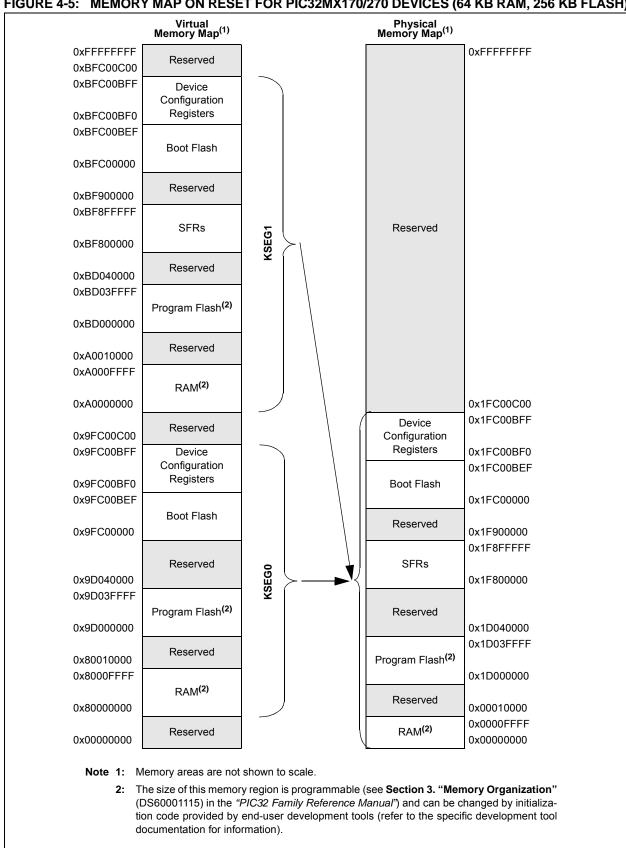

### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

| Bit<br>Range      | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24             | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24             | —                  | _                 | _                 | —                 | _                 | —                 | _                | —                |  |  |  |

| 00.40             | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16             | —                  | —                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 45.0              | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8              | 5:8 BMXDUDBA<15:8> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0               | R-0                | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0 BMXDUDBA<7:0> |                    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

## bit 9-0 BMXDUDBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |  |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | —                 |                      | —                     |                        | NVMOF             | P<3:0>           |                  |  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |  |

### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

## 6.1 Reset Control Registers

## TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         |                                 | 0         | Bits  |       |       |       |       |       |      |       |      |      | s    |      |       |      |      |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset |

| F600                        | RCON                            | 31:16     | _     | _     | _     |       | —     | _     |      | —     | _    | _    |      | _    |       | -    | -    | _     | 0000      |

| 1 000                       | ROOM                            | 15:0      | _     |       | -     |       | _     | -     | CMR  | VREGS | EXTR | SWR  |      | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx(2)   |

| E610                        | RSWRST                          | 31:16     |       | —     | -     | —     | —     | —     | —    | —     |      | —    | —    | _    | —     | _    | —    | —     | 0000      |

| 1010                        | N31/K31                         | 15:0      | _     | _     | _     | -     | _     | —     |      | —     | _    | _    | -    | _    | _     | _    | -    | SWRST | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

## 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP                      |               |                 |                   |       |            |       |           |       |          |         |          |                      |        |       |           |                       |                     |       |           |

|-----------------------------------------------------------------|---------------|-----------------|-------------------|-------|------------|-------|-----------|-------|----------|---------|----------|----------------------|--------|-------|-----------|-----------------------|---------------------|-------|-----------|

| ess                                                             |               | Bits            |                   |       |            |       |           |       |          |         |          |                      |        | ú     |           |                       |                     |       |           |

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(1</sup> ) |               | Bit Range       | 31/15             | 30/14 | 29/13      | 28/12 | 27/11     | 26/10 | 25/9     | 24/8    | 23/7     | 22/6                 | 21/5   | 20/4  | 19/3      | 18/2                  | 17/1                | 16/0  | All Reset |

| F000                                                            | OSCCON        | FCCON 31:16 — F |                   |       | LLODIV<2:0 |       |           |       | —        | SOSCRDY | PBDIVRDY | PBDI\                | /<1:0> | PL    | LMULT<2:0 | >                     | x1xx <sup>(2)</sup> |       |           |

| FUUU                                                            | 030001        | 15:0            | —                 |       | COSC<2:0   | V     | Ι         |       | NOSC<2:0 | >       | CLKLOCK  | ULOCK <sup>(3)</sup> | SLOCK  | SLPEN | CF        | UFRCEN <sup>(3)</sup> | SOSCEN              | OSWEN | xxxx(2)   |

| F010                                                            | OSCTUN        | 31:16           | _                 | _     |            | _     | _         |       |          | _       | _        | _                    | _      | _     |           | _                     | —                   | _     | 0000      |

| 1010                                                            | 030101        | 15:0            | _                 | _     |            | _     | _         |       |          | _       | _        | _                    |        |       | TUN       | l<5:0>                |                     |       | 0000      |

| 5000                                                            |               | 31:16           | - RODIV<14:0> 000 |       |            |       |           |       |          | 0000    |          |                      |        |       |           |                       |                     |       |           |

| F020                                                            | F020 REFOCON  | 15:0            | ON                |       | SIDL       | OE    | RSLP      | -     | DIVSWEN  | ACTIVE  | —        | —                    |        |       |           | ROSE                  | _<3:0>              |       | 0000      |

| F000                                                            | F030 REFOTRIM | 31:16           |                   |       |            | R     | OTRIM<8:0 | )>    |          |         |          | _                    | _      | _     | _         | _                     | _                   | _     | 0000      |

| F030                                                            |               | 15:0            | _                 | _     |            | _     | _         |       |          | -       | _        | _                    | _      | _     |           | _                     | —                   | _     | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24             |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |

| 22:16             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16             | —                 | —                 | _                 | -                 | _                 |                   |                  | —                |

| 45.0              | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8 CHSPTR<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |

| 7.0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0 CHSPTR<7:0>   |                   |                   |                   |                   |                   |                   |                  |                  |

## REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                   | CHDPTR<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

### REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         |                   | —                 | —                 | —                 | _                 | —                 |                  | —                |  |  |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |  |

| 7.0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |  |  |

## Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| REGISTER 10-3. OTF WRC. USB FOWER CONTROL REGISTER |                   |     |     |                   |                        |                   |                  |                  |  |  |

|----------------------------------------------------|-------------------|-----|-----|-------------------|------------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range                                       | Bit<br>31/23/15/7 |     |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24                                              | U-0               | U-0 | U-0 | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 31.24                                              | —                 | —   | -   | —                 | _                      | _                 | —                | _                |  |  |

| 23:16                                              | U-0               | U-0 | U-0 | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 23.10                                              | —                 | —   | -   | —                 | _                      | _                 | —                | _                |  |  |

| 15:8                                               | U-0               | U-0 | U-0 | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 15.0                                               | —                 | —   |     | —                 | _                      | —                 | —                | _                |  |  |

| 7.0                                                | R-0               | U-0 | U-0 | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |  |  |

| 7:0                                                | UACTPND           |     |     | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |  |  |

## REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| zogonai           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

## **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

### 11.3.5 OUTPUT MAPPING

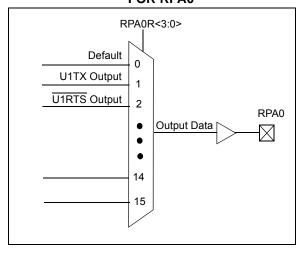

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

## 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

## 11.3.6.1 Control Register Lock Sequence

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, IOLOCK (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The Configuration bit, IOL1WAY (DEVCFG3<29>), blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

## REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | _                 | -                 | —                 |                   | _                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |  |  |  |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |

| Legend:           | HS = Set in hardware | HSC = Hardware set/cleared         |                   |  |  |  |

|-------------------|----------------------|------------------------------------|-------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                   |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | C = Clearable bit |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> | C module is busy |

|--------------------------------------------------------------------------------|------------------|

| 0 = No collision                                                               |                  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

### bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

## 20.1 PMP Control Registers

## TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 0             |       |               |       |       |         |                                   |        | Bi     | ts               |       |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|---------------|-------|---------------|-------|-------|---------|-----------------------------------|--------|--------|------------------|-------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14         | 29/13 | 28/12 | 27/11   | 26/10                             | 25/9   | 24/8   | 23/7             | 22/6  | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16         | —     | _             | -     | _     |         |                                   | -      | _      | —                | —     | —         |      |      | —    | —    | _    | 0000       |

| 7000                        | 15:0                            | 15:0          | ON    | _             | SIDL  | ADRML | IX<1:0> | PMPTTL                            | PTWREN | PTRDEN | CSF∙             | <1:0> | ALP       |      | CS1P | _    | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16         | —     | _             | -     | _     | _       |                                   | _      | _      | —                | _     | —         |      | -    | _    | —    | _    | 0000       |

| 7010                        | FININODE                        | 15:0          | BUSY  | IRQM          | <1:0> | INCM  | <1:0>   | > MODE<1:0> WAITB<1:0> WAITM<3:0> |        |        | WAITM<3:0> WAITE |       | <1:0>     | 0000 |      |      |      |      |            |

|                             |                                 | 31:16         | _     | —             | _     | _     | —       | _                                 | —      | _      | _                | _     | _         | —    | —    | _    | _    | —    | 0000       |

| 7020                        | PMADDR                          | 15:0          | _     | CS1<br>ADDR14 | _     | _     | _       |                                   |        |        |                  | /     | ADDR<10:0 | >    |      |      |      |      | 0000       |

| 7030                        | PMDOUT                          | 31:16<br>15:0 |       |               |       |       |         |                                   |        | DATAOU | T<31:0>          |       |           |      |      |      |      |      | 0000       |

| 7040                        | PMDIN                           | 31:16<br>15:0 |       |               |       |       |         |                                   |        | DATAIN | <31:0>           |       |           |      |      |      |      |      | 0000       |

| 7050                        |                                 | 31:16         | _     | _             |       | _     | -       |                                   | -      | _      | _                | _     | —         |      |      | _    | _    |      | 0000       |

| 7050                        | PMAEN                           | 15:0          | _     | PTEN14        | _     | _     | _       |                                   |        |        |                  |       | PTEN<10:0 | >    |      |      |      |      | 0000       |

| 7060                        | DMSTAT                          | 31:16         |       |               |       | _     |         |                                   | _      | _      |                  |       | —         | _    | _    |      | —    | _    | 0000       |

| 1000                        | '060 PMSTAT                     | 15:0          | IBF   | IBOV          | _     | _     | IB3F    | IB2F                              | IB1F   | IB0F   | OBE              | OBUF  | —         | _    | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

|              |                   |                   | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |

| 02.16        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

|              |                   | 1                 | 1                 |                   |                   |                   |                  |                  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |

### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

## R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

## REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

## REGISTER 27-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

- Note 1: This bit is only available on PIC32MX2XX devices.

## 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

## 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

|               |         |                                                         | Standard Opera<br>stated) |                        |            |       |                                                   |  |  |  |  |

|---------------|---------|---------------------------------------------------------|---------------------------|------------------------|------------|-------|---------------------------------------------------|--|--|--|--|

|               | ARACTER |                                                         | Operating tempe           |                        |            |       | C for Industrial<br>C for V-temp                  |  |  |  |  |

| Param.<br>No. | Symbol  | Characteristics                                         | Min.                      | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |  |  |  |

|               | VIL     | Input Low Voltage                                       |                           |                        |            |       |                                                   |  |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss                       | —                      | 0.15 Vdd   | V     |                                                   |  |  |  |  |

|               |         | I/O Pins                                                | Vss                       | —                      | 0.2 Vdd    | V     |                                                   |  |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss                       | _                      | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss                       | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |  |  |  |

|               | VIH     | Input High Voltage                                      |                           |                        |            |       |                                                   |  |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                  | —                      | Vdd        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V           | —                      | 5.5        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 VDD                  | —                      | 5.5        | V     |                                                   |  |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD                  | _                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1                       | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |  |  |  |

| DI30          | ICNPU   | Change Notification<br>Pull-up Current                  | _                         | —                      | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _                         | —                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |  |  |

|               | lı∟     | Input Leakage Current<br>(Note 3)                       |                           |                        |            |       |                                                   |  |  |  |  |

| DI50          |         | I/O Ports                                               | _                         | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |  |  |  |

| DI51          |         | Analog Input Pins                                       | _                         | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | —                         | _                      | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |  |  |  |

| DI56          |         | OSC1                                                    | _                         | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |  |  |  |

## TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

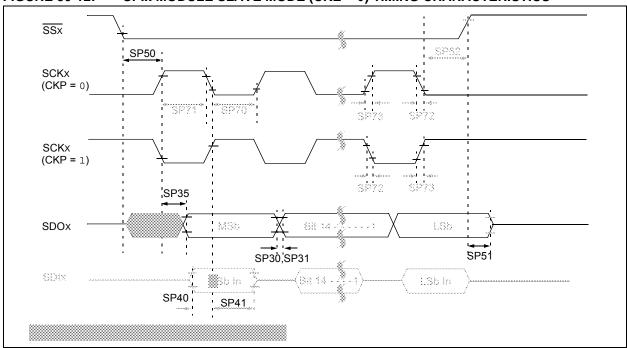

### FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

## TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | TICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |      |       |                    |  |  |

|---------------|-----------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                                                                                               | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                       | TSCK/2                                                                                                                                                                                                                                                                             | —                   | _    | ns    | —                  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                      | TSCK/2                                                                                                                                                                                                                                                                             | —                   | _    | ns    | —                  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                               | —                                                                                                                                                                                                                                                                                  | _                   |      | ns    | See parameter DO32 |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                               | —                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | See parameter DO31 |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                | —                                                                                                                                                                                                                                                                                  | —                   |      | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                | _                                                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO31 |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                       | —                                                                                                                                                                                                                                                                                  | _                   | 15   | ns    | VDD > 2.7V         |  |  |

|               | TscL2DoV              | SCKx Edge                                                          | —                                                                                                                                                                                                                                                                                  | —                   | 20   | ns    | VDD < 2.7V         |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                         | 10                                                                                                                                                                                                                                                                                 |                     |      | ns    | —                  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                       | 10                                                                                                                                                                                                                                                                                 | _                   | _    | ns    | —                  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}}\downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                                                                                                |                     |      | ns    | —                  |  |  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>             | 5                                                                                                                                                                                                                                                                                  | —                   | 25   | ns    | _                  |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                | Тѕск + 20                                                                                                                                                                                                                                                                          | —                   |      | ns    | —                  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

## TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS                                             |                        |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |  |

|----------------------------------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units                                                                                                                                           | Conditions |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |      |                                                                                                                                                 |            |  |  |  |

| MDC34a                                                         | 8                      | 13   | mA                                                                                                                                              | 50 MHz     |  |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- + CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| DC CHARACTERISTICS                |                        |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |                                                 |  |  |  |

|-----------------------------------|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max. | Units                                                                                                                                            | Conditions |                                                 |  |  |  |

| Power-Down Current (IPD) (Note 1) |                        |      |                                                                                                                                                  |            |                                                 |  |  |  |

| MDC40k                            | 10                     | 25   | μA                                                                                                                                               | -40°C      | Base Power-Down Current                         |  |  |  |

| MDC40n                            | 250                    | 500  | μA                                                                                                                                               | +85°C      |                                                 |  |  |  |

| Module Differential Current       |                        |      |                                                                                                                                                  |            |                                                 |  |  |  |

| MDC41e                            | 10                     | 55   | μA                                                                                                                                               | 3.6V       | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |

| MDC42e                            | 23                     | 55   | μA                                                                                                                                               | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |

| MDC43d                            | 1100                   | 1300 | μA                                                                                                                                               | 3.6V       | ADC: Aladc (Notes 3,4)                          |  |  |  |

## TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

• Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set