Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 33                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

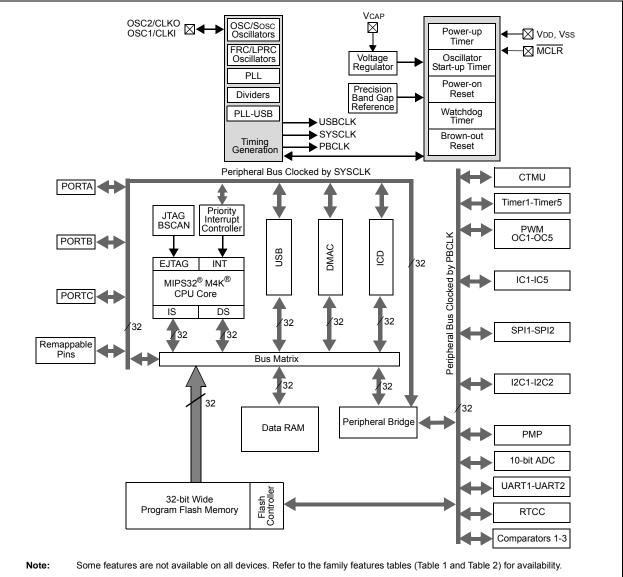

**BLOCK DIAGRAM**

This document contains device-specific information for PIC32MX1XX/2XX 28/36/44-pin Family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/36/44-pin Family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1:

|          |                        | Pin Nu                            | mber <sup>(1)</sup> | -                               |             |                |                                           |

|----------|------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                  | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                   | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                   | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                  | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                     | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                     | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                   | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                     | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                  | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                   | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                   | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                   | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                  | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                  | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                  | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                  | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                  | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                  | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                  | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                  | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                  | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                     |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                     |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe        | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

#### DINOUT I/O DESCRIPTIONS (CONTINUED)

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

# TABLE 3-2: COPROCESSOR 0 REGISTERS

**Note 1:** Registers used in exception processing.

**2:** Registers used during debug.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

# 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

# 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

# 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |                  |       |             |       |               |           |         |         |                      |                     |       |      |                       |        |        |         |           |

|--------------------------------------------|---------------------------------|-----------|------------------|-------|-------------|-------|---------------|-----------|---------|---------|----------------------|---------------------|-------|------|-----------------------|--------|--------|---------|-----------|

| ess                                        |                                 | 0         | Bits             |       |             |       |               |           |         |         |                      |                     |       |      |                       |        | ú      |         |           |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15            | 30/14 | 29/13       | 28/12 | 27/11         | 26/10     | 25/9    | 24/8    | 23/7                 | 22/6                | 21/5  | 20/4 | 19/3                  | 18/2   | 17/1   | 16/0    | All Reset |

| F000                                       | 000 OSCCON                      | 31:16     | — — PLLODIV<2:0> |       |             |       | FRCDIV<2:0> — |           |         | SOSCRDY | PBDIVRDY             | PBDIVRDY PBDIV<1:0> |       |      | PLLMULT<2:0>          |        |        |         |           |

| FUUU                                       | 030001                          | 15:0      | 15:0 —           |       | COSC<2:0> — |       |               | NOSC<2:0> |         | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK               | SLPEN | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN  | xxxx(2) |           |

| F010                                       | OSCTUN                          | 31:16     | _                | _     |             | _     | _             |           |         | _       | _                    | _                   | _     | _    |                       | _      | —      | _       | 0000      |

| 1010                                       | 030101                          | 15:0      | _                | _     |             | _     | _             |           |         | _       | _                    | _                   |       |      | TUN                   | l<5:0> |        |         | 0000      |

| 5000                                       |                                 | 31:16     | _                |       |             |       |               |           |         |         | RODIV<1              | 4:0>                |       |      |                       |        |        |         | 0000      |

| F020                                       | REFOCON                         | 15:0      | ON               |       | SIDL        | OE    | RSLP          | -         | DIVSWEN | ACTIVE  | —                    | —                   |       |      |                       | ROSE   | _<3:0> |         | 0000      |

| F000                                       | DEEOTDIM                        | 31:16     | 1:16 ROTRIM<8:0> |       |             |       |               |           |         |         |                      | _                   | 0000  |      |                       |        |        |         |           |

| F030                                       | 030 REFOTRIM                    | 15:0      | _                | _     |             | _     | _             |           |         | -       | _                    | _                   | _     | _    |                       | _      | —      | _       | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|

|              | U-0                         | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                           | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |

|              | R/W-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(1,3)</sup> |                              |                   |                   |                     |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                       | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |

| 15:8         | ON                          | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |

|              | U-0                         | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                             |                              |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |

# REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

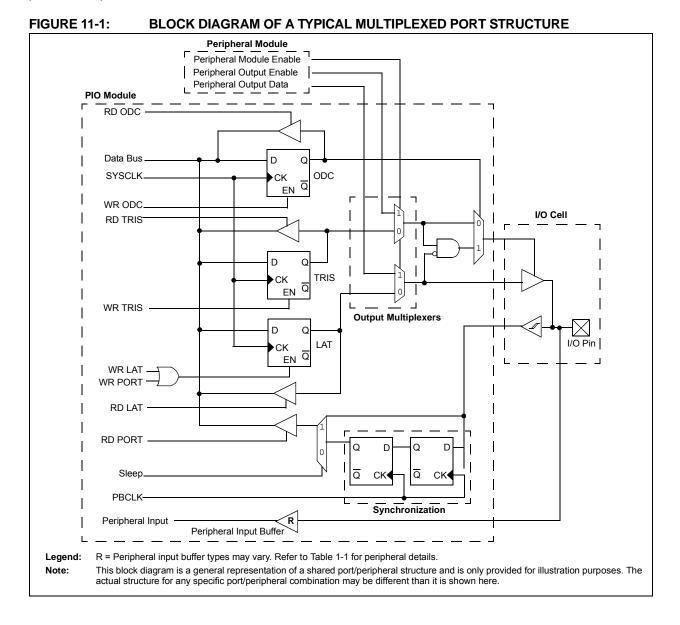

# 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Key features of this module include:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

### TABLE 11-5: PORTC REGISTER MAP

| ess                         | -                                 |           |       |       |       |       |       |       |          |                       |                         | Bits                  |                       |                         |          |                       |          |          |            |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-----------------------|-----------------------|-------------------------|----------|-----------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                  | 21/5                  | 20/4                    | 19/3     | 18/2                  | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     |       | _     |       |       | —     | —     | _        | -                     | _                       | -                     | _                     | _                       | —        | _                     | —        |          | 0000       |

| 0200                        | ,                                 | 15:0      | —     | —     | —     | —     | —     | —     |          |                       | —                       |                       |                       | _                       | ANSC3(4) | ANSC2 <sup>(3)</sup>  | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | —     | —     | —     | —     | —        | —                     | —                       | —                     | —                     | —                       | —        | —                     | —        |          | 0000       |

| 0210                        | 11100                             | 15:0      | _     | _     | —     | —     | —     | —     | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup> | TRISC5 <sup>(3)</sup> | TRISC4 <sup>(3)</sup>   | TRISC3   | TRISC2 <sup>(3)</sup> | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | —     | —     | _        |                       | _                       |                       | _                     |                         |          |                       |          |          | 0000       |

| 0220                        |                                   | 15:0      | _     | _     | —     | —     | —     | —     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>    | RC5 <sup>(3)</sup>    | RC4 <sup>(3)</sup>      | RC3      | RC2 <sup>(3)</sup>    | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | _     | _     | —     | —     | —     | —     | _        |                       | _                       |                       |                       | _                       | —        |                       | —        | —        | 0000       |

| 0230                        | LAIC                              | 15:0      |       |       | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>  | LATC5 <sup>(3)</sup>  | LATC4 <sup>(3)</sup>    | LATC3    | LATC2 <sup>(3)</sup>  | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     |       |       | _     | _     | _     | _     | _        |                       |                         |                       |                       |                         | _        |                       | _        | _        | 0000       |

| 6240                        | ODCC                              | 15:0      |       |       | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>  | ODCC5 <sup>(3)</sup>  | ODCC4 <sup>(3)</sup>    | ODCC3    | ODCC2 <sup>(3)</sup>  | ODCC1    | ODCC0    | 0000       |

| 0050                        |                                   | 31:16     |       |       | —     | —     | —     | -     | —        | -                     | _                       | -                     | —                     | —                       | —        | —                     | —        | —        | 0000       |

| 6250                        | CNPUC                             | 15:0      | _     | _     | _     | _     | —     | —     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup> | CNPUC5 <sup>(3)</sup> | CNPUC4 <sup>(3)</sup>   | CNPUC3   | CNPUC2 <sup>(3)</sup> | CNPUC1   | CNPUC0   | 0000       |

| 0000                        |                                   | 31:16     | _     | _     | _     | _     | _     | _     | —        | _                     | _                       | _                     | _                     | —                       | _        | —                     | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | —     | —     | —     | —     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup> | CNPDC5 <sup>(3)</sup> | CNPDC4 <sup>(3)</sup>   | CNPDC3   | CNPDC2 <sup>(3)</sup> | CNPDC1   | CNPDC0   | 0000       |

| 0070                        | anaana                            | 31:16     | _     | _     | —     | —     | —     | —     | _        | _                     | _                       | _                     | —                     | —                       | —        | _                     | —        | —        | 0000       |

| 6270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | —     | —     | —     | _        | _                     | _                       | _                     | _                     | —                       | _        | _                     | —        | _        | 0000       |

|                             |                                   | 31:16     | _     | _     | _     |       | —     | _     |          |                       | _                       |                       | _                     | _                       | _        | _                     | —        | —        | 0000       |

| 6280                        | CNENC                             | 15:0      | _     | _     | _     |       | —     | _     | CNIEC9   | CNIEC8(3)             | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)             | CNIEC5 <sup>(3)</sup> | CNIEC4 <sup>(3)</sup>   | CNIEC3   | CNIEC2 <sup>(3)</sup> | CNIEC1   | CNIEC0   | 0000       |

|                             |                                   | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       |                       | _                     | _                       | —        |                       | —        | —        | 0000       |

| 6290 CNS                    | CNSTATC                           | 15:0      | _     | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6(3)           | CNSTATC5(3)           | CNSTATC4 <sup>(3)</sup> | CNSTATC3 | CNSTATC2(3)           | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

3: This bit is only available on 44-pin devices.

4: This bit is only available on USB-enabled devices with 36 or 44 pins.

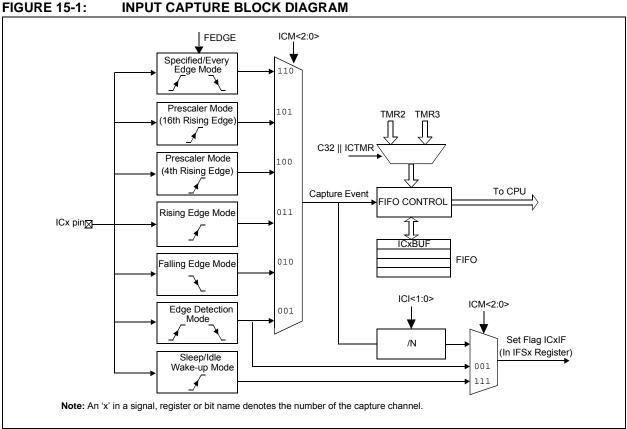

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        | —                    | —                 | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | —                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

# REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

# 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        | _                 | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MIN10<2:0>        |                   |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   |                   | SEC01<3:0>        |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

|              |                   |                   | 1                 |                   |                   |                   |                  |                  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | -                 | —                 | _                 | _                 |                   | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7:0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | BUFS              |                   | SMPI<3:0>         |                   |                   |                   | BUFM             | ALTS             |

# REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | eadable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |

|-------------------|------------------------------|----------------------|------------------------------------|--|--|

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVdd               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

#### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

#### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

#### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-----------------------|------------------|------------------|--|

| 24.04        | r-0               | r-1               | r-1               | R/P               | r-1                  | r-1                   | r-1              | R/P              |  |

| 31:24        |                   | _                 |                   | CP                | —                    | _                     | _                | BWP              |  |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1                  | R/P                   | R/P              | R/P              |  |

| 23:16        |                   | _                 |                   | _                 | —                    | PWP<8:6>(3)           |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                  | R/P                   | r-1              | r-1              |  |

| 15:8         |                   | PWP<5:0>          |                   |                   |                      |                       | —                | —                |  |

| 7:0          | r-1               | r-1               | r-1               | R/P               | R/P                  | R/P                   | R/P              | R/P              |  |

|              |                   |                   |                   | ICESEL            | <1:0> <sup>(2)</sup> | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |  |

## REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 Reserved: Write '0'

bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device. 1 = Protection is disabled

0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

- bit 23-19 Reserved: Write '1'

- **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "**Pin Diagrams**" section for availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

### TABLE 30-34: ADC MODULE SPECIFICATIONS

|               |            |                                                      | Standard Operating Conditions (see Note 5): 2.5V to 3.6V (unless otherwise stated) |              |                                  |          |                                                                                                         |  |  |

|---------------|------------|------------------------------------------------------|------------------------------------------------------------------------------------|--------------|----------------------------------|----------|---------------------------------------------------------------------------------------------------------|--|--|

|               |            |                                                      |                                                                                    |              |                                  |          | a +85°C for Industrial<br>a +105°C for V-temp                                                           |  |  |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                                                                               | Typical      | Max.                             | Units    | Conditions                                                                                              |  |  |

| Device        | Supply     |                                                      |                                                                                    |              |                                  |          |                                                                                                         |  |  |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                  | —            | Lesser of<br>VDD + 0.3 or<br>3.6 | V        | _                                                                                                       |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                                                                                | _            | AVdd                             | V        | (Note 1)                                                                                                |  |  |

| Referen       | ce Inputs  | ·                                                    |                                                                                    |              |                                  |          | ·                                                                                                       |  |  |

| AD05<br>AD05a | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                                                                  | _            | AVDD<br>3.6                      | V<br>V   | (Note 1)<br>VREFH = AVDD (Note 3)                                                                       |  |  |

| AD06          | Vrefl      | Reference Voltage Low                                | AVss                                                                               | —            | Vrefh – 2.0                      | V        | (Note 1)                                                                                                |  |  |

| AD07          | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                                                                                | _            | AVDD                             | V        | (Note 3)                                                                                                |  |  |

| AD08<br>AD08a | IREF       | Current Drain                                        | _                                                                                  | 250<br>      | 400<br>3                         | μΑ<br>μΑ | ADC operating<br>ADC off                                                                                |  |  |

| Analog        | Input      | ·                                                    |                                                                                    |              |                                  |          |                                                                                                         |  |  |

| AD12          | VINH-VINL  | Full-Scale Input Span                                | VREFL                                                                              | —            | Vrefh                            | V        | —                                                                                                       |  |  |

| AD13          | VINL       | Absolute VINL Input<br>Voltage                       | AVss – 0.3                                                                         | _            | AVDD/2                           | V        | _                                                                                                       |  |  |

| AD14          | Vin        | Absolute Input Voltage                               | AVss - 0.3                                                                         | _            | AVDD + 0.3                       | V        | —                                                                                                       |  |  |

| AD15          | —          | Leakage Current                                      | _                                                                                  | ±0.001       | ±0.610                           | μA       | $V_{INL} = AV_{SS} = V_{REFL} = 0V,$<br>$AV_{DD} = V_{REFH} = 3.3V$<br>Source Impedance = 10 k $\Omega$ |  |  |

| AD17          | RIN        | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                  | _            | 5k                               | Ω        | (Note 1)                                                                                                |  |  |

| ADC Ac        | curacy – N | leasurements with Exte                               | rnal VREF+/V                                                                       | REF-         |                                  |          |                                                                                                         |  |  |

| AD20c         | Nr         | Resolution                                           |                                                                                    | 10 data bits | S                                | bits     | —                                                                                                       |  |  |

| AD21c         | INL        | Integral Non-linearity                               | > -1                                                                               | _            | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                                        |  |  |

| AD22c         | DNL        | Differential Non-linearity                           | > -1                                                                               | _            | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                            |  |  |

| AD23c         | Gerr       | Gain Error                                           | > -1                                                                               | —            | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                                        |  |  |

| AD24c         | Eoff       | Offset Error                                         | > -1                                                                               | _            | < 1                              | Lsb      | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                                        |  |  |

| AD25c         | _          | Monotonicity                                         | _                                                                                  | _            |                                  | _        | Guaranteed                                                                                              |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

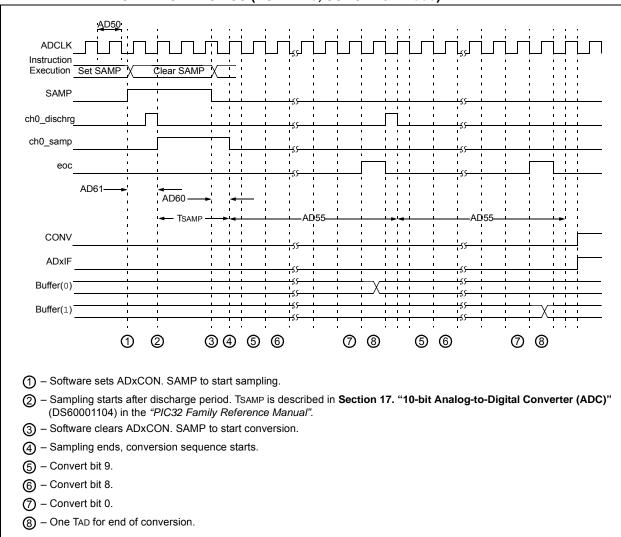

# FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)