Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                 |                                                                                 |

|------------------------|---------------------------------------------------------------------------------|

| oduct Status           | Obsolete                                                                        |

| ore Processor          | MIPS32® M4K™                                                                    |

| ore Size               | 32-Bit Single-Core                                                              |

| peed                   | 40MHz                                                                           |

| nnectivity             | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                        |

| ripherals              | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| mber of I/O            | 33                                                                              |

| ogram Memory Size      | 256KB (256K x 8)                                                                |

| gram Memory Type       | FLASH                                                                           |

| PROM Size              | -                                                                               |

| M Size                 | 64K x 8                                                                         |

| age - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| a Converters           | A/D 13x10b                                                                      |

| illator Type           | Internal                                                                        |

| erating Temperature    | -40°C ~ 85°C (TA)                                                               |

| unting Type            | Surface Mount                                                                   |

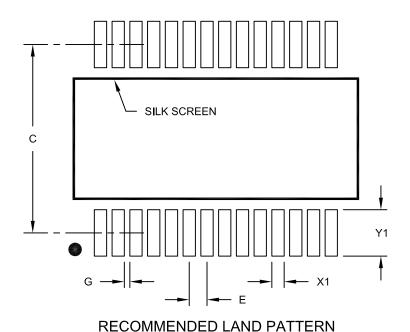

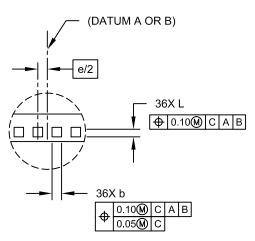

| ckage / Case           | 44-VFTLA Exposed Pad                                                            |

| pplier Device Package  | 44-VTLA (6x6)                                                                   |

| chase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256dt-i-tl |

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

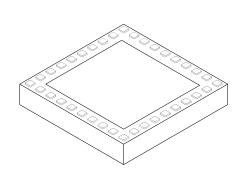

44-PIN QFN (TOP VIEW)(1,2,3,5)

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

.4

| Pin # | Full Pin Name                                    |

|-------|--------------------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         |

| 2     | RPC6/PMA1/RC6                                    |

| 3     | RPC7/PMA0/RC7                                    |

| 4     | RPC8/PMA5/RC8                                    |

| 5     | RPC9/CTED7/PMA6/RC9                              |

| 6     | Vss                                              |

| 7     | VCAP                                             |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       |

| 9     | PGEC2/RPB11/D-/RB11                              |

| 10    | Vusb3v3                                          |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 12    | PGED4/TMS/PMA10/RA10                             |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 16    | AVss                                             |

| 17    | AVDD                                             |

| 18    | MCLR                                             |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 23   | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 24   | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 25   | AN6/RPC0/RC0                              |

| 26   | AN7/RPC1/RC1                              |

| 27   | AN8/RPC2/PMA2/RC2                         |

| 28   | VDD                                       |

| 29   | Vss                                       |

| 30   | OSC1/CLKI/RPA2/RA2                        |

| 31   | OSC2/CLKO/RPA3/RA3                        |

| 32   | TDO/RPA8/PMA8/RA8                         |

| 33   | SOSCI/RPB4/RB4                            |

| 34   | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 35   | TDI/RPA9/PMA9/RA9                         |

| 36   | AN12/RPC3/RC3                             |

| 37   | RPC4/PMA4/RC4                             |

| 38   | RPC5/PMA3/RC5                             |

| 39   | Vss                                       |

| 40   | VDD                                       |

| 41   | RPB5/USBID/RB5                            |

| 42   | VBUS                                      |

| 43   | RPB7/CTED3/PMD5/INT0/RB7                  |

| 44   | RPB8/SCL1/CTED10/PMD4/RB8                 |

1

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

- Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

- 5: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup> | •                               |             |                |                                                                         |

|----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>   | 41(3)                           | ı           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                | 2                                 | 33                  | 19                              | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                | 3                                 | 34                  | 20                              | I           | ST             | 1                                                                       |

| CTED3    | 13                | 16                                | 17                  | 43                              | I           | ST             | 1                                                                       |

| CTED4    | 15                | 18                                | 19                  | 1                               | I           | ST             | 1                                                                       |

| CTED5    | 22                | 25                                | 28                  | 14                              | I           | ST             | 1                                                                       |

| CTED6    | 23                | 26                                | 29                  | 15                              | I           | ST             | 1                                                                       |

| CTED7    | _                 | _                                 | 20                  | 5                               | I           | ST             | 1                                                                       |

| CTED8    | _                 | _                                 | -                   | 13                              | I           | ST             | 1                                                                       |

| CTED9    | 9                 | 12                                | 10                  | 34                              | I           | ST             | 1                                                                       |

| CTED10   | 14                | 17                                | 18                  | 44                              | I           | ST             | 1                                                                       |

| CTED11   | 18                | 21                                | 24                  | 8                               | I           | ST             | 1                                                                       |

| CTED12   | 2                 | 5                                 | 36                  | 22                              | I           | ST             | 1                                                                       |

| CTED13   | 3                 | 6                                 | 1                   | 23                              | I           | ST             | 1                                                                       |

| CTPLS    | 21                | 24                                | 27                  | 11                              | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |

| PGEC1    | 2                 | 5                                 | 36                  | 22                              | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                | 21                                | 24                  | 8                               | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |

| PGEC2    | 19                | 22                                | 25                  | 9                               | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>   | 41 <sup>(2)</sup>               | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)               | 19 <sup>(3)</sup>               | 1/0         | 31             | Communication Channel 3                                                 |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               |             | ST             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>   | 20 <sup>(3)</sup>               | 1 '         | 31             | Debugging Communication Channel 3                                       |

| PGED4    | _                 | _                                 | 3                   | 12                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |

| PGEC4    | _                 | _                                 | 4                   | 13                              | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

**3:** Pin number for PIC32MX2XX devices only.

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Read as '0' bit 15-13 **Unimplemented:** Read as '0'

bit 12 MVEC: Multi Vector Configuration bit

1 = Interrupt controller configured for Multi-vectored mode

0 = Interrupt controller configured for Single-vectored mode

bit 11 Unimplemented: Read as '0'

bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

001 = Interrupts of group priority 1 start the Interrupt Proximity timer

000 = Disables Interrupt Proximity timer

bit 7-5 **Unimplemented:** Read as '0'

bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 2

INT2EP: External Interrupt 2 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 0 **INTOEP:** External Interrupt 0 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

### 8.1 Oscillator Control Regiters

#### TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP

| ess                         |             |           |       |       |          |            |           |           |           |        | Bits    |                      |          |       |        |           |           |       | vo.        |

|-----------------------------|-------------|-----------|-------|-------|----------|------------|-----------|-----------|-----------|--------|---------|----------------------|----------|-------|--------|-----------|-----------|-------|------------|

| Virtual Address<br>(BF80_#) |             | Bit Range | 31/15 | 30/14 | 29/13    | 28/12      | 27/11     | 26/10     | 25/9      | 24/8   | 23/7    | 22/6                 | 21/5     | 20/4  | 19/3   | 18/2      | 17/1      | 16/0  | All Resets |

| F000                        | OCCON       | 31:16     | _     |       | Р        | LLODIV<2:0 | )>        | F         | RCDIV<2:0 | )>     |         | SOSCRDY              | PBDIVRDY | PBDI\ | /<1:0> | PL        | LMULT<2:0 | >     | x1xx(2)    |

| F000                        | F000 OSCCON | 15:0      | _     |       | COSC<2:0 | )>         | _         | NOSC<2:0> |           |        | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK    | SLPEN | CF     | UFRCEN(3) | SOSCEN    | OSWEN | xxxx(2)    |

| E010                        | OSCTUN      | 31:16     | _     |       | _        | _          | -         | _         | _         | _      | _       | _                    | -        | _     | _      | _         | _         | _     | 0000       |

| F010                        | OSCIUN      | 15:0      | _     |       | _        | _          | -         | _         | _         | _      | _       | _                    |          |       | TUN    | V<5:0>    |           |       | 0000       |

| <b>-</b> 000                | DEEOCON     | 31:16     | _     |       |          |            |           |           |           |        | RODIV<1 | 14:0>                |          |       |        |           |           |       | 0000       |

| F020                        | REFOCON     | 15:0      | ON    |       | SIDL     | OE         | RSLP      | _         | DIVSWEN   | ACTIVE | _       | _                    | _        | _     |        | ROSE      | L<3:0>    |       | 0000       |

| F000                        | REFOTRIM    | 31:16     |       |       |          | R          | OTRIM<8:0 | )>        | )> _      |        |         |                      |          | 1     | _      | _         |           | _     | 0000       |

| F030                        | KEFUIKIM    | 15:0      | _     | _     | _        | _          | 1         | ı         | _         | _      |         | _                    | _        | 1     | _      | _         | ı         | _     | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUE) |

|-----------------------------------------------------|

|-----------------------------------------------------|

| sse                         |                                 |               |        |       |       |       | •      |       | -    | Bi       | ts           |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|----------|--------------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8     | 23/7         | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | _      | _     | _     | _     | ı      | _     |      | _        | ı            | ı      | _      | _      | I      | ı      | _      | ı      | 0000       |

| 3200                        | DCH2CFTR                        | 15:0          |        |       |       |       |        |       |      | CHCPT    | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2200                        | DCH2DAT                         | 31:16         | _      | _     | _     | _     | ı      | _     | _    | _        | -            | ı      | _      | _      | ı      | ı      | _      | ı      | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _      |       | _     | -     | 1      | _     | -    | 1        |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 32AU                        | DCH3CON                         | 15:0          | CHBUSY | _     | _     | _     | -      | _     | _    | CHCHNS   | CHEN         | CHAED  | CHCHN  | CHAEN  | -      | CHEDET | CHPR   | I<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        |              |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3200                        | DOI IOLOON                      | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |          | CFORCE       | CABORT | PATEN  | SIRQEN | AIRQEN |        | _      |        | FF00       |

| 32C0                        | DCH3INT                         | 31:16         | _      | _     | _     | _     | ı      | _     | _    | _        | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | DOTIONAL                        | 15:0          | _      | _     | _     | _     | _      | _     | _    | _        | CHSDIF       | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF |            |

| 32D0                        | DCH3SSA                         | 31:16         |        |       |       |       |        |       |      | CHSSA    | <31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      |          |              |        |        |        |        |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHDSA    | <31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         |        |       |       |       |        |       |      |          |              |        |        |        |        |        |        |        | 0000       |

| 32F0                        | DCH3SSIZ                        | 15:0          | _      | _     | _     | _     |        | _     |      | CHSSIZ   | ~<br>?<15:0> |        | _      |        |        |        | _      |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | —        |              | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3300                        | DCH3DSIZ                        | 15:0          |        |       |       |       |        |       |      | CHDSIZ   | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3310                        | DCH3SPTR                        | 15:0          |        |       |       |       |        |       |      | CHSPT    | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2000                        | DOLLODDED                       | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3320                        | DCH3DPTR                        | 15:0          |        |       |       |       |        |       |      | CHDPTI   | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2220                        | DCH3CSIZ                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | _        | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3330                        | DCH3C3IZ                        | 15:0          |        |       |       |       |        |       |      | CHCSIZ   | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         |        | _     | _     | _     | _      | _     | _    |          | _            | _      | _      | _      | _      | _      | _      |        | 0000       |

| JJ-0                        | POLIDOL IK                      | 15:0          |        |       |       |       |        |       |      | CHCPTI   | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | _      | _     | _     | _     | -      | _     | _    | _        | 1            |        | _      | _      | -      |        | _      | -      | 0000       |

| 0000                        | DONODAI                         | 15:0          | — I    | _     | _     | _     |        | _     |      | <u> </u> |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

| 31.24        | _                 | _                 | _                 | 1                 | _                 | _                 | _                     |                         |

| 23:16        | U-0                   | U-0                     |

| 23.10        | _                 | _                 | -                 | _                 | _                 | _                 | _                     | _                       |

| 15:8         | U-0                   | U-0                     |

| 15.6         | _                 | _                 | _                 | 1                 | _                 | _                 | _                     |                         |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | O I/ (LLIL        | 7ti i7tOFIL       | TRESSIVILIE       | IDLLIL            | IIMIL             | 00111             | OLIVIC                | DETACHIE <sup>(3)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 STALLIE: STALL Handshake Interrupt Enable bit

1 = STALL interrupt is enabled0 = STALL interrupt is disabled

bit 6 ATTACHIE: ATTACH Interrupt Enable bit

1 = ATTACH interrupt is enabled0 = ATTACH interrupt is disabled

bit 5 RESUMEIE: RESUME Interrupt Enable bit

1 = RESUME interrupt is enabled0 = RESUME interrupt is disabled

bit 4 IDLEIE: Idle Detect Interrupt Enable bit

1 = Idle interrupt is enabled0 = Idle interrupt is disabled

bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

1 = TRNIF interrupt is enabled0 = TRNIF interrupt is disabled

bit 2 SOFIE: SOF Token Interrupt Enable bit

1 = SOFIF interrupt is enabled0 = SOFIF interrupt is disabled

bit 1 **UERRIE:** USB Error Interrupt Enable bit<sup>(1)</sup>

1 = USB Error interrupt is enabled

0 = USB Error interrupt is disabled

bit 0 URSTIE: USB Reset Interrupt Enable bit(2)

1 = URSTIF interrupt is enabled0 = URSTIF interrupt is disabled

**DETACHIE:** USB Detach Interrupt Enable bit<sup>(3)</sup>

1 = DATTCHIF interrupt is enabled0 = DATTCHIF interrupt is disabled

Note 1: For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

2: Device mode.

3: Host mode.

**TABLE 11-6:** PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FAU4                        | INTIK            | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17100                       | IIVIZIX          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 17.00                       | IIIII            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| FA10                        | INT4R            | 31:16     |       |       | _     | _     | _     |       |      |      |      | _    |      |      | _    | _     | _      | _    | 0000       |

| .,                          |                  | 15:0      |       |       |       | _     |       |       |      |      |      | _    |      |      |      | INT4F | R<3:0> | ı    | 0000       |

| FA18                        | T2CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CKI | R<3:0> |      | 0000       |

| FA1C                        | T3CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       |       | _     | _     | _     | _     |      |      |      | _    |      |      |      | T3CKI | ₹<3:0> | ı    | 0000       |

| FA20                        | T4CKR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T4CKI | R<3:0> |      | 0000       |

| FA24                        | T5CKR            | 31:16     |       |       | _     |       | _     |       |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    |      | T5CKI | R<3:0> |      | 0000       |

| FA28                        | IC1R             | 31:16     | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

| FA2C                        | IC2R             | 31:16     | _     | _     | _     |       |       | _     |      | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | _                | 15:0      | _     | _     | _     |       |       | _     |      | _    |      | _    |      | _    |      | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IC3R             | 31:16     | _     | _     | _     |       |       | _     |      | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

|                             |                  | 15:0      |       | _     |       |       |       | _     |      | _    |      | _    |      | _    |      | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R             | 31:16     |       |       |       |       |       |       |      |      |      |      |      |      |      |       |        | _    | 0000       |

|                             |                  | 15:0      |       |       |       |       |       |       |      |      |      |      |      |      |      | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R             | 31:16     |       | _     |       |       |       | _     |      | _    |      | _    |      | _    | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     |       |       |       | _     |      | _    |      | _    |      | _    |      | IC5R  | <3:0>  |      | 0000       |

| FA48                        | OCFAR            | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     |      | _    | _    | _    |      | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA4C                        | OCFBR            | 31:16     |       | _     | _     | _     | _     | _     |      |      |      | _    |      |      | _    | _     |        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

|                             | •                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| sss                         |                      |               | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |           |          |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1     | 16/0 | All Resets |

| FB00                        | RPA0R                | 31:16<br>15:0 | _     |       | _     |       |       |       | _    |      |      | _    | _    | _    | -    | —<br>RPA0 | -        | _    | 0000       |

|                             |                      | 31:16         |       |       |       |       |       |       |      |      |      |      |      | _    | _    | _         | _        | _    | 0000       |

| FB04                        | RPA1R                | 15:0          | _     | _     | _     |       | _     |       |      | _    |      | _    | _    | _    |      | RPA1      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     |       | _     |       | _     |       | _    | _    |      | _    | _    | _    |      | _         | _        | _    | 0000       |

| FB08                        | RPA2R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA2      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| FB0C                        | RPA3R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA3      | <3:0>    |      | 0000       |

| ED40                        | RPA4R                | 31:16         | _     | 1     | _     |       | _     |       | _    | _    | 1    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| FB10                        | RPA4R                | 15:0          | _     |       | _     | _     | _     |       | _    | _    |      | _    | _    | _    |      | RPA4      | <3:0>    |      | 0000       |

| FB20                        | RPA8R <sup>(1)</sup> | 31:16         | _     | 1     | _     | -     | _     | -     | _    | _    | 1    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| 1 020                       | IN AOIN.             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA8      | <3:0>    |      | 0000       |

| FB24                        | RPA9R <sup>(1)</sup> | 31:16         | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | _    | -    | _         | _        | _    | 0000       |

|                             |                      | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA9      | <3:0>    |      | 0000       |

| FB2C                        | RPB0R                | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |           |          | _    | 0000       |

|                             |                      | 15:0          |       |       | _     |       |       |       |      |      |      |      |      |      |      | RPB0      |          |      | 0000       |

| FB30                        | RPB1R                | 31:16<br>15:0 |       |       | _     |       |       |       |      |      |      |      |      |      |      | RPB1      | -2:0>    | _    | 0000       |

|                             |                      | 31:16         |       |       | _     |       |       |       |      |      |      | _    | _    | _    | _    | — KFB1    | <u> </u> | _    | 0000       |

| FB34                        | RPB2R                | 15:0          | _     |       |       |       |       |       |      |      |      | _    | _    |      |      | RPB2      |          | _    | 0000       |

|                             |                      | 31:16         | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _    | —         | _        | l _  | 0000       |

| FB38                        | RPB3R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB3      | <3:0>    |      | 0000       |

|                             |                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _         | _        | _    | 0000       |

| FB3C                        | RPB4R                | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB4      | <3:0>    |      | 0000       |

| ED 40                       | DDDCD                | 31:16         | _     | 1     | _     | -     | _     |       | _    | _    | 1    | _    | _    | _    | -    | _         | _        | _    | 0000       |

| FB40                        | RPB5R                | 15:0          | _     |       | _     |       | _     | -     | _    | _    |      | _    | _    | _    |      | RPB5      | <3:0>    |      | 0000       |

| FB44                        | RPB6R <sup>(2)</sup> | 31:16         | -     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _         | _        | _    | 0000       |

| 1 044                       | INF DOIN, 7          | 15:0          | _     | 1     | _     | 1     | -     | 1     | -    | -    | 1    | _    | _    | _    |      | RPB6      | <3:0>    |      | 0000       |

| FB48                        | RPB7R                | 31:16         | _     |       | _     |       | _     |       | _    | _    |      | _    |      |      | _    | _         | _        | _    | 0000       |

| . 2 .0                      | 2                    | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | RPB7      | <3:0>    |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register is only available on 44-pin devices. Note 1:

This register is only available on PIC32MX1XX devices. 2:

This register is only available on 36-pin and 44-pin devices.

| PIC32IVIA | (1XX/2X | X 28/36 | )/44-PIN | Y FAIVIII | _ Y |  |

|-----------|---------|---------|----------|-----------|-----|--|

| NOTES:    |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

#### REGISTER 17-3: SPIXSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        |                   | _                 | _                 |                   | R)                | KBUFELM<4:0       | 0>               |                  |  |

| 22.46        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        | _                 | _                 | _                 |                   | TXBUFELM<4:0>     |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |

| 15:8         | _                 | _                 | _                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | _                 | SPITBF           | SPIRBF           |  |

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-24 RXBUFELM<4:0>: Receive Buffer Element Count bits (valid only when ENHBUF = 1)

bit 23-21 Unimplemented: Read as '0'

bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

bit 15-13 Unimplemented: Read as '0'

bit 12 FRMERR: SPI Frame Error status bit

1 = Frame error detected

0 = No Frame error detected

This bit is only valid when FRMEN = 1.

bit 11 SPIBUSY: SPI Activity Status bit

1 = SPI peripheral is currently busy with some transactions

0 = SPI peripheral is currently idle

bit 10-9 **Unimplemented:** Read as '0'

bit 8 SPITUR: Transmit Under Run bit

1 = Transmit buffer has encountered an underrun condition

0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

1 = When SPI module shift register is empty

0 = When SPI module shift register is not empty

bit 6 **SPIROV:** Receive Overflow Flag bit

1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1)

1 = RX FIFO is empty (CRPTR = SWPTR)

0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

bit 4 Unimplemented: Read as '0'

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits(1)

- 11 = Wait of 4 TPB

- 10 = Wait of 3 TPB

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

#### For Read operations:

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- Note 1: Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 ΤΡΒCLK cycle for a write operation; WAITB = 1 ΤΡΒCLK cycle, WAITE = 0 ΤΡΒCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

#### 26.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 26-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

TABLE 26-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМИ                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| I2C1                         | I2C1MD                       | PMD5<16>                       |

| I2C2                         | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

<sup>2:</sup> The module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

#### **TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS**

AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$  for V-temp

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                      | Min.  | Typical | Max.  | Units | Conditions                           |

|---------------|--------|---------------------------------------------------------------------|-------|---------|-------|-------|--------------------------------------|

| OS50          | FPLLI  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51          | Fsys   | On-Chip VCO System Frequency                                        | 60    | _       | 120   | MHz   | _                                    |

| OS52          | TLOCK  | PLL Start-up Time (Lock Time)                                       | _     | _       | 2     | ms    | _                                    |

| OS53          | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      | -0.25 | _       | +0.25 | %     | Measured over 100 ms period          |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- **2:** This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### **TABLE 30-19: INTERNAL FRC ACCURACY**

| AC CHARACTERISTICS |                                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |            |  |  |

|--------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|

| Param.<br>No.      | Characteristics                                 | Min.                                                                                                                                                                                                                                           | Typical | Max. | Units | Conditions |  |  |

| Internal           | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                |         |      |       |            |  |  |

| F20b               | FRC                                             | -0.9                                                                                                                                                                                                                                           | _       | +0.9 | %     | _          |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### **TABLE 30-20: INTERNAL LPRC ACCURACY**

| AC CHARACTERISTICS |                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |       |            |  |  |

|--------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|

| Param.<br>No.      | Characteristics                 | Min.                                                                                                                                                                                                    | Typical | Max. | Units | Conditions |  |  |

| LPRC @             | LPRC @ 31.25 kHz <sup>(1)</sup> |                                                                                                                                                                                                         |         |      |       |            |  |  |

| F21                | LPRC                            | -15                                                                                                                                                                                                     | _       | +15  | %     | _          |  |  |

Note 1: Change of LPRC frequency as VDD changes.

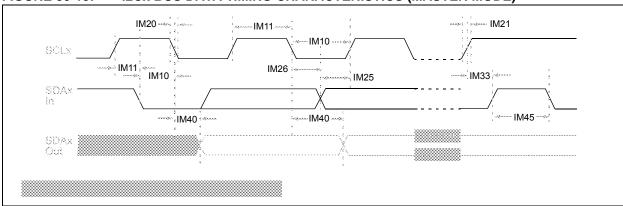

#### FIGURE 30-14: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

#### FIGURE 30-15: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

TABLE 30-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                      | Standard Operating Conditions (see Note 4): 2.5V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |         |       |                                                           |

|--------------------|-----------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|-------|-----------------------------------------------------------|

| Param.<br>No.      | Symbol    | Characteristics                                                      | Min.                                                                                                                                                                                                                                                         | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                |

| Clock P            | arameter  | S                                                                    |                                                                                                                                                                                                                                                              |                        |         |       |                                                           |

| AD50               | TAD       | ADC Clock Period <sup>(2)</sup>                                      | 65                                                                                                                                                                                                                                                           | _                      | _       | ns    | See Table 30-35                                           |

| Convers            | sion Rate |                                                                      |                                                                                                                                                                                                                                                              |                        |         |       |                                                           |

| AD55               | TCONV     | Conversion Time                                                      | _                                                                                                                                                                                                                                                            | 12 TAD                 | _       | _     | _                                                         |

| AD56               | FCNV      | Throughput Rate                                                      | _                                                                                                                                                                                                                                                            | _                      | 1000    | ksps  | AVDD = 3.0V to 3.6V                                       |

|                    |           | (Sampling Speed)                                                     | _                                                                                                                                                                                                                                                            | _                      | 400     | ksps  | AVDD = 2.5V to 3.6V                                       |

| AD57               | TSAMP     | Sample Time                                                          | 1 TAD                                                                                                                                                                                                                                                        | _                      | _       | _     | Tsamp must be ≥ 132 ns                                    |

| Timing             | Paramete  | rs                                                                   |                                                                                                                                                                                                                                                              |                        |         |       |                                                           |

| AD60               | TPCS      | Conversion Start from Sample Trigger <sup>(3)</sup>                  | _                                                                                                                                                                                                                                                            | 1.0 TAD                | 1       | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |

| AD61               | TPSS      | Sample Start from Setting Sample (SAMP) bit                          | 0.5 TAD                                                                                                                                                                                                                                                      | _                      | 1.5 TAD | _     | _                                                         |

| AD62               | TCSS      | Conversion Completion to Sample Start (ASAM = $1$ ) <sup>(3)</sup>   | _                                                                                                                                                                                                                                                            | 0.5 TAD                | _       | _     | _                                                         |

| AD63               | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _                                                                                                                                                                                                                                                            | _                      | 2       | μS    | _                                                         |

Note 1: These parameters are characterized, but not tested in manufacturing.

**<sup>2:</sup>** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**<sup>3:</sup>** Characterized by design but not tested.

**<sup>4:</sup>** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

#### TABLE 30-39: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |       |      |       |            |

|--------------------|---------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                      | Min.                                                                                                                                                                                                                                              | Тур.  | Max. | Units | Conditions |

| PM11               | Twr     | PMWR Pulse Width                                                    | _                                                                                                                                                                                                                                                 | 1 Трв | _    | _     | _          |

| PM12               | TDVSU   | Data Out Valid before PMWR or PMENB goes Inactive (data setup time) | _                                                                                                                                                                                                                                                 | 2 TPB | _    | _     | _          |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data Out Invalid (data hold time)          | _                                                                                                                                                                                                                                                 | 1 Трв |      | _     | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

#### **TABLE 30-40: OTG ELECTRICAL SPECIFICATIONS**

| IABLE              | TABLE 30-40: OTG ELECTRICAL SPECIFICATIONS |                                   |                                                                                                                                                                                                                                                |      |      |       |                                                                                   |

|--------------------|--------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|

| AC CHARACTERISTICS |                                            |                                   | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |      |      |       |                                                                                   |

| Param.<br>No.      | Symbol                                     | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions                                                                        |

| USB313             | VUSB3V3                                    | USB Voltage                       | 3.0                                                                                                                                                                                                                                            | _    | 3.6  | V     | Voltage on Vusb3v3<br>must be in this range<br>for proper USB<br>operation        |

| USB315             | VILUSB                                     | Input Low Voltage for USB Buffer  | _                                                                                                                                                                                                                                              | _    | 0.8  | V     | _                                                                                 |

| USB316             | VIHUSB                                     | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                            | _    | _    | V     | _                                                                                 |

| USB318             | VDIFS                                      | Differential Input Sensitivity    | _                                                                                                                                                                                                                                              |      | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |

| USB319             | VCM                                        | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                            | _    | 2.5  | V     | _                                                                                 |

| USB320             | Zout                                       | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                           | _    | 44.0 | Ω     | _                                                                                 |

| USB321             | Vol                                        | Voltage Output Low                | 0.0                                                                                                                                                                                                                                            | _    | 0.3  | V     | 1.425 kΩ load connected to Vusb3v3                                                |

| USB322             | Vон                                        | Voltage Output High               | 2.8                                                                                                                                                                                                                                            | _    | 3.6  | V     | 1.425 kΩ load connected to ground                                                 |