Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 33                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f256dt-v-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

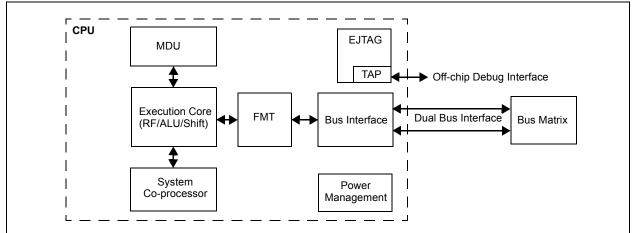

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

## 3.1 Features

- 5-stage pipeline

- 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

## FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

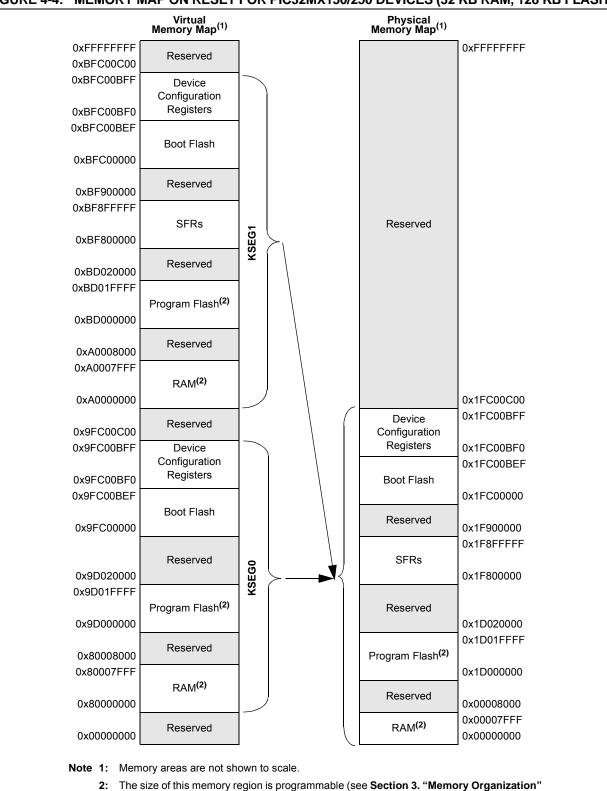

## FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX150/250 DEVICES (32 KB RAM, 128 KB FLASH)

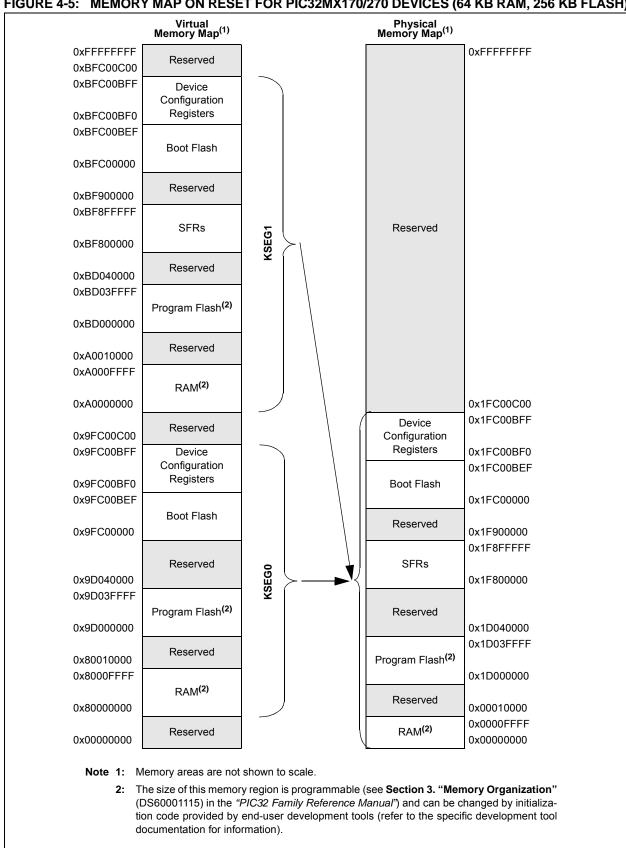

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*") and can be changed by initialization code provided by end-user development tools (refer to the specific development tool documentation for information).

#### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDK             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |

### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

# Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | —                 | _                 | -                 | _                 | —                 |                  | _                |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | BMXDUPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

## REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | —                 | -                | —                    |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 10.0         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                    |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |

| 7:0          | —                 | —                 | _                 | —                 | _                 | —                 | —                | SWRST <sup>(1)</sup> |  |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:         HC = Cleared by hardware |                  |                           |                    |  |

|------------------------------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit                         | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR                        | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable Software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit is written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |

|       | available from the Documentation >                                                                                                                                                                              |

|       | Reference Manual section of the                                                                                                                                                                                 |

|       | Microchip PIC32 web site                                                                                                                                                                                        |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | _                | —                |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 |                   |                   |                   |                   | _                | _                |

## **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

NOTES:

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                          | —                 | —                 | _                 | —                 | —                 | —                | -                |  |

| 00.40        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                          | —                 | —                 | _                 | —                 | —                 | _                | -                |  |

| 45.0         | R/W-0                      | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | 15:8 ADRC — — SAMC<4:0>(1) |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W              | R/W-0            |  |

| 7:0          |                            |                   |                   | ADCS<             | 7:0> <b>(2)</b>   |                   |                  |                  |  |

## Legend:

| =ogona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- **2:** This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

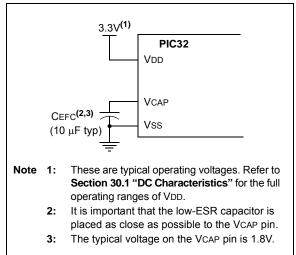

## 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

## 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

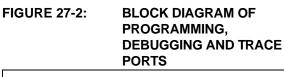

## 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

NOTES:

## TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |       |            |  |

|--------------------|-----------|------------------------------------------------------------------|-------------------------------------------------------|------|-------|-------|------------|--|

| Param.<br>No.      | Symbol    | Characteristics                                                  | Min.                                                  | Тур. | Max.  | Units | Conditions |  |

| Operati            | ng Voltag | e                                                                |                                                       |      |       |       |            |  |

| DC10               | Vdd       | Supply Voltage (Note 2)                                          | 2.3                                                   |      | 3.6   | V     | —          |  |

| DC12               | Vdr       | RAM Data Retention Voltage<br>(Note 1)                           | 1.75                                                  | _    | —     | V     | _          |  |

| DC16               | VPOR      | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                  | —    | 2.1   | V     | _          |  |

| DC17               | SVDD      | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005                                               | _    | 0.115 | V/μs  | _          |  |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

### TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS                     |                               | $\begin{array}{ll} \mbox{Standard Operating Conditions: } 2.3V \ to \ 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ for \ Industrial \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \ for \ V-temp \end{array}$ |      |       |                                |  |

|---------------|---------|----------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|

| Param.<br>No. | Symbol  | Charact                    | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                               | Max. | Units | Conditions                     |  |

| IM10          | TLO:SCL | Clock Low Time             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μs    | —                              |  |

|               |         |                            | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | —                              |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | —    | μs    | _                              |  |

| IM11          | THI:SCL | Clock High Time            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | —                              |  |

|               |         |                            | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS    | —                              |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μs    | -                              |  |

| IM20          | TF:SCL  | SDAx and SCLx              | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                 | 300  | ns    | CB is specified to be          |  |

|               |         | Fall Time                  | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | from 10 to 400 pF              |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                 | 100  | ns    |                                |  |

| IM21          | TR:SCL  | SDAx and SCLx<br>Rise Time | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                 | 1000 | ns    | CB is specified to be          |  |

|               |         |                            | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | from 10 to 400 pF              |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                 | 300  | ns    |                                |  |

| IM25          | TSU:DAT | Data Input<br>Setup Time   | 100 kHz mode                  | 250                                                                                                                                                                                                                                                                               |      | ns    | —                              |  |

|               |         |                            | 400 kHz mode                  | 100                                                                                                                                                                                                                                                                               | _    | ns    |                                |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                                                                               |      | ns    |                                |  |

| IM26          | THD:DAT | Data Input                 | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                 |      | μS    | —                              |  |

|               |         | Hold Time                  | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                 | 0.9  | μS    |                                |  |

|               |         |                            | 1 MHz mode<br>(Note 2)        | 0                                                                                                                                                                                                                                                                                 | 0.3  | μS    |                                |  |

| IM30          | TSU:STA |                            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | Only relevant for              |  |

|               |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS    | Repeated Start condition       |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS    | condition                      |  |

| IM31          | THD:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | After this period, the         |  |

|               |         | Hold Time                  | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | -    | μS    | first clock pulse is generated |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | generaleu                      |  |

| IM33          | Tsu:sto | Stop Condition             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS    |                                |  |

|               |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    |                                |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | —    | μs    |                                |  |

| IM34          | THD:STO | Stop Condition             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | ns    | —                              |  |

|               |         | Hold Time                  | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | ns    |                                |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | ns    |                                |  |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

| AC CHA        | RACTERIS     | STICS                        |                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industr} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temperature} \\ \end{array}$ |      |       |                                            |  |

|---------------|--------------|------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|

| Param.<br>No. | Symbol Chara |                              | eristics               | Min.                                                                                                                                                                                                                                                                                       | Max. | Units | Conditions                                 |  |

| IS10          | TLO:SCL      | Clock Low Time               | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                                                        | —    | μS    | PBCLK must operate at a minimum of 800 kHz |  |

|               |              |                              | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                                                        | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                                                        | _    | μS    | _                                          |  |

| IS11          | THI:SCL      | Clock High Time              | 100 kHz mode           | 4.0                                                                                                                                                                                                                                                                                        | _    | μS    | PBCLK must operate at a minimum of 800 kHz |  |

|               |              |                              | 400 kHz mode           | 0.6                                                                                                                                                                                                                                                                                        | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                                                        | _    | μS    |                                            |  |

| IS20          | TF:SCL       | SDAx and SCLx                | 100 kHz mode           | —                                                                                                                                                                                                                                                                                          | 300  | ns    | CB is specified to be from                 |  |

|               |              | Fall Time                    | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                                                                                                                | 300  | ns    | 10 to 400 pF                               |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | _                                                                                                                                                                                                                                                                                          | 100  | ns    |                                            |  |

| IS21          | TR:SCL       | L SDAx and SCLx<br>Rise Time | 100 kHz mode           |                                                                                                                                                                                                                                                                                            | 1000 | ns    | CB is specified to be from                 |  |

|               |              |                              | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                                                                                                                | 300  | ns    | 10 to 400 pF                               |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | —                                                                                                                                                                                                                                                                                          | 300  | ns    |                                            |  |

| IS25          | TSU:DAT      | Data Input                   | 100 kHz mode           | 250                                                                                                                                                                                                                                                                                        | —    | ns    | _                                          |  |

|               |              | Setup Time                   | 400 kHz mode           | 100                                                                                                                                                                                                                                                                                        | —    | ns    |                                            |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 100                                                                                                                                                                                                                                                                                        | —    | ns    |                                            |  |

| IS26          | THD:DAT      | Data Input                   | 100 kHz mode           | 0                                                                                                                                                                                                                                                                                          | —    | ns    |                                            |  |

|               |              | Hold Time                    | 400 kHz mode           | 0                                                                                                                                                                                                                                                                                          | 0.9  | μs    |                                            |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 0                                                                                                                                                                                                                                                                                          | 0.3  | μS    |                                            |  |

| IS30          | TSU:STA      |                              | 100 kHz mode           | 4700                                                                                                                                                                                                                                                                                       | —    | ns    | Only relevant for Repeated                 |  |

|               |              | Setup Time                   | 400 kHz mode           | 600                                                                                                                                                                                                                                                                                        | —    | ns    | Start condition                            |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                                                                                                                        | —    | ns    |                                            |  |

| IS31          | THD:STA      | Start Condition              | 100 kHz mode           | 4000                                                                                                                                                                                                                                                                                       | —    | ns    | After this period, the first               |  |

|               |              | Hold Time                    | 400 kHz mode           | 600                                                                                                                                                                                                                                                                                        | —    | ns    | clock pulse is generated                   |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                                                                                                                        | —    | ns    |                                            |  |

| IS33          | Tsu:sto      | Stop Condition               | 100 kHz mode           | 4000                                                                                                                                                                                                                                                                                       |      | ns    |                                            |  |

|               |              | Setup Time                   | 400 kHz mode           | 600                                                                                                                                                                                                                                                                                        |      | ns    | ]                                          |  |

|               |              |                              | 1 MHz mode<br>(Note 1) | 600                                                                                                                                                                                                                                                                                        |      | ns    |                                            |  |

### TABLE 30-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

### TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS  |                       |                                                    | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |       |      |       |                                  |

|---------------------|-----------------------|----------------------------------------------------|----------------------------------------------------------|-------|------|-------|----------------------------------|

| Param<br>No.        | Symbol Characteristic |                                                    | Min.                                                     | Тур.  | Max. | Units | Conditions                       |

| CTMU CURRENT SOURCE |                       |                                                    |                                                          |       |      |       |                                  |

| CTMUI1              | Ιουτ1                 | Base Range <sup>(1)</sup>                          | _                                                        | 0.55  | _    | μA    | CTMUCON<9:8> = 01                |

| CTMUI2              | Ιουτ2                 | 10x Range <sup>(1)</sup>                           | _                                                        | 5.5   | _    | μA    | CTMUCON<9:8> = 10                |

| CTMUI3              | Ιουτ3                 | 100x Range <sup>(1)</sup>                          | _                                                        | 55    |      | μA    | CTMUCON<9:8> = 11                |

| CTMUI4              | IOUT4                 | 1000x Range <sup>(1)</sup>                         | _                                                        | 550   |      | μA    | CTMUCON<9:8> = 00                |

| CTMUFV1             | VF                    | Temperature Diode Forward Voltage <sup>(1,2)</sup> | —                                                        | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |

|                     |                       |                                                    | _                                                        | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |

|                     |                       |                                                    | —                                                        | 0.721 |      | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |

| CTMUFV2             | VFVR                  | Temperature Diode Rate of                          | —                                                        | -1.92 | _    | mV/ºC | CTMUCON<9:8> = 01                |

|                     |                       | Change <sup>(1,2)</sup>                            | _                                                        | -1.74 |      | mV/ºC | CTMUCON<9:8> = 10                |

|                     |                       |                                                    | _                                                        | -1.56 |      | mV/ºC | CTMUCON<9:8> = 11                |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

**2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

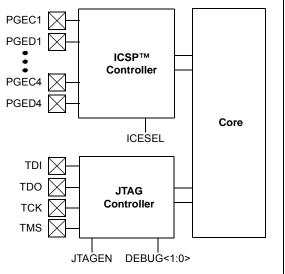

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       |          |       |  |  |

|----------------------------|----------|-------|----------|-------|--|--|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |  |  |

| Number of Pins             | Ν        |       | 28       |       |  |  |

| Pitch                      | е        |       | .100 BSC |       |  |  |

| Top to Seating Plane       | Α        | -     | -        | .200  |  |  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |  |  |

| Base to Seating Plane      | A1       | .015  | -        | -     |  |  |

| Shoulder to Shoulder Width | E        | .290  | .310     | .335  |  |  |

| Molded Package Width       | E1       | .240  | .285     | .295  |  |  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |  |  |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |  |  |

| Lead Thickness             | С        | .008  | .010     | .015  |  |  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |  |  |

| Lower Lead Width           | b        | .014  | .018     | .022  |  |  |

| Overall Row Spacing §      | eВ       | -     | -        | .430  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

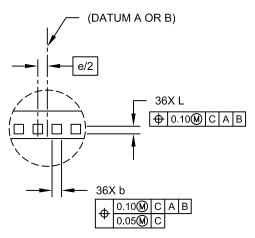

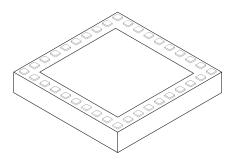

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |               |      |       |  |

|-------------------------|-------------|---------------|------|-------|--|

| Dimensior               | Limits      | MIN           | NOM  | MAX   |  |

| Number of Pins          | Ν           |               | 36   |       |  |

| Number of Pins per Side | ND          |               | 10   |       |  |

| Number of Pins per Side | NE          |               | 8    |       |  |

| Pitch                   | е           | 0.50 BSC      |      |       |  |

| Overall Height          | А           | 0.80 0.90 1.0 |      |       |  |

| Standoff                | A1 0.025    |               |      | 0.075 |  |

| Overall Width           | Е           | 5.00 BSC      |      |       |  |

| Exposed Pad Width       | E2          | 3.60 3.75 3.9 |      |       |  |

| Overall Length          | D           | 5.00 BSC      |      |       |  |

| Exposed Pad Length      | D2          | 2 3.60 3.75   |      |       |  |

| Contact Width           | b           | 0.20          | 0.25 | 0.30  |  |

| Contact Length          | L           | 0.20          | 0.25 | 0.30  |  |

| Contact-to-Exposed Pad  | K           | 0.20          | -    | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-187C Sheet 2 of 2