# E. Renesas Electronics America Inc - UPD70F3782GF-GAT-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 50MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, Ethernet, I <sup>2</sup> C, UART/USART, USB                            |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 84                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                |                                                                                      |

| RAM Size                   | 124K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 10x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 128-LQFP                                                                             |

| Supplier Device Package    |                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3782gf-gat-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### (a) Function as compare register

The TABnCCR1 register can be rewritten even when the TABnCTL0.TABnCE bit = 1.

The set value of the TABnCCR1 register is transferred to the CCR1 buffer register. When the value of the 16bit counter matches the value of the CCR1 buffer register, a compare match interrupt request signal (INTTABnCC1) is generated. If TOABn1 pin output is enabled at this time, the output of the TOABn1 pin is inverted.

#### (b) Function as capture register

When the TABnCCR1 register is used as a capture register in the free-running timer mode, the count value of the 16-bit counter is stored in the TABnCCR1 register if the valid edge of the capture trigger input pin (TIABn1 pin) is detected. In the pulse width measurement mode, the count value of the 16-bit counter is stored in the TABnCCR1 register and the 16-bit counter is cleared (0000H) if the valid edge of the capture trigger input pin (TIABn1 pin) is detected.

Even if the capture operation and reading the TABnCCR1 register conflict, the correct value of the TABnCCR1 register can be read.

**Remark** n = 0, 1

The following table shows the functions of the capture/compare register in each mode, and how to write data to the compare register.

| Operation Mode                | Capture/Compare Register | How to Write Compare Register |

|-------------------------------|--------------------------|-------------------------------|

| Interval timer                | Compare register         | Anytime write                 |

| External event counter        | Compare register         | Anytime write                 |

| External trigger pulse output | Compare register         | Batch write                   |

| One-shot pulse output         | Compare register         | Anytime write                 |

| PWM output                    | Compare register         | Batch write                   |

| Free-running timer            | Capture/compare register | Anytime write                 |

| Pulse width measurement       | Capture register         | _                             |

| Triangular wave PWM mode      | Compare register         | Batch write                   |

| Table 8-3 | Function of C | anture/Compare | Register in  | Fach Mode and  | d How to Write | Compare Register |

|-----------|---------------|----------------|--------------|----------------|----------------|------------------|

|           |               | aptule/compare | inegister in | Lacii woue and |                | oompare negister |

## 10.4.2 Cautions

(1) It takes the 16-bit counter up to the following time to start counting after the TMnCTL0.TMnCE bit is set to 1, depending on the count clock selected.

| (n | = 0)                 |                                    |

|----|----------------------|------------------------------------|

|    | Selected Count Clock | Maximum Time Before Counting Start |

|    | fxx                  | 2/fxx                              |

|    | fxx/2                | 3/fxx                              |

|    | fxx/4                | 6/fxx                              |

|    | fxx/64               | 128/fxx                            |

|    | fxx/512              | 1024/fxx                           |

|    | fxx/1024             | 2048/fxx                           |

|    | fr/8                 | 16/f <sub>R</sub>                  |

|    | fхт                  | 2/fxt                              |

#### (n = 1 to 3)

| Selected Count Clock | Maximum Time Before Counting Start |

|----------------------|------------------------------------|

| fxx/2                | 4/fxx                              |

| fxx/4                | 6/fxx                              |

| fxx/8                | 12/fxx                             |

| fxx16                | 32/fxx                             |

| fxx/64               | 128/fxx                            |

| fxx/256              | 512/fxx                            |

| fxx/512              | 1024/fxx                           |

| fxx/1024             | 2048/fxx                           |

(2) Rewriting the TMnCMP0 and TMnCTL0 registers is prohibited while TMMn is operating. If these registers are rewritten while the TMnCE bit is 1, the operation cannot be guaranteed. If they are rewritten by mistake, clear the TMnCTL0.TMnCE bit to 0, and re-set the registers.

**Remark** n = 0 to 3

### 11.2 Configuration

The motor control function consists of the following hardware.

| Item              | Configuration                                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer register    | Dead-time counters                                                                                                                                                                                                             |

| Compare register  | TAB1 dead-time compare register (TAB1DTC register)                                                                                                                                                                             |

| Control registers | TAB1 option register 1 (TAB1OPT1)<br>TAB1 option register 2 (TAB1OPT2)<br>TAB1 I/O control register 3 (TAB1IOC3)<br>High-impedance output control register 0 (HZA0CTL0)<br>High-impedance output control register 1 (HZA0CTL1) |

- 6-phase PWM output can be produced with dead time by using the output of TAB1 (TOAB11, TOAB12, TOAB13).

- The output level of the 6-phase PWM output can be set individually.

- The 16-bit timer/counter of TAB1 counts up/down triangular waves. When the timer/counter underflows and when a cycle match occurs, an interrupt is generated. Interrupt generation, however, can be suppressed up to 31 times.

- TAA4 can execute counting at the same time as TAB1 (timer tuning operation function). TAA4 can be set in three ways as it can generate an A/D trigger source (TABTADT0) and two types of interrupts: a TAB1 underflow interrupt (INTTAB1OV) and a cycle match interrupt (INTTAB1CC0).

#### (4) Real-time counter control register 3 (RC1CC3)

The RC1CC3 register is an 8-bit register that controls the interval interrupt function and RTCDIV pin. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

|               | 7                      | 6                                                   | 5                                     | 4                        | 3                     | 2                          | 1          | 0           |          |  |  |

|---------------|------------------------|-----------------------------------------------------|---------------------------------------|--------------------------|-----------------------|----------------------------|------------|-------------|----------|--|--|

| RC1CC3        | RINTE                  | CLOE2                                               | CKDIV                                 | 0                        | 0                     | ICT2                       | ICT1       | ICT0        |          |  |  |

|               |                        |                                                     |                                       |                          |                       |                            |            |             |          |  |  |

|               | RINTE                  |                                                     | h                                     | nterval inte             | rrupt (INTF           | RTC2) contr                | ol         |             |          |  |  |

|               | 0                      | Does not g                                          | Does not generate interval interrupt. |                          |                       |                            |            |             |          |  |  |

|               | 1                      |                                                     |                                       |                          |                       |                            |            |             |          |  |  |

|               | CLOE2                  |                                                     |                                       |                          |                       |                            |            |             |          |  |  |

|               | 0                      | Disables F                                          | Disables RTCDIV pin output.           |                          |                       |                            |            |             |          |  |  |

|               | 1                      | Enables R                                           | TCDIV pir                             | output.                  |                       |                            |            |             |          |  |  |

|               | CKDIV0                 |                                                     | RT                                    | CDIV pin o               | utput frequ           | iency select               | tion       |             |          |  |  |

|               | 1                      | Outputs 5                                           | 12 Hz (1.9                            | 5 ms) from               | RTCDIV p              | oin.                       |            |             |          |  |  |

|               |                        | Outputs 1                                           | 6.384 kHz                             | (0.061 ms)               | from RTC              | DIV pin.                   |            |             |          |  |  |

|               |                        |                                                     |                                       |                          |                       |                            |            |             |          |  |  |

|               | ICT2                   | ICT1                                                | ICT0                                  | Ir                       | terval inte           | rrupt (INTR                | TC2) selec | tion        |          |  |  |

|               | 0                      | 0                                                   | 0                                     | 2 <sup>6</sup> /fхт (1.  | 953125 m              | s)                         |            |             |          |  |  |

|               | 0                      | 0                                                   | 1                                     | 2 <sup>7</sup> /fxt (3.  | 90625 ms              | )                          |            |             |          |  |  |

|               | 0                      | 1                                                   | 0                                     | 2 <sup>8</sup> /fxт (7.  | 8125 ms)              |                            |            |             |          |  |  |

|               | 0                      | 1                                                   | 1                                     | 2 <sup>9</sup> /fхт (18  | 5.625 ms)             |                            |            |             |          |  |  |

|               | 1                      | 0                                                   | 0                                     | 2 <sup>10</sup> /fx⊤ (3  | 1.25 ms)              |                            |            |             |          |  |  |

|               | 1                      | 0                                                   | 1                                     | 2 <sup>11</sup> /fx⊤ (6  | 2.5 ms)               |                            |            |             |          |  |  |

|               | 1                      | 1                                                   | ×                                     | 2 <sup>12</sup> /fxt (1  | 25 ms)                |                            |            |             |          |  |  |

| <b>2.</b> The | ting the R<br>RTCDIV o | anging IN<br>INTE bit du<br>utput oper<br>ed from 0 | uring real<br>ates as fo              | -time cour<br>ollows whe | nter operation the CL | ation (RC1<br>OE2 bit se   | PWR bit =  | = 1).       |          |  |  |

|               | -                      |                                                     | (2                                    | × 32.768                 | kHz).                 |                            |            |             |          |  |  |

| • Wi          | nen chang              | ed from 1                                           |                                       | -                        |                       | 0IV output<br>el, 2 × 32.7 |            | ed after tw | vo clock |  |  |

| UBnRT3                      | UBnRT2   | UBnRT1     | UBnRT0   | Number of data of<br>transmit FIFO set as trigger | Pointer mode     | Pending mode |

|-----------------------------|----------|------------|----------|---------------------------------------------------|------------------|--------------|

| 0                           | 0        | 0          | 0        | 1 byte                                            | Settable         | Settable     |

| 0                           | 0        | 0          | 1        | 2 bytes                                           | Setting          |              |

| 0                           | 0        | 1          | 0        | 3 bytes                                           | prohibited       |              |

| 0                           | 0        | 1          | 1        | 4 bytes                                           |                  |              |

| 0                           | 1        | 0          | 0        | 5 bytes                                           | _                |              |

| 0                           | 1        | 0          | 1        | 6 bytes                                           |                  |              |

| 0                           | 1        | 1          | 0        | 7 bytes                                           |                  |              |

| 0                           | 1        | 1          | 1        | 8 bytes                                           |                  |              |

| 1                           | 0        | 0          | 0        | 9 bytes                                           |                  |              |

| 1                           | 0        | 0          | 1        | 10 bytes                                          |                  |              |

| 1                           | 0        | 1          | 0        | 11 bytes                                          |                  |              |

| 1                           | 0        | 1          | 1        | 12 bytes                                          |                  |              |

| 1                           | 1        | 0          | 0        | 13 bytes                                          |                  |              |

| 1                           | 1        | 0          | 1        | 14 bytes                                          |                  |              |

| 1                           | 1        | 1          | 0        | 15 bytes                                          |                  |              |

| 1                           | 1        | 1          | 1        | 16 bytes                                          |                  |              |

| <ul> <li>Set the</li> </ul> | ne numb  | er of rec  | eive FIF | O receive data to be                              | he trigger.      |              |

| <ul> <li>Each</li> </ul>    | time dat | a of the   | specifie | d number has been s                               | ored from the re | eceive shift |

| -                           |          |            |          | NTUBnTIR interrupt is                             | -                |              |

|                             |          | -          |          | 0.UBnIRM bit = 0), th                             |                  | gnal is      |

| -                           |          |            |          | s of the pending mod                              |                  |              |

|                             |          |            |          | 0.0BnIRM bit = 1), the                            |                  |              |

|                             |          |            | -        | (UBnRT3 to UBnRT0<br>other than 1 byte is ma      |                  | -            |

|                             | inteed.  | i. II a Se |          |                                                   | aue, me operatio |              |

#### (5) CSIEn status register (CEnSTR)

These registers indicate the status of the CSIBUFn register or the transfer status.

These registers can be read or written in 8-bit or 1-bit units (however, bits 6 to 0 can only be read. They do not change even if they are written).

Reset sets this register to 20H.

In addition to reset input, the CEnSTR register can be initialized by clearing (0) the CEnCTL0.CEnPWR bit.

## Cautions 1. Accessing the CEnSTR register is prohibited in the following statuses. For details, refer to 3.4.9 (2) Accessing specific on-chip peripheral I/O registers.

- When the CPU operates with the subclock and the main clock oscillation is stopped

- When the CPU operates with the internal oscillation clock

- 2. Because the values of the CEnFLF, CEnEMP, CEnTSF, CEnSFP3 to CEnSFP0 bits may change at any time during transfer, their values during transfer may differ from the actual values. Especially, use the CEnTSF bit independently (do not use this bit in relation with the other bits). To detect the end of transfer by the CEnSTR register, check to see if the CEnEMF bit is 1 after the data to be transferred has been written to the CSIBUFn register.

### (3) When arbitration loss occurs during data transfer

| ST                   | AD6 to AD0                                                                                              | R/W                                                                                             | ACK                                                    | D7 to D0                                     | ACK       | D7 to D0               | ĀCK        | SP      |         |

|----------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------|-----------|------------------------|------------|---------|---------|

|                      |                                                                                                         |                                                                                                 |                                                        | <b>1</b>                                     | ▲2        |                        |            | -       | Δ3      |

| ▲1                   | : IICSn register                                                                                        | = 1000                                                                                          | 1110B                                                  |                                              |           |                        |            |         |         |

| ▲2                   | : IICSn register                                                                                        | = 0100                                                                                          | 0000B (I                                               | Example: Whe                                 | en ALDn   | bit is read duri       | ing interr | upt ser | vicing) |

| Δ3                   | : IICSn register                                                                                        | = 0000                                                                                          | 0001B                                                  |                                              |           |                        |            |         |         |

|                      |                                                                                                         |                                                                                                 |                                                        |                                              |           |                        |            |         |         |

| R                    | emarks 1. 🔺                                                                                             |                                                                                                 |                                                        |                                              |           |                        |            |         |         |

|                      |                                                                                                         |                                                                                                 |                                                        | only when S                                  | PIEn bit  | t = 1                  |            |         |         |

|                      | 2. n                                                                                                    | = 0 to                                                                                          | 3 (V850                                                | )ES/JH3-E)                                   |           |                        |            |         |         |

|                      |                                                                                                         | <u>.</u>                                                                                        | 4 /1/050                                               | -                                            |           |                        |            |         |         |

|                      | n                                                                                                       | = 0 to                                                                                          | 4 (V850                                                | )ES/JJ3-E)                                   |           |                        |            |         |         |

| . Wh                 |                                                                                                         |                                                                                                 | 4 (V850                                                | -                                            |           |                        |            |         |         |

| Wh                   | n<br><b>en WTIMn bi</b>                                                                                 |                                                                                                 | 4 (V850                                                | -                                            |           |                        |            |         |         |

| Wh                   |                                                                                                         |                                                                                                 | 4 (V850<br>ĀCK                                         | -                                            | ĀCK       | D7 to D0               | ĀCK        | SP      | 1       |

|                      | en WTIMn bi                                                                                             | t = 1                                                                                           | ĀCK                                                    | )ES/JJ3-E)                                   |           | D7 to D0               | ĀCK        | SP      | ]<br>3  |

| ST                   | en WTIMn bi                                                                                             | t = 1<br>R/W                                                                                    | ĀCK                                                    | DES/JJ3-E)<br>D7 to D0                       |           |                        | ĀCK        | SP      | ]<br>3  |

| ST<br>▲1             | en WTIMn bi                                                                                             | t = 1<br>R/W                                                                                    | <u>АСК</u><br>1110В                                    | DES/JJ3-E)<br>D7 to D0                       |           | 2                      | <u> </u>   | _       | -       |

| ST<br>▲1<br>▲2       | en WTIMn bi<br>AD6 to AD0<br>: IICSn register                                                           | t = 1<br>R/W<br>= 1000<br>r = 0100                                                              | ACK<br>1110B<br>0100B (I                               | DES/JJ3-E)<br>D7 to D0                       |           | 2                      | <u> </u>   | _       | -       |

| ST<br>▲1<br>▲2       | en WTIMn bi<br>AD6 to AD0<br>: IICSn register                                                           | t = 1<br>R/W<br>= 1000<br>r = 0100                                                              | ACK<br>1110B<br>0100B (I                               | DES/JJ3-E)<br>D7 to D0                       |           | 2                      | <u> </u>   | _       | -       |

| ST<br>▲1<br>▲2<br>∆3 | en WTIMn bi<br>AD6 to AD0<br>: IICSn register                                                           | <b>r</b> = <b>1</b><br><b>R</b> / <del>W</del><br><b>r</b> = 1000<br><b>r</b> = 0100<br>= 00000 | ACK<br>1110B<br>0100B (F<br>0001B                      | DES/JJ3-E)<br>D7 to D0<br>▲1<br>Example: Whe |           | 2                      | <u> </u>   | _       | -       |

| ST<br>▲1<br>▲2<br>∆3 | en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register                   | t = 1<br>R/W<br>= 1000<br>= 0100<br>= 00000                                                     | ACK<br>1110B<br>0100B (I<br>0001B<br>ays gen           | DES/JJ3-E)<br>D7 to D0<br>▲1<br>Example: Whe | en ALDn I | 12<br>bit is read duri | <u> </u>   | _       | -       |

| ST<br>▲1<br>▲2<br>∆3 | en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register<br>: Remarks 1. ▲ | t = 1<br>R/W<br>= 1000<br>= 0100<br>= 00000<br>a: Alwa<br>: Gen                                 | ACK<br>1110B<br>0100B (R<br>0001B<br>ays gen<br>erated | DES/JJ3-E)                                   | en ALDn I | 12<br>bit is read duri | <u> </u>   | _       | -       |

#### 20.14.2 When communication reservation function is disabled (IICFn.IICRSVn bit = 1)

When the IICCn.STTn bit is set when the bus is not being used for communication during bus communication, this request is rejected and a start condition is not generated. There are two modes in which the bus is not used.

- When arbitration results in neither master nor slave operation

- When an extension code is received and slave operation is disabled (ACK is not returned and the bus was released when the IICCn.LRELn bit was set to 1) (n = 0 to 2)

To confirm whether the start condition was generated or the request was rejected, check the IICFn.STCFn flag. The time shown in Table 20-7 is required until the STCFn flag is set after setting the STTn bit to 1. Therefore, secure the time by software.

| OCKSENm | OCKSm1 | OCKSm0 | CLn1 | CLn0 | Wait Period |

|---------|--------|--------|------|------|-------------|

| 1       | 0      | 0      | 0    | ×    | 20 clocks   |

| 1       | 0      | 1      | 0    | ×    | 30 clocks   |

| 1       | 1      | 0      | 0    | ×    | 40 clocks   |

| 1       | 1      | 1      | 0    | ×    | 50 clocks   |

| 0       | 0      | 0      | 1    | 0    | 10 clocks   |

#### Table 20-7. Wait Periods

Remarks 1. X: don't care

2. n = 0 to 3 (V850ES/JH3-E)

n = 0 to 4 (V850ES/JJ3-E)

m = 0 to 2

#### (17) CAN0 module transmit history list register (C0TGPT)

The C0TGPT register is used to read the transmit history list.

| After reset: xx02                     | H R/W                                                                                                                                                                                                                                                                                                               | Address                                                                                                                                                | : 03FEC06                                                                                                                         | 4H                                                                                                    |                                                                                                                 |                                                                                             |                                                                               |                                               |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|--|--|

| (a) Read                              | 15                                                                                                                                                                                                                                                                                                                  | 14                                                                                                                                                     | 13                                                                                                                                | 12                                                                                                    | 11                                                                                                              | 10                                                                                          | 9                                                                             | 8                                             |  |  |

| СОТСРТ                                | TGPT7                                                                                                                                                                                                                                                                                                               | TGPT6                                                                                                                                                  | TGPT5                                                                                                                             | TGPT4                                                                                                 | TGPT3                                                                                                           | TGPT2                                                                                       | J<br>TGPT1                                                                    | TGPT0                                         |  |  |

| L                                     | 7                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                      | 5                                                                                                                                 | 4                                                                                                     | 3                                                                                                               | 2                                                                                           | 1                                                                             | 0                                             |  |  |

|                                       | 0                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                      | 0                                                                                                                                 | 0                                                                                                     | 0                                                                                                               | 0                                                                                           | THPM                                                                          | TOVF                                          |  |  |

| (b) Write                             |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |                                                                                                                                   |                                                                                                       |                                                                                                                 |                                                                                             |                                                                               |                                               |  |  |

|                                       | 15                                                                                                                                                                                                                                                                                                                  | 14                                                                                                                                                     | 13                                                                                                                                | 12                                                                                                    | 11                                                                                                              | 10                                                                                          | 9                                                                             | 8                                             |  |  |

| COTGPT                                | 0                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                      | 0                                                                                                                                 | 0                                                                                                     | 0                                                                                                               | 0                                                                                           | 0                                                                             | 0                                             |  |  |

| _                                     | 7                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                      | 5                                                                                                                                 | 4                                                                                                     | 3                                                                                                               | 2                                                                                           | 1                                                                             | 0                                             |  |  |

|                                       | 0                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                      | 0                                                                                                                                 | 0                                                                                                     | 0                                                                                                               | 0                                                                                           | 0                                                                             | Clear<br>TOVF                                 |  |  |

| THPM <sup>Note 1</sup><br>0           |                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                      | ist has at lea                                                                                                                    | Transmit histo<br>st one messa                                                                        | ge buffer nur                                                                                                   | nber that has                                                                               |                                                                               | ıd.                                           |  |  |

| 1                                     | The tran                                                                                                                                                                                                                                                                                                            | smit history li                                                                                                                                        | st has no me                                                                                                                      | essage buffer                                                                                         | numbers tha                                                                                                     | t have not be                                                                               | en read.                                                                      |                                               |  |  |

|                                       |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        | 1                                                                                                                                 | Fransmit histo                                                                                        | ry list overflo                                                                                                 | w bit                                                                                       |                                                                               |                                               |  |  |

| TOVF <sup>Note 2</sup>                | Transmit history list overflow bit<br>All the message buffer numbers that have not been read are preserved. All the numbers of the<br>message buffers to which a new data frame or remote frame has been transmitted are recorded<br>to the transmit history list (the transmit history list has a vacant element). |                                                                                                                                                        |                                                                                                                                   |                                                                                                       |                                                                                                                 |                                                                                             |                                                                               |                                               |  |  |

| TOVF <sup>Note 2</sup><br>0           | message                                                                                                                                                                                                                                                                                                             | e buffers to w                                                                                                                                         |                                                                                                                                   |                                                                                                       | st has a vaca                                                                                                   | int element).                                                                               |                                                                               |                                               |  |  |

|                                       | Message<br>to the tra<br>At least<br>COTGPT<br>overwritt<br>stored at                                                                                                                                                                                                                                               | e buffers to w<br>unsmit history<br>7 entries hav<br>7). The first 6<br>en by newly<br>t position LOI                                                  | r list (the tran<br>e been store<br>6 entries are s<br>transmitted n<br>PT-1 when T                                               |                                                                                                       | ost processor<br>tored wherea<br>umber of time<br>to 1. As a co                                                 | serviced the<br>s the last en<br>es because a                                               | try might have<br>Il buffer numl                                              | e been<br>oers are                            |  |  |

| 0<br>1<br>Notes 1. The r<br>2. If all | message<br>to the tra<br>At least<br>COTGPT<br>overwritt<br>stored at<br>complete<br>ead value<br>the transm                                                                                                                                                                                                        | e buffers to w<br>insmit history<br>7 entries hav<br>7). The first 6<br>en by newly<br>t position LOI<br>ely recovered<br>of the TGP<br>hit history is | e list (the tran<br>e been store<br>c entries are s<br>transmitted n<br>PT-1 when T<br>l in the order<br>T0 to TGP<br>read by the | smit history li<br>d since the ho<br>sequentially s<br>nessages a n<br>OVF bit is se<br>that they wer | ost processor<br>tored wherea<br>umber of time<br>to 1. As a co<br>e received.<br>alid when th<br>register whil | serviced the<br>as the last en<br>es because a<br>onsequence r<br>ne THPM bi<br>le the TOVR | try might have<br>Il buffer numl<br>receptions ca<br>t = 1.<br>F bit is set ( | e been<br>bers are<br>nnot be<br>1), the THPM |  |  |

#### (11) UF0 INT status 0 register (UF0IS0)

This register indicates the interrupt source. If the contents of this register are changed, the EPCINT0B signal becomes active.

This register is read-only, in 8-bit units.

If an interrupt request (INTUSBF0) is generated from USBF, the FW must read this register to identify the interrupt source.

Each bit of this register is forcibly cleared to 0 when 0 is written to the corresponding bit of the UF0IC0 register.

Caution In the USBF, multiple interrupt sources, such as Bus Reset, Resume, and Short, are ORed internally and are issued as a single interrupt request (INTUSBF0). Therefore, in the case of the occurrence of multiple interrupt sources, they are ORed and issued as an INTUSBF0 interrupt request.

For example, if a Bus Reset interrupt source and Resume interrupt source occur, the two sources are ORed and an INTUSBF0 interrupt request is issued.

Under these conditions, if the Bus Reset interrupt source is cleared to 0 (UF0IC0.BUSRSTC = 0), the V850ES/JH3-E or V850ES/JJ3-E internal INTUSBF0 interrupt request may remain set to 1 since the Resume interrupt source will still remain. The new interrupt request flag (US0BIC.US0BIF), therefore, might not be set to 1.

In this case, after performing clear processing for each interrupt request with the INTUSBF0 interrupt servicing routine, confirm the flag status for the UF0IS0 and UF0IS1 registers again, and if there are any interrupt sources with flags set to 1, perform flag clearing (only the applicable bits need to be cleared (do not perform a batch clearing)).

|         | 7     |        | 6    | 5                                    | 4                                                   | 3                                                  | 2                                            | 1                                          | 0                         | Address                                | After reset |

|---------|-------|--------|------|--------------------------------------|-----------------------------------------------------|----------------------------------------------------|----------------------------------------------|--------------------------------------------|---------------------------|----------------------------------------|-------------|

| UF0IS0  | BUSR  | ST RSI | JSPD | 0                                    | SHORT                                               | DMAED                                              | SETRQ                                        | CLRRQ                                      | EPHALT                    | 00200020H                              | 00H         |

| Bit pos | ition | Bit n  | ame  |                                      |                                                     |                                                    |                                              | Function                                   |                           |                                        |             |

| 7       |       | BUSRS  | Τ    | 1: 1                                 | Bus Reset I                                         | that Bus Re<br>nas occurre<br>set status (         | ed (interrup                                 | t request is                               | generated)                | ).                                     |             |

| 6       |       | RSUSP  | D    | the UF<br>1: I                       | 0EPS1 reg<br>Resume or                              | jister by FV<br>Suspend s                          | <i>I</i> .<br>tatus has o                    | ccurred (in                                |                           | urred. Referenduest is generate        |             |

| 4       |       | SHORT  | -    | registe<br>full in t<br>1: 1<br>0: 1 | er and that t<br>he DMA m<br>JSBSPnB s<br>JSBSPnB s | the USBSP<br>ode.<br>signal is act<br>signal is no | nB signal (<br>tive (interru<br>t active (de | n = 2, 4) is<br>pt request<br>fault value) | active. It is is generate | UF0BO1 or UF<br>valid only when<br>d). | the FIFO is |

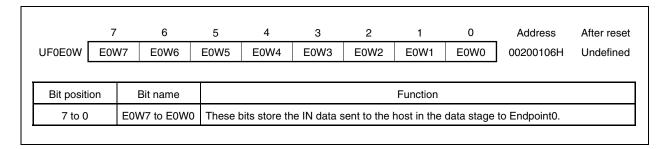

#### (4) UF0 EP0 write register (UF0E0W)

The UF0E0W register is a 64-byte FIFO that stores the IN data (passes it to SIE) sent to the host in the data stage to Endpoint0.

This register is write-only, in 8-bit units. When this register is read, 00H is read.

The hardware transmits data to the USB bus in synchronization with an IN token only when the EPONKW bit of the UF0E0N register is set to 1 (when NAK is not transmitted). When data is transmitted and when the host correctly receives the data, the EPONKW bit of the UF0E0N register is automatically cleared to 0 by hardware. A short packet is transmitted when data is written to the UF0E0W register and the E0DED bit of the UF0END register is set to 1 (EPOW bit of the UF0EPS0 register = 1 (data exists)). A Null packet is transmitted when the UF0E0W register is cleared and the E0DED bit of the UF0DEND register is set to 1 (EPOW bit of the UF0EDD bit of the UF0EDD register = 1 (data exists)).

The UF0E0W register is cleared to 0 when the next SETUP token is received while transmission has not been completed yet. If the stage of control transfer (read) changes to the status stage while ACK has not been correctly received in the data stage, the UF0E0W register is automatically cleared to 0. At the same time, it is also cleared to 0 if the EP0NKW bit of the UF0E0N register is 1.

If the UF0E0W register is read while no data is in it, 00H is read.

The operation of the UF0E0W register is illustrated below.

#### (2) RPKT: Receive packet counter

Access This register can be read and written in 32-bit units.

Address 002E 0144H

Default value 0000 0000H. This register is cleared to its default value by all types of resets.

| 31           | 30     | 29     | 28      | 27     | 26     | 25     | 24     |

|--------------|--------|--------|---------|--------|--------|--------|--------|

| RPKT31       | RPKT30 | RPKT29 | RPKT28  | RPKT27 | RPKT26 | RPKT25 | RPKT24 |

| R/W          | R/W    | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    |

| 23           | 22     | 21     | 20      | 19     | 18     | 17     | 16     |

| RPKT23       | RPKT22 | RPKT21 | RPKT20  | RPKT19 | RPKT18 | RPKT1  | RPKT16 |

| R/W          | R/W    | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    |

| 15           | 14     | 13     | 12      | 11     | 10     | 9      | 8      |

| RPKT15       | RPKT14 | RPKT13 | RPKT12  | RPKT11 | RPKT10 | RPKT9  | RPKT8  |

| R/W          | R/W    | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    |

| 7            | 6      | 5      | 4       | 3      | 2      | 1      | 0      |

| <b>BPKT7</b> |        |        | DDI/T ( | DDI/TO | DDI/TO | DDI/T4 | DDI/TO |

|              | RPKT6  | RPKT5  | RPKT4   | RPKT3  | RPKT2  | RPKT1  | RPKT0  |

| Bit     | Name       | Description                                                                                                                                                                    |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 0 | RPKT[31:0] | This counter is incremented when any packet, including packets in which an error has occurred, all unicast packets, all multicast packets, and broadcast packets, is received. |

#### (2) Procedure for transmitting or receiving a serial management frame

Serial management frames are transmitted or received as follows.

First, the MIND.SCANA bit is checked to see whether the SCAN command is under execution.

If not, the MIND.BUSY bit is checked to see whether the serial management frame is being accessed. If the BUSY bit is 1, the Ethernet controller waits until it is cleared to 0. On the other hand, while the SCAN command is being executed, the MCMD.SCANC bit is cleared to 0 and then the Ethernet controller waits until the BUSY bit is cleared to 0.

Next, the address of the external PHY device to which the frame is to be transmitted and the address of a register in the PHY device are set to the MADR.FIAD and RGAD bits, respectively.

When a write access is to be made, writing is started by writing data to the MWTD.CTLD bits.

The BUSY bit is set to 1 when data has been written to the MWDT register and cleared to 0 when writing is complete.

A read access is started by writing 1 to the MCMD.RSTAT bit. When the RSTAT bit is set to 1, the BUSY bit is set to 1. The BUSY bit is cleared to 0 after completion of reading. The host system can obtain the data of the PHY register by confirming that the BUSY bit is 0 and then reading the MRDD.PRSD bit.

To execute the SCAN command, set the MCMD.SCANC bit to 1. When this bit has been set to 1, reading is repeatedly executed. The MIND.SCANA bit is set to 1 while the SCAN command is being executed. The MIND.NVALID bit is set to 1 until the first read access is completed after the SCAN command has been executed. The MIND.BUSY bit is set to 1 when the SCAN command is executed. If the SCAN command is disabled (by clearing the MCMD.SCANC bit to 0), the MIND.BUSY bit is cleared to 0 after the current read access is completed.

How reception works is described below using an example of an actual descriptor chain.

After the RXS bit of the core function setting register (ETHMODE) is set to 1 by software, the first descriptor is read from the address indicated by the reception descriptor pointer (RXDP) (0028 0000H), and the reception descriptor is analyzed.

The first buffer address pointer (0028 1000H) is set as the DMA transfer start address and the reception data in the FIFO is transferred to buffer A.

When buffer A becomes full upon subsequent receptions, the next descriptor (0028 0008H) is read, the buffer address pointer (0028 1800H) is set as the DMA start address, and the reception data in the FIFO is transferred to buffer C.

In the final reception, the E and U bits of the descriptor are set to 1, and the number of data bytes transferred is written back to the descriptor's size field.

Once all the packet data has been transferred, the U and S bits of the first descriptor are set to 1, and the reception status information is written back to the status (A) field.

#### (7) External DMA request enable register (EXDRQEN)

The EXDRQEN register sets the DMA request to each DMA channel when connecting the external USB device by using the  $\overline{\text{UDMARQm}}/\overline{\text{UDMAAKm}}$  pin (m = 0, 1).

This register can be read or written in 8-bit units.

Reset sets This register to 00H.

|             | After reset: 00H                                                                                                                                                                                                          | R/W Address                                          | : FFFFF60    | ЭН        |               |           |           |          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|-----------|---------------|-----------|-----------|----------|

|             | _                                                                                                                                                                                                                         |                                                      |              | 0         |               |           | •         |          |

| EVD         | ROEN ROJEXIE                                                                                                                                                                                                              | 6 5<br>RQ2EX1E RQ1EX1I                               |              | 3         |               |           |           |          |

| EXD         | NOEN NOSENTE                                                                                                                                                                                                              |                                                      |              |           |               |           | UEXUE     |          |

|             | RQnEX1E                                                                                                                                                                                                                   | Ass                                                  | ignment of D | MA channe | el n (n = 0 t | o 3)      |           |          |

|             | 0                                                                                                                                                                                                                         | Does not assign D                                    | •            |           |               | ,<br>     |           |          |

|             | 1                                                                                                                                                                                                                         | Assigns DMA chan                                     |              |           |               |           |           |          |

|             |                                                                                                                                                                                                                           | Accigno Divix onan                                   |              |           | www.compil    | ·         |           |          |

|             | RQnEX0E                                                                                                                                                                                                                   | Ass                                                  | ignment of D | MA channe | el n (n = 0 t | o 3)      |           |          |

|             | 0                                                                                                                                                                                                                         | Does not assign DMA channel n to UDMARQ0/UDMAAK0 pin |              |           |               |           |           |          |

|             | 1                                                                                                                                                                                                                         | Assigns DMA chan                                     | nel n to UDN | IARQ0/UD  | MAAK0 pir     | l         |           |          |

| Cautions 1. | • •                                                                                                                                                                                                                       | iple DMA channe<br>RQ2EX1E, RQ1EX<br>s prohibited).  |              |           |               |           |           | <u> </u> |

| 2.          | <ul> <li>Assigning multiple DMA channels to the UDMARQ0/UDMAAK0 pin is prohibited (setting<br/>the RQ3EX0E, RQ2EX0E, RQ1EX0E, and RQ0EX0E bits to the UDMARQ0/UDMAAK0 pin at<br/>the same time is prohibited).</li> </ul> |                                                      |              |           |               |           |           |          |

| 3.          | Assigning both the UDMARQ1/UDMAAK1 pin and the UDMARQ0/UDMAAK0 pin to the same DMA channel is prohibited (setting the RQ3EX1E and RQ3EX0E, RQ2EX1E and                                                                    |                                                      |              |           |               | to the    |           |          |

|             |                                                                                                                                                                                                                           |                                                      |              |           |               | and       |           |          |

|             | RQ2EX0E, RQ1EX1E and RQ1EX0E, and RQ0EX1E and RQ0EX0E bits respectively at the                                                                                                                                            |                                                      |              |           |               |           | ly at the |          |

|             | same time is pro                                                                                                                                                                                                          | phibited).                                           |              |           |               |           |           |          |

| 4.          | When using a D                                                                                                                                                                                                            | •                                                    |              |           | •             | •         |           | •        |

|             |                                                                                                                                                                                                                           | 5-IFCn0 bit to 000                                   | •••          |           | •             |           | • •       | 1-       |

|             | For details, see 2                                                                                                                                                                                                        | 24.3 (6) DMA trigg                                   | ger factor r | egisters  | 0 to 3 (DT    | FR0 to DT | FR3).     |          |

#### (b) Repeatedly execute setting INITn bit until transfer is forcibly terminated correctly

- <1> Suppress a request from the DMA request source of the channel to be forcibly terminated (stop operation of the on-chip peripheral I/O).

- <2> Check that the DMA transfer request of the channel to be forcibly terminated is not held pending, by using the DTFRn.DFn bit. If a DMA transfer request is held pending, wait until execution of the pending request is completed.

- <3> When it has been confirmed that the DMA request of the channel to be forcibly terminated is not held pending, clear the Enn bit to 0.

- <4> Again, clear the Enn bit of the channel to be forcibly terminated. If the target of transfer for the channel to be forcibly terminated (transfer source/destination) is the internal RAM, execute this operation once more.

- <5> Copy the initial number of transfers of the channel to be forcibly terminated to a general-purpose register.

- <6> Set the INITn bit of the channel to be forcibly terminated to 1.

- <7> Read the value of the DBCn register of the channel to be forcibly terminated, and compare it with the value copied in <5>. If the two values do not match, repeat operations <6> and <7>.

- **Remarks 1.** When the value of the DBCn register is read in <7>, the initial number of transfers is read if forced termination has been correctly completed. If not, the remaining number of transfers is read.

- **2.** Note that method (b) may take a long time if the application frequently uses DMA transfer for a channel other than the DMA channel to be forcibly terminated.

#### (4) Procedure of temporarily stopping DMA transfer (clearing Enn bit)

Stop and resume the DMA transfer under execution using the following procedure.

- <1> Suppress a transfer request from the DMA request source (stop the operation of the on-chip peripheral I/O).

- <2> Check the DMA transfer request is not held pending, by using the DFn bit (check if the DFn bit = 0). If a request is pending, wait until execution of the pending DMA transfer request is completed.

- <3> If it has been confirmed that no DMA transfer request is held pending, clear the Enn bit to 0 (this operation stops DMA transfer).

- <4> Set the Enn bit to 1 to resume DMA transfer.

- <5> Resume the operation of the DMA request source that has been stopped (start the operation of the on-chip peripheral I/O).

#### (5) Memory boundary

The operation is not guaranteed if the address of the transfer source or destination exceeds the area of the DMA target (external memory, internal RAM, or on-chip peripheral I/O) during DMA transfer.

#### (6) Transferring misaligned data

DMA transfer of misaligned data with a 16-bit bus width is not supported.

If an odd address is specified as the transfer source or destination, the least significant bit of the address is forcibly assumed to be 0.

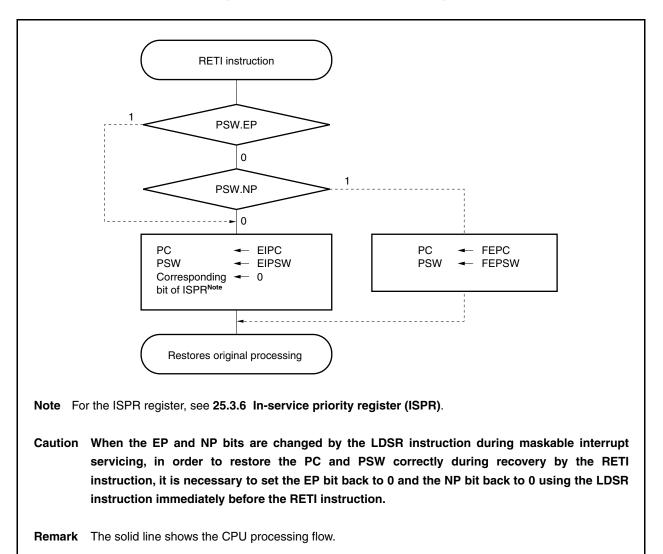

#### 25.3.2 Restore

Recovery from maskable interrupt servicing is carried out by the RETI instruction.

When the RETI instruction is executed, the CPU performs the following processing, and transfers control to the address of the restored PC.

<1> Loads the restored PC and PSW from EIPC and EIPSW because the PSW.EP bit is 0 and the PSW.NP bit is 0.

<2> Transfers control back to the address of the restored PC and PSW.

The processing of the RETI instruction is shown below.

| Setting of STOP Mode        |                    | Operating Status                                                                                                                                                |                                                                                  |  |  |  |

|-----------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| Item                        |                    | When Subclock Is Not Used                                                                                                                                       | When Subclock Is Used                                                            |  |  |  |

| Main clock oscilla          | ator (fx)          | Stops oscillation                                                                                                                                               |                                                                                  |  |  |  |

| Subclock oscillate          | or (fxt)           | _                                                                                                                                                               | Oscillation enabled                                                              |  |  |  |

| Internal oscillator         | (f <sub>R</sub> )  | Oscillation enabled                                                                                                                                             |                                                                                  |  |  |  |

| PLL                         |                    | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

| CPU                         |                    | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

| DMA controller              |                    | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

| Interrupt controlle         | er                 | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

| Timer                       | TAA0 to TAA5       | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

|                             | TAB0, TAB1         | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

|                             | TMM0 to TMM3       | Operable when $f_{\text{R}}/8$ is selected as the count clock                                                                                                   | Operable when $f_{\text{P}}/8$ or $f_{\text{XT}}$ is selected as the count clock |  |  |  |

|                             | ТМТО               | Stops operation                                                                                                                                                 |                                                                                  |  |  |  |

| Real-time counter (RTC)     |                    | Stops operation                                                                                                                                                 | Operable when $f_{XT}$ is selected as the count clock                            |  |  |  |