Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                             |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 50MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, Ethernet, I <sup>2</sup> C, UART/USART, USB                            |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                |                                                                                      |

| RAM Size                   | 76K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3784gj-gae-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (3) Port DH mode control register (PMCDH)

|          | -Е        |                                          |                                          |              |          |             |        |        |  |

|----------|-----------|------------------------------------------|------------------------------------------|--------------|----------|-------------|--------|--------|--|

| After re | eset: 00H | R/W                                      | Address: F                               | FFFF046      | ł        |             |        |        |  |

|          | 7         | 6                                        | 5                                        | 4            | 3        | 2           | 1      | 0      |  |

| PMCDH    | 0         | 0                                        | PMCDH5                                   | PMCDH4       | PMCDH3   | PMCDH2      | PMCDH1 | PMCDH0 |  |

|          | PMCDH5    |                                          | Spec                                     | ification of | PDH5 pin | operation r | node   |        |  |

|          | 0         | I/O port                                 |                                          |              |          |             |        |        |  |

|          | 1         |                                          | ut/SCKF4 I/                              | 0            |          |             |        |        |  |

|          | PMCDH4    |                                          | Spec                                     | ification of | PDH4 pin | operation r | node   |        |  |

|          | 0         | I/O port                                 |                                          |              |          |             |        |        |  |

|          | 1         | A20 outp                                 | A20 output/SOF4 output/RXDB0 input       |              |          |             |        |        |  |

|          | PMCDH3    |                                          | Specification of PDH3 pin operation mode |              |          |             |        |        |  |

|          | 0         | I/O port                                 |                                          |              |          |             |        |        |  |

|          | 1         | A19 outp                                 | ut/SIF4 inpu                             | ut/TXDB0 c   | output   |             |        |        |  |

|          | PMCDH2    | Specification of PDH2 pin operation mode |                                          |              |          |             |        |        |  |

|          | 0         | I/O port                                 |                                          |              |          |             |        |        |  |

|          | 1         | A18 outp                                 | ut/SCKE1 I/                              | 0            |          |             |        |        |  |

|          | PMCDH1    |                                          | Spec                                     | ification of | PDH1 pin | operation r | node   |        |  |

|          | 0         | I/O port                                 |                                          |              |          |             |        |        |  |

|          | 1         | A17 outp                                 | ut/SOE1 ou                               | tput         |          |             |        |        |  |

|          | PMCDH0    |                                          | Spec                                     | ification of | PDH0 pin | operation r | node   |        |  |

|          | 0         | I/O port                                 |                                          |              |          |             |        |        |  |

|          | 1         | A16 outp                                 | ut/SIE1 inpu                             | ut           |          |             |        |        |  |

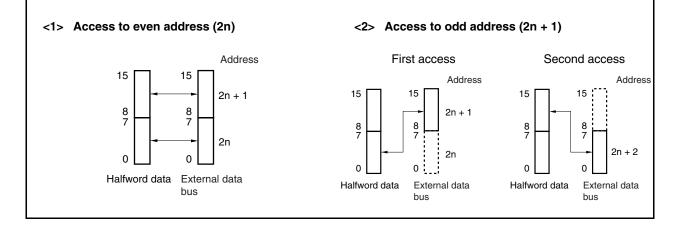

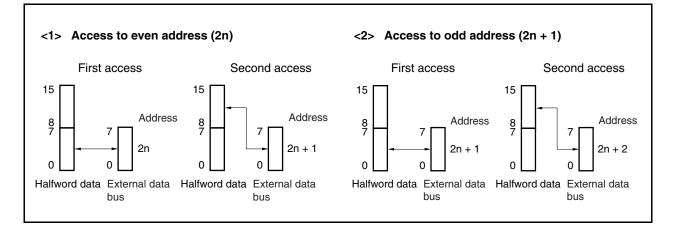

# (3) Halfword access (16 bits)

### (a) 16-bit data bus width

(b) 8-bit data bus width

**Remark** m = 0 to 3, n = 0, 1

#### (7) Notes on using encoder count function

#### (a) If compare match interrupt is not generated immediately after operation is started

If a value which is the same as that of the TT0TCW register is set to the TT0CCR0 or TT0CCR1 register and the counter operation is started when the TT0CTL2.TT0ECC bit = 0, and if the count value (TT0TCW) of the 16-bit counter matches the value of the CCRn buffer register immediately after the start of the operation, the match is masked and the compare match interrupt request signal (INTTT0CCn) is not generated (n = 0, 1). In addition, the 16-bit counter is not cleared to 0000H by setting the TT0CTL2.TT0ECM1 and TT0CTL2.TT0ECM0 bits.

| Count clock             |                |        |                                |

|-------------------------|----------------|--------|--------------------------------|

| TT0CE bit               |                |        |                                |

| Peripheral clock        |                |        |                                |

| Count<br>timing signal  |                |        |                                |

| Count<br>up/down signal | H = Count down |        | 16-bit counter is not cleared. |

| TT0CNT register         | FFFFH          | ттотси | ТТОТСИ – 1                     |

| TT0CCR1 register        |                | TTOTCW |                                |

| INTTT0CC1 signal        |                |        | Match does not occur.          |

|                         |                |        |                                |

(2/2) T

| HZA0DCTn                                                                                    | High-impedance output trigger bit                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                                                                                           | No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1 Pins are made to go into a high-impedance state by software and HZA0DCFn bit is set to 1. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| accordin<br>bit is inv<br>• The HZ<br>bit.<br>• The HZ                                      | ge indicating abnormality is input to the external pin (which is detected<br>ng to the setting of the HZA0DCNn and HZA0DCPn bits), the HZA0DCTn<br>valid even if it is set to 1.<br>A0DCTn bit is always 0 when it is read because it is a software-triggered<br>A0DCTn bit is invalid even if it is set to 1 when the HZA0DCEn bit = 0.<br>neously setting the HZA0DCTn and HZA0DCCn bits to 1 is prohibited.                                                            |  |  |  |  |

| HZA0DCCn                                                                                    | High-impedance output control clear bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0                                                                                           | No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1                                                                                           | Pins that have gone into a high-impedance state are output-enabled by software and the HZA0DCFn bit is cleared to 0.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| status o<br>If an ed<br>HZAOD<br>bit is inv<br>The HZ<br>The HZ                             | n function as output pins when the HZA0DCM bit = 0, regardless of the<br>f the external pin.<br>ge indicating abnormality is input to the external pin (which is set by the<br>CNn and HZA0DCPn bits) when the HZA0DCM bit = 1, the HZA0DCCn<br>ralid even if it is set to 1.<br>A0DCCn bit is always 0 when it is read.<br>A0DCCn bit is invalid even if it is set to 1 when the HZA0DCEn bit = 0.<br>neously setting the HZA0DCTn and HZA0DCCn bits to 1 is prohibited. |  |  |  |  |

| HZA0DCFn                                                                                    | High-impedance output status flag                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 0                                                                                           | Indicates that output of the pin is enabled.<br>• This bit is cleared to 0 when the HZA0DCEn bit = 0.<br>• This bit is cleared to 0 when the HZA0DCCn bit = 1.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 1                                                                                           | Indicates that the pin goes into a high-impedance state.<br>• This bit is set to 1 when the HZA0DCTn bit = 1.<br>• This bit is set to 1 when an edge indicating abnormality is input to the<br>external pin (which is detected according to the setting of the<br>HZA0DCNn and HZA0DCPn bits).                                                                                                                                                                            |  |  |  |  |

## (10) Standby mode

Because the A/D converter stops operating in the STOP mode, the conversion results are invalid, so power consumption can be reduced. Operations are resumed after the STOP mode is released, but the A/D conversion results after the STOP mode is released are invalid. When using the A/D converter after the STOP mode is released, clear the ADA0M0.ADA0CE bit to 0 before setting the STOP mode or after releasing the STOP mode, then set the ADA0CE bit to 1 after releasing the STOP mode.

In the IDLE1, IDLE2, or subclock operation mode, operation continues. To lower the power consumption, therefore, clear the ADA0M0.ADA0CE bit to 0. In the IDLE1 and IDLE2 modes, since the analog input voltage value cannot be retained, the A/D conversion results after the IDLE1 and IDLE2 modes are released are invalid. The results of conversions before the IDLE1 and IDLE2 modes were set are valid.

#### (11) High-speed conversion mode

In the high-speed conversion mode, rewriting the ADA0M0, ADA0M2, ADA0S, ADA0PFM, and ADA0PFT registers and trigger input during the stabilization time are prohibited.

## (12) A/D conversion time

The A/D conversion time is the total of the stabilization time, conversion time, wait time, and trigger response time (for details of these times, refer to Table 15-2 Conversion Time Selection in Normal Conversion Mode (ADA0HS1 Bit = 0) and Table 15-3 Conversion Time Selection in High-Speed Conversion Mode (ADA0HS1 Bit = 1)).

During A/D conversion in the normal conversion mode, if the ADA0M0, ADA0M2, ADA0S, ADA0PFM, and ADA0PFT registers are written or a trigger is input, reconversion is carried out. However, if the stabilization time end timing conflicts with writing to these registers, or if the stabilization time end timing conflicts with the trigger input, a stabilization time of 64 clocks is reinserted.

If a conflict occurs again with the reinserted stabilization time end timing, the stabilization time is reinserted. Therefore do not set the trigger input interval and control register write interval to 64 clocks or lower.

#### (13) Variation of A/D conversion results

The results of A/D conversion may vary due to a fluctuation in the supply voltage or the effect of noise. To reduce this variation, take countermeasures with the program such as averaging the A/D conversion results.

#### (14) A/D conversion result hysteresis characteristics

The successive comparison type A/D converter holds the analog input voltage in the internal sample & hold capacitor and then performs A/D conversion. After A/D conversion has finished, the analog input voltage remains in the internal sample & hold capacitor. As a result, the following phenomena may occur.

- When the same channel is used for A/D conversions, if the voltage is higher or lower than the previous A/D conversion, then hysteresis characteristics may appear in which the conversion result is affected by the previous value. Thus, even if the conversion is performed at the same potential, the result may vary.

- When switching the analog input channel, hysteresis characteristics may appear in which the conversion result is affected by the previous channel value. This is because one A/D converter is used for the A/D conversions. Thus, even if the conversion is performed at the same potential, the result may vary.

#### (2) UARTBn status register (UBnSTR)

The UBnSTR register indicates the transfer status and reception error contents while UARTBn is transmitting data. The status flag that indicates the transfer status during transmission indicates the data retention status of the transmit shift register and transmit data register (the UBnTX register in the single mode or transmit FIFO in the FIFO mode). The status flag that indicates a reception error holds its status until it is cleared to 0. This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

# Caution When the UBnCTL0.UBnPWR bit or UBnCTL0.UBnRXE bit is set to 0, or when 0 is written to the UBnSTR register, the UBnSTR.UBnOVF, UBnSTR.UBnPE, UBnSTR.UBnFE, and UBnSTR.UBnOVE bits are cleared to 0.

| After re            | set: 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W                                                                      | Address: I    | JB0STR I    | FFFFFB84H,      | UB1STR       | FFFFFBA4     | 1H         |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------|-------------|-----------------|--------------|--------------|------------|--|--|

|                     | <7>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                        | 5             | 4           | <3>             | <2>          | <1>          | <0>        |  |  |

| JBnSTR<br>n = 0, 1) | UBnTSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                        | 0             | 0           | UBnOVF          | UBnPE        | UBnFE        | UBnOVE     |  |  |

| 1 = 0, 1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |               |             |                 |              |              |            |  |  |

|                     | UBnTSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                          |               | Tr          | ansfer status   | flag         |              |            |  |  |

|                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>In sing</li> </ul>                                              | le mode (Ul   | BnFIC0.U    | BnMOD bit =     | = 0)         |              |            |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data to                                                                  | be transfe    | rred to the | e transmit sh   | ift register | and UBnT)    | X register |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | does n                                                                   | ot exist (cle | ared (0) v  | when UBnCT      | L0.UBnPV     | /R bit = 0 c | or         |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UBnCT                                                                    | L0.UBnTX      | E bit = 0). |                 |              |              |            |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>In FIFC</li> </ul>                                              | D mode (UE    | InFIC0.UE   | BnMOD bit =     | 1)           |              |            |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data to                                                                  | be transfe    | rred to the | e transmit shi  | ift register | and transm   | nit FIFO   |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | does n                                                                   | ot exist (cle | ared (0) v  | vhen UBnCT      | L0.UBnPW     | /R bit = 0 c | or         |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UBnCT                                                                    | L0.UBnTX      | E bit = 0). |                 |              |              |            |  |  |

|                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>In sing</li> </ul>                                              | le mode (Ul   | BnFIC0.U    | BnMOD bit =     | = 0)         |              |            |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data to                                                                  | be transfe    | rred to the | e transmit shi  | ift register | or UBnTX     | register   |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | exists (                                                                 | transmissic   | on in prog  | ress).          |              |              |            |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | In FIFC                                                                  | D mode (UE    | InFIC0.UE   | BnMOD bit =     | 1)           |              |            |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data to                                                                  | be transfe    | rred to the | e transmit shi  | ift register | and transm   | nit FIFO   |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | exists (                                                                 | transmissic   | on in prog  | ress).          | L            |              |            |  |  |

|                     | The value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e of the UE                                                              | 3nTSF bit is  | reflected   | after two pe    | riods of fxx | have elap    | sed, after |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |               |             | (register. Th   |              |              |            |  |  |

|                     | referenci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ng the UB                                                                | nTSF bit aft  | er transm   | it data has b   | een writter  | to the UB    | nTX        |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |               |             |                 |              |              |            |  |  |

|                     | UBnOVF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                          |               |             | Overflow fla    | ıg           |              |            |  |  |

|                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Overflow                                                                 | did not occ   | ur.         |                 |              |              |            |  |  |